DDR2时序测试规范V10.docx

DDR2时序测试规范V10.docx

- 文档编号:5127277

- 上传时间:2022-12-13

- 格式:DOCX

- 页数:20

- 大小:7.90MB

DDR2时序测试规范V10.docx

《DDR2时序测试规范V10.docx》由会员分享,可在线阅读,更多相关《DDR2时序测试规范V10.docx(20页珍藏版)》请在冰豆网上搜索。

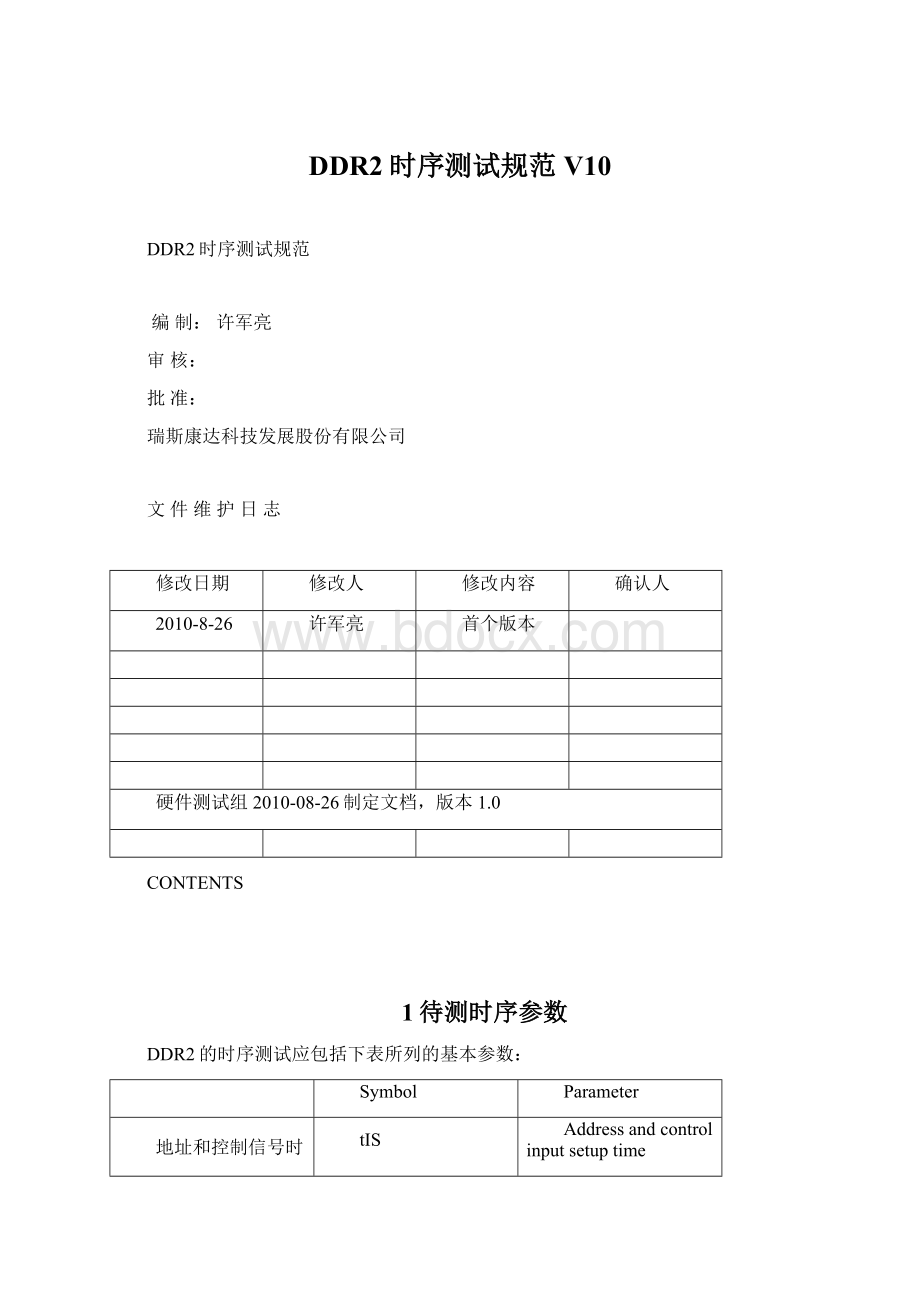

DDR2时序测试规范V10

DDR2时序测试规范

编制:

许军亮

审核:

批准:

瑞斯康达科技发展股份有限公司

文件维护日志

修改日期

修改人

修改内容

确认人

2010-8-26

许军亮

首个版本

硬件测试组2010-08-26制定文档,版本1.0

CONTENTS

1待测时序参数

DDR2的时序测试应包括下表所列的基本参数:

Symbol

Parameter

地址和控制信号时序

tIS

Addressandcontrolinputsetuptime

tIH

Addressandcontrolinputholdtime

写数据和DM信号时序

tDS

DQandDMinputsetuptime

tDH

DQandDMinputholdtime

tWPRE

DQSWritepreamble,写前导时间

tWPST

DQSWritepostamble,写后续时间

读数据时序

tDQSQ

DQS-DQskewforDQSandassociatedDQ

tQH

DQoutputholdtimefromDQS

tRPRE

DQSReadpreamble,读前导时间

tRPST

DQSReadpostamble,读后续时间

【备注】如果内存控制器(如CPU)的datasheet中对读数据时序有明确要求,读时序测试参考内存控制器的datasheet执行。

各参数的示意图如下:

下面分别说明这些参数的测试方法。

2地址和控制信号时序

包括tIS和tIH,定义如下:

上图中的各种逻辑电平定义如下:

【注释】

VIH(dc)输入高电平直流参数:

当信号向上穿越此阀值时,确保电平翻转到1。

是逻辑高电平的翻转阀值。

VIH(ac)输入高电平交流参数:

只有信号向上穿越此阀值后,输入的高电平信号才能保持一段时间,此时,介于VIH(dc)和VIH(ac)之间的振铃和毛刺才不会引起误触发。

VIL(dc)输入低电平直流参数:

当信号向下穿越此阀值时,确保电平翻转到0。

是逻辑低电平的翻转阀值。

VIL(ac)输入低电平交流参数:

只有信号向下穿越此阀值后,输入的低电平才能保持一段时间,此时,介于VIL(dc)和VIL(ac)之间的振铃和毛刺才不会引起误触发。

测试点:

地址和控制信号包括A0~A15、BA0~BA2、CS#、RAS#、CAS#、WE、CKE、ODT,对DDR2来说,这些都是输入信号,在DDR2芯片侧测试。

测试点的选取尽量靠近DDR2芯片输入管脚,测试时,根据测试需求可选取个别信号测试。

测试仪器:

1.地址和控制信号的时序是以差分时钟的交叉点为参考的,测试时需要使用示波器的3个模拟通道,分别连接CK、CK#和地址(或控制)信号,CK和CK#信号需要使用焊接式探头连接,以减少干扰。

2.以目前的测试条件,示波器需要使用Tek_DSA70804,被测地址(或控制)信号使用P7240单端探头,CK和CK#信号分别使用1个P7380A差分探头,差分探头的“+”端接CK或CK#,“-”端接地,连接方式如下图:

图1.先将探头的附件焊接在板上并固定好

图2.再将P7380A探头分别连接好

实测波形:

以低电平信号为例。

tIS:

tIH:

【注意】tIS和tIH是以CK上升沿与CK#下降沿的交叉点为参考的。

3DQ读写数据分离

由于DQ数据总线是双向的,所以测试DQ读写时序的前提是对读写数据进行分离,筛选出需要的读或写数据。

总体而言,有4种方法:

1.根据WE#信号——写数据出现前,WE#信号会被拉低来下发写命令,而下发读命令时,WE#信号是高电平。

2.根据DQS和DQ的时序关系——写操作DQS跳变点与DQ中心对齐,读操作DQS跳变点与DQ跳变沿对齐。

3.根据DQS的前导信号长度——写操作DQS前导信号长度大约为0.5tCK,读操作DQS前导信号长度大约为1tCK。

4.比较DQ信号波形峰峰值(或信号质量)——一般情况下,在内存控制器端测量时,写操作峰峰值高(或信号质量差),在内存芯片端测量时读操作峰峰值高(或信号质量差)。

【说明】由于DDR2的读写操作在不同的设计中存在差异,而且DDR2本身的工作状态比较复杂,所以在某个特定的设计中,上面的4种判断依据并不都是绝对符合的。

进行读写信号的分离需要根据实际情况,综合考虑,选择其中的一种或几种作为判断依据,并且尽量选择最简单有效的方法。

4写数据和DM信号时序

包括tDS、tDH、tWPRE和tWPST。

tDS和tDH的定义如下:

如果DDR2配置为DQS#不使能模式,仅用DQS单端信号采样,tDS和tDH的定义如下:

tWPRE的起始点和tWPST的结束点如下图所示:

测试点:

写数据DQ和数据屏蔽DM信号都在靠近DDR2芯片侧测试,并且尽量在DDR2芯片的BGA管脚下面测试。

DQ数据总线根据芯片型号不同有×4、×8、×16三种位宽,测试时,根据测试需求可选取个别信号进行测试。

测试仪器:

1.DQ和DM信号的时序是以差分DQS和DQS#的交叉点为参考的,测试时需要使用示波器的全部4个模拟通道,分别连接WE#、DQS、DQS#和DQ(或DM)信号,DQS和DQS#信号需要使用焊接式探头连接,以减少干扰。

【备注】如果芯片配置为不使能DQS#模式,DQ和DM的时序则以DQS的上下沿为参考。

这里以使能DQS#模式为例讲解。

2.以目前的测试条件,示波器需要使用Tek_DSA70804,WE#信号使用P6248差分探头(“-”端接地,当作单端探头使用),被测DQ(或DM)信号使用P7240单端探头,DQS和DQS#信号分别使用1个P7380A差分探头(“+”端接DQS或DQS#,“-”端接地)。

实测波形:

以高电平信号为例。

tDS:

tDH:

tWPRE:

tWPST:

5读数据时序

包括tDQSQ、tQH、tRPRE和tRPST。

测试点:

读数据信号都在靠近内存控制器(如CPU)侧测试,并且测试点尽量靠近内存控制器管脚。

DQ数据总线根据芯片型号不同有×4、×8、×16三种位宽,测试时,根据测试需求可选取个别信号进行测试。

测试仪器:

1.DQ信号的时序是以差分DQS和DQS#的交叉点为参考的,测试时需要使用示波器的全部4个模拟通道,分别连接WE#、DQS、DQS#和DQ(或DM)信号,DQS和DQS#信号需要使用焊接式探头连接,以减少干扰。

2.以目前的测试条件,示波器需要使用Tek_DSA70804,WE#信号使用P6248差分探头(“-”端接地,当作单端探头使用),被测DQ(或DM)信号使用P7240单端探头,DQS和DQS#信号分别使用1个P7380A差分探头(“+”端接DQS或DQS#,“-”端接地)。

实测波形:

以高电平信号为例。

tDQSQ:

【备注】tDQSQ表示读数据可以滞后采样点输出的最大时间。

当DQ滞后于采样点出现时,tDQSQ为正值;当DQ提前于采样点出现时,tDQSQ为负值。

这与通常的“建立时间”意义相似,但数值相反。

tQH:

tRPRE:

tRPST:

6时序修正

涉及参数:

tIS、tIH、tDS、tDH

上面测得的数据、地址和控制信号的建立/保持时间,需要与芯片datasheet中的参数要求做比较,以判定其时序符合性。

但是,datasheet中给出的建立保持时间与信号的斜率有关,均为在特定斜率下(单端信号1.0V/ns,差分信号2.0V/ns)的数值,在datasheet中一般叫做base值。

当实际信号的斜率不等于这个特定斜率时,JEDEC标准规定,实际的时序要求需要根据信号的斜率,在base值上加上一个修正值△t。

下表为JEDEC标准中对应DDR2-400/533的数据输入建立/保持时间修正表。

例如,DQS/DQS#差分信号的斜率为3.0V/ns,DQ的斜率为1.5V/ns,对应的修正值为△tDS=83ps,datasheet中给出的特定斜率下的base值为tDS(base)min=100ps,那么实际的时序要求tDS(totalsetuptime)min=tDS(base)min+△tDS=183ps。

斜率计算:

为了在上表中查到对应的修正值,首先需要得出相应信号的斜率。

JEDEC中规定了两种斜率计算方法,即直连斜率(nominalslewrate)和切线斜率(tangentslewrate),分别在不同数据波形时采用,计算方法如下图:

当信号波形在阴影标定区域内一直晚于直连斜率这根蓝色直线时,使用直连斜率计算并查找对应的建立/保持时间修正值;当信号波形在阴影标定区域内有任何一点落在直连斜率线之后时,则需要采用切线斜率计算并查找对应的建立/保持时间修正值。

上面的斜率计算方法对Addr/Command、DQ、CK/CK#差分、DQS/DQS#差分、以及DQS单端信号都适用。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- DDR2 时序 测试 规范 V10

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx

第九章(上)英国教育、法国教育、德国教育.ppt

第九章(上)英国教育、法国教育、德国教育.ppt