单片机学霸总结复习提纲.docx

单片机学霸总结复习提纲.docx

- 文档编号:5120465

- 上传时间:2022-12-13

- 格式:DOCX

- 页数:41

- 大小:510.91KB

单片机学霸总结复习提纲.docx

《单片机学霸总结复习提纲.docx》由会员分享,可在线阅读,更多相关《单片机学霸总结复习提纲.docx(41页珍藏版)》请在冰豆网上搜索。

单片机学霸总结复习提纲

1.MCS-51单片机芯片包含哪些主要功能?

8051单片机是个完整的单片微型计算机。

芯片内部包括下列主要功能部件:

1)8位CPU;

2)4KB的片内程序存储器ROM。

可寻址64KB程序存储器和64KB外部数据存储器;

3)128B内部RAM;

4)21个SFR;

5)4个8位并行I/O口(共32位I/O线);

6)一个全双工的异步串行口;

7)两个16位定时器/计数器;0

8)5个中断源,两个中断优先级;

9)内部时钟发生器。

2.MCS-51单片机的4个I/O口在使用上各有什么功能?

1)P0口:

8位双向三态端口,外接上拉电阻时可作为通用I/O口线,也可在总线外扩时用作数据总线及低8位地址总线。

2)P1口:

8位准双向I/O端口,作为通用I/O口。

3)P2口:

8位准双向I/O端口,可作为通用I/O口,也可在总线外扩时用作高8位地址总线。

4)P3口:

8位准双向I/O端口,可作为通用I/O口,除此之外,每个端口还有第二功能。

实际应用中常使用P3口的第二功能。

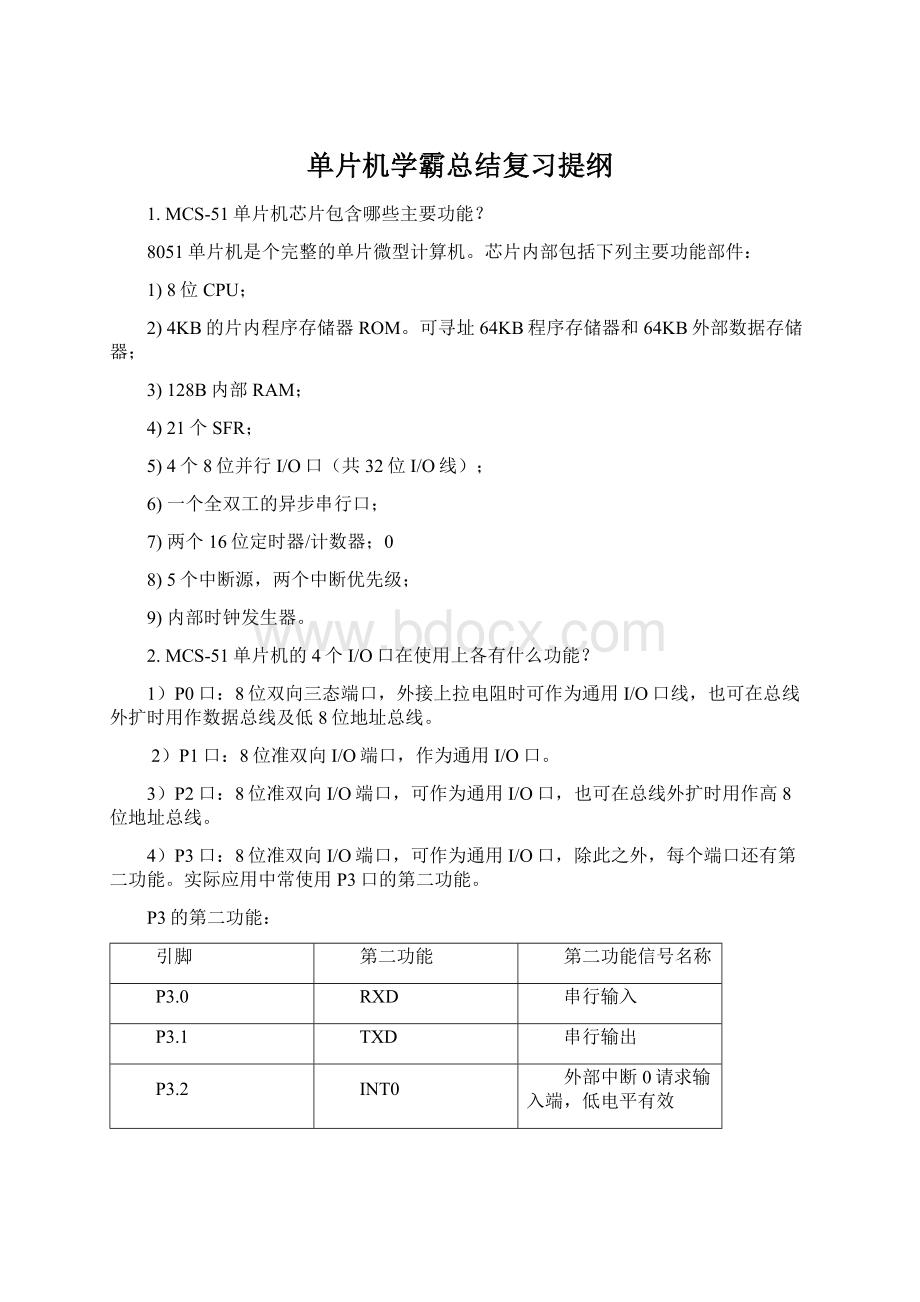

P3的第二功能:

引脚

第二功能

第二功能信号名称

P3.0

RXD

串行输入

P3.1

TXD

串行输出

P3.2

INT0

外部中断0请求输入端,低电平有效

P3.3

INT1

外部中断1请求输入端,低电平有效

P3.4

T0

定时/计数器0的计数脉冲输入端

P3.5

T1

定时/计数器1的计数脉冲输入端

P3.6

WR

外部RAM写选通信号输入端,低电平有效

P3.7

RD

外部RAM写选通信号输出端,低电平有效

【注】:

P0口必须接上拉电阻;

I/O口准双向:

MCS-51单片机I/O口做输入之前要先输出1.这种输入之前要先输出1的I/O口线叫做准双向I/O口,以区别真正的输入,输出的双向I/O口。

3.MCS-51单片机的存储器分为哪几个空间?

是描述各空间作用?

8051存储器包括程序存储器和数据存储器,从逻辑结构上看,可以分为三个不同的空间:

1)64KB片内片外统一编址的程序存储器地址空间,地址范围:

0000H~FFFFH,对于8051单片机,其中地址0000H~0FFFH范围为4KB的片内ROM地址空间,1000H~FFFFH为片外ROM地址空间;

2)256B的内部数据存储器地址空间,地址范围为00H~FFH,对于8051单片机,内部RAM分为两部分,其中地址范围00H~7FH(共128B单元)为内部静态RAM的地址空间,80H~FFH为特殊功能寄存器的地址空间,21个特殊功能寄存器离散地分布在这个区域;对于8052系列单片机还有地址范围为80H~FFH的高128B的静态RAM。

3)64KB的外部数据存储器地址空间:

地址范围为0000H~FFFFH,包括扩展I/O端口地址空间。

4.数据存储器

MCS-51基本型单片机内部数据存储器有256B的存储空间,地址为00H~FFH;外部数据存储器的地址空间最大为64KB,编址为0000H~FFFFH。

256B的内部存储器按功能划分为两部分:

地址为00H~7FH的低128B的基本RAM区和地址为80H~FFH的高128B的特殊功能寄存器(SFR)区

基本RAM区分为工作寄存器区,位寻址区,用户RAM区

工作寄存区(00H~1FH):

共分为4组,每组由8个工作寄存器,编号R0~R7

位寻址区(20H~2FH):

16个单元,既可以作为普通RAM单元使用,有可以对单元中的每一位进行位操作。

用户RAM区(30H~7FH):

用于存放随机数据及运算的中间结果。

程序状态字寄存器(PSW):

RS1,RS0(PSW.4,PSW.3):

工作寄存器组选择控制位。

可用软件对它们置1或清0,以选择当前工作寄存器的组号。

堆栈指针寄存器SP:

堆栈只允许在其一端进行数据插入和数据删除操作的线性表。

PUSH,数据写入堆栈称为插入运算(入栈);POP,从堆栈中读出数据称为删除运算(出栈)。

堆栈的特点:

后进先出LIFO(Last-InFirt-Out)。

堆栈有两种类型:

向上生长型,向下生长型。

进栈操作:

先SP加1,后写入数据

出栈操作:

先读出数据,后SP减1

MCS-51单片机复位后,SP的初值自动设为07H;

5.什么是振荡周期,时钟周期,机器周期和指令周期?

如何计算机器周期的确切时间?

1)振荡周期是指为单片机提供脉冲信号的振荡源的周期,是单片机最基本的时间单位。

通常由外接晶振与内部电路来提供振荡脉冲信号,其频率记为

,此频率的倒数即是振荡周期。

2)振荡脉冲经过二分频后就是单片机的时钟信号,时钟信号的周期称为时钟周期,又定义为状态,用S表示。

时钟周期是振荡周期的二倍。

3)机器周期是指令执行过程中完成某一个基本操作所需的时间。

一个机器周期等于12个振荡周期。

即

。

4)指令周期是指执行一条指令所需要的时间,根据指令不同,可包含1、2、4个机器周期。

常用符号说明:

寻址方式:

(1)立即寻址。

操作数直接在指令中给出,它可以是二进制、十进制、十六进制数,也可以是带单引号的字符,通常把这种操作数称为立即数,它的寻址范围就是指令本身所在的程序存储单元。

例:

MOVA,#25H;MOVDPTR,#1234H;

(2)直接寻址。

在指令中直接给出存放操作数的内存单元的地址。

寻址范围为:

内部RAM低128字节单元,特殊功能寄存器。

例:

MOVA,25H;

(3)寄存器寻址。

指令中给出的是操作数所在的寄存器。

寻址范围为:

4组工作寄存器(R0~R7),部分特殊功能寄存器,如A、B、DPTR。

例:

MOVA,R7;

(4)寄存器间接寻址。

存放操作数的内存单元的地址放在寄存器中,指令只给出寄存器(包括Ri和DPTR),寄存器名称前加“@”前缀标志。

寻址范围:

地址范围从00~FFH的全部内部RAM单元,包括堆栈区,但不包括特殊功能寄存器,以及地址范围从0000~FFFFH的全部片外RAM。

例:

MOVA,@R7;

(5)变址寻址。

将基址寄存器与变址寄存器的内容相加,结果作为操作数的地址。

变址寻址主要用于查表操作。

寻址范围:

64KB的程序存储空间。

例:

MOVCA,@A+DPTR;

(6)相对寻址。

指令中给出的操作数是程序相对转移的偏移量。

偏移量是一个带符号的单字节数,范围为-128~+127。

例:

SJMP50H;

(7)位寻址。

操作数是位地址。

寻址范围:

内部RAM位寻址区共128位(位地址:

00~7FH),11个特殊功能寄存器中的可寻址位(对于8051,有83位)。

MCS-51单片机指令系统

I.数据传送类(29条)

1.普通传送指令

MOV:

内部ROM;MOVC:

外部ROM;MOVX:

程序存储器。

1)片内数据存储器传送指令(16条)

(1)以A为目的操作数指令(4条)

MOVA,#data;

MOVA,direct;

MOVA,Rn;

MOVA,@Ri;

(2)以Rn为目的操作数的指令(3条)

MOVRn,#data;

MOVRn,direct;

MOVRn,A;

(3)以直接地址为目的操作数的指令(5条)

MOVdirect,#data;

MOVdirect,direct;

MOVdirect,A;

MOVdirect,Rn;

MOVdirect,@Ri;

(4)以寄存器间接寻址为目的操作数的指令(3条)

MOV@Ri,#data;

MOV@Ri,direct;

MOV@Ri,A;

(5)16位书库传送指令(1条)

MOVDPTR,#data16;

2)片外数据存储器传送指令(4条)

(1)使用DPTR进行间接寻址

MOVXA,@DPTR;A←((DPTR))

MOVX@DPTR,A;(DPTR)←A

(2)使用Ri进行间接寻址

MOVXA,@Ri;A←((Ri))

MOVX@Ri,A;(Ri)←A

例3.6要求把外部RAM60H单元中的数据8BH传送到内部RAM50H中,试编程。

解法1:

MOVR0,#60H;(R0)=60H

MOVXA,@R0;(A)=8BH

MOV50H,A;(50H)=8BH

解法2:

MOVDPTR,#0060H;(DPTR)=0060H

MOVXA,@DPTR;(A)=8BH

MOV50H,A;(50H)=8BH

3)程序存储器传送指令(2条)

MOVCA,@A+DPTR;A←((A)+(DPTR))

MOVCA,@A+PC;A←((A)+(PC))

例3.7已知程序存储器中以TAB为起点地址的空间存放着0~9的ASCII码,累加器A中存放着一个0~9之间的BCD码数据。

要求用查表的方法获得A中数据的ASCII码。

解法1:

MOVDPTR,#TAB

MOVCA,@A+DPTR

RET

TAB:

DB30H,31H,32H,33H,34H,35H,36H,

37H,38H,39H

解法2:

INCA

MOVCA,@A+PC

RET

TAB:

DB30H,31H,32H,33H,34H,35H,36H,

37H,38H,39H

2.数据交换指令(5条)

(1)整字节交换指令

源操作数与累加器A进行8位数据交换,共有3条指令:

XCHA,Rn;(A)←(Rn)

XCHA,direct;(A)←(direct)

XCHA,@Ri;(A)←((Ri))

(2)半字节交换指令

源操作数与累加器A进行低4位的半字节数据交换,

只有1条指令:

XCHDA,@Ri;(A)3~0((Ri))3~0

(3)累加器高低半字节交换指令

累加器A的高低半个字节进行数据交换,只有1条指令:

SWAPA;(A)3~0(A)7~4

3.堆栈操作指令

PUSHdirect;--SP+1,SP←(direct)

POPdirect;--direct←(SP),SP←(SP-1)

II.算术运算类指令

1.加法指令

1)不带进位的加法指令

ADDA,#data;A←(A)+data

ADDA,direct;A←(A)+(direct)

ADDA,Rn;A←(A)+(Rn)

ADDA,@Ri;A←(A)+((Ri))

加法运算的结果会影响程序状态字寄存器PSW,其中包括:

①如果运算结果的最高位第7位有进位,进位标志CY置“1”,反之,CY清“0”;

②如果运算结果的第3位有进位,辅助进位标志AC置“1”,反之,AC清“0”;

③如果运算结果的第6位有进位而第7位没有进位或者第7位有进位而第6位没有进位,则溢出标志OV置“1”(即OV=C7⊕C6),反之,OV清“0”;

④奇偶标志P随累加器A中1的个数的奇偶性而变化。

例3.10已知(A)=97H,(R0)=89H,

执行指令:

ADDA,R0

解:

10010111

+10001001

1←00100000

运算结果:

(A)=20H,CY=1,AC=1,OV=1,P=1。

若97H和89H是两个无符号数,则结果是正确的;

反之,若97H和89H是两个带符号数(即负数),则由于有溢出而表明相加结果是错误的,因为两个负数相加结果不可能是正数。

2)带进位的加法指令

ADDCA,#data;A←(A)+data+(CY)

ADDCA,direct;A←(A)+(direct)+(CY)

ADDCA,Rn;A←(A)+(Rn)+(CY)

ADDCA,@Ri;A←(A)+((Ri))+(CY)

例3.11已知当前(CY)=1,(A)=97H,(R0)=89H,

执行指令:

ADDCA,R0

解:

10010111

10001001

+1

1←00100001

运算结果:

(A)=21H,CY=1,AC=1,OV=1,P=0。

3)加1指令

INCA;A←(A)+1

INCRn;Rn←(Rn)+1

INCdirect;direct←(direct)+1

INC@Ri;(Ri)←((Ri))+1

INCDPTR;DPTR←(DPTR)+1

加1指令的操作不影响程序状态字PSW的状态,只有“INCA”指令可以影响奇偶标志位P

例3.13已知:

(A)=0FFH,(R3)=0FH,(30H)=0F0H,(R0)=40H,(40H)=00H,(DPTR)=1234H,

执行如下指令:

INCA

INCR3

INC30H

INC@R0

INCDPTR

其结果为:

(A)=00H,(R3)=10H,(30H)=0F1H,(R0)=40H,(40H)=01H,(DPTR)=1235H,PSW中仅P改变。

2.减法指令

1)带借位的减法指令

SUBBA,#data;A←(A)﹣data﹣(CY)

SUBBA,direct;A←(A)﹣(direct)﹣(CY)

SUBBA,Rn;A←(A)﹣(Rn)﹣(CY)

SUBBA,@Ri;A←(A)﹣((Ri))﹣(CY)

减法运算的结果会影响程序状态字寄存器PSW,其中包括:

①如果运算结果的最高位第7位有借位,则进位标志CY置“1”,反之,CY清“0”;

②如果运算结果的第3位有借位,则辅助进位标志AC置“1”,反之,AC清“0”;

③如果运算结果的第6位有借位而第7位没有借位或者第7位有借位而第6位没有借位,则溢出标志OV置“1”(即OV=C7⊕C6),反之,OV清“0”;

④奇偶标志P随累加器A中1的个数的奇偶性而变化。

例3.14已知(A)=0C9H,(R2)=54H,(CY)=1。

执行指令:

SUBBA,R2

解:

11001001

﹣01010100

1

01110100

运算结果:

(A)=74H,CY=0,AC=0,OV=1,P=0。

若C9H和54H是两个无符号数,则结果74H是正确的;反之,若为两个带符号数,则由于有溢出而表明结果是错误的,因为负数减正数其差不可能是正数。

2)减1指令组

4条减1指令:

DECA;A←(A)﹣1

DECRn;Rn←(Rn)﹣1

DECdirect;direct←(direct)﹣1

DEC@Ri;(Ri)←((Ri))﹣1

减1操作不影响PSW的状态,只有DECA影响奇偶标志位P

只有数据指针DPTR加1指令,而没有DPTR减1指令,如果要在程序设计中进行DPTR-1运算,只有通过编程完成

例3.3.15假如(A)=0FH,(R7)=19H,(30H)=00H,(R1)=40H,(40H)=0FFH,执行指令:

DECA

DECR7

DEC30H

DEC@R1

结果:

(A)=0EH,(R7)=18H,(30H)=0FFH,(R1)=40H,(40H)=0FEH。

PSW中仅P改变

3.乘法指令

MULAB

16位乘积的低位字节放在A中,高位字节放在B中

乘法运算影响PSW的状态:

进位标志CY总是被清“0”,溢出标志位状态与乘积有关

例3.3.16已知(A)=80H(即十进制数128),(B)=40H(即十进制数64),

执行指令:

MULAB

执行结果:

乘积为2000H(十进制数为8192),(A)=00H,(B)=20H,CY=0,OV=1

4.除法指令

DIVAB

被除数:

A除数:

B

指令执行后,商存于A中,余数存于B中

除法运算影响PSW的状态:

进位标志位CY总是被清“0”,溢出标志位OV状态则反映除数情况

例3.17已知(A)=80H(即十进制数128),(B)=40H(即十进制数64),

执行指令:

DIVAB

执行结果:

商为02H,余数为00H,(A)=02H,(B)=00H,CY=0,OV=0。

5.十进制调整指令:

用于对BCD码十进制数加法运算的结果进行修正。

DAA

十进制调整的修正方法:

(1)累加器低4位大于9或辅助进位位(AC)=1,则进行低4位加6修正

A←(A)+06H

(2)累加器高4位大于9或进位标志位(CY)=1,则进行高4位加6修正

A←(A)+60H

(3)累加器高4位为9、低4位大于9,则进行高4位和低4位分别加6修正

A←(A)+66H

例3.18试编写程序,实现93+59的加法运算,并分析执行过程。

解:

加法运算程序为:

MOVA,#93H

ADDA,#59H

DAA

程序执行的过程分析:

10010011

+01011001

11101100

01100110;加66H调整

101010010

最终结果为101010010(152)是正确的BCD码。

III.逻辑运算及移位类指令(24条)

1.逻辑与运算指令组

ANLA,#data;A←(A)∧data

ANLA,direct;A←(A)∧(direct)

ANLA,Rn;A←(A)∧(Rn)

ANLA,@Ri;A←(A)∧((Ri))

ANLdirect,#data;direct←(direct)∧data

ANLdirect,A;direct←(direct)∧(A)

例3.19已知(A)=86H,试分析下面指令执行的结果:

(1)ANLA,#0FFH;

(2)ANLA,#0F0H;

(3)ANLA,#0FH;

(4)ANLA,#1AH;

解:

(1)A=86H;

(2)A=80H;

(3)A=06H;

(4)A=02H。

由上例可知,逻辑与指令可用于将指定位清0,方法:

将要清零的位与0相与,把要保留的位与1相与。

2.逻辑或运算指令组

ORLA,#data;A←(A)∨data

ORLA,direct;A←(A)∨(direct)

ORLA,Rn;A←(A)∨(Rn)

ORLA,@Ri;A←(A)∨((Ri))

ORLdirect,#data;direct←(direct)∨data

ORLdirect,A;direct←(direct)∨(A)

例3.20已知(A)=86H,试分析下面指令执行的结果:

(1)ORLA,#0FFH;

(2)ORLA,#0F0H;

(3)ORLA,#0FH;

(4)ORLA,#1AH;

解:

(1)A=0FFH;

(2)A=0F6H;

(3)A=8FH;

(4)A=9EH。

由上例可知,逻辑或指令可用于将指定位置1,方法是将要置1的位与1相或,把要保留的位与0相或

3.逻辑异或运算指令组

XRLA,#data;A←(A)data

XRLA,direct;A←(A)(direct)

XRLA,Rn;A←(A)(Rn)

XRLA,@Ri;A←(A)((Ri))

XRLdirect,#data;direct←(direct)data

XRLdirect,A;direct←(direct)(A)

例3.3.20已知(A)=86H,试分析下面指令执行的结果:

(1)XRLA,#0FFH;

(2)XRLA,#0F0H;

(3)XRLA,#0FH;

(4)XRLA,#1AH;

解:

(1)A=79H;

(2)A=76H;

(3)A=89H;

(4)A=9CH。

4.累加器清“0”和取反指令组

累加器清“0”指令CLRA;A←0

累加器取反指令:

CPLA;A←(A)

5.移位指令组

(1)累加器循环左移RLA;

(2)累加器循环右移RRA;

(3)带进位循环左移RLCA;

(4)带进位循环右移RRCA;

例3.3.23

若累加器A中的内容为10001011B,CY=0,则执行RLCA指令后累加器A中的内容为00010110,CY=1

Ⅳ.控制转移类指令

1.无条件转移指令组:

不规则条件的程序转移称为无条件转移

(1)长转移指令LJMPaddr16;PC←addr16转移范围:

64KB

(2)绝对转移指令AJMPaddr11;PC←(PC)+2,PC10~0←addr11

指令功能:

构造程序转移目的地址,实现程序转移

以指令提供的11位地址去替换PC的低11位内容,形成新的PC值,即转移的目的地址.注意:

PC是下一条指令的PC值,是本条指令地址加2以后的PC值

例3.25程序存储器1000H地址单元有绝对转移指令:

1000HAJMP0750H

分析该指令的执行情况。

解:

指令AJMP0750H执行前,(PC)=1000H,取出该指令后PC当前值为1002H,指令执行的过程是将指令中的11位地址11101010000B送入PC的低11位,得新的PC值为0001011101010000B=1750H,所以指令AJMP0750H执行的结果就是转移到1750H处执行程序。

(3)短转移指令:

SJMPrel目的地址PC=(PC)+2+rel

例3.26在1000H地址上有指令1000HSJMP30H

则目的地址为1000H+02H+30H=1032H程序向前转移

如果指令为1000HSJMP0E7Hrel=0E7H,是负数19H的补码,

目的地址=1000H+02H-19H=0FE9H。

程序向后转移。

单片机程序设计时,通常用到一条SJMP指令:

SJMP$或HERE:

SJMPHERE

以$代表PC的当前值

(4)变址寻址转移指令JMP@A+DPTR;PC←(A)+(DPTR)

目的地址=(A)+(DPTR)

例3.28设累加器A中存放着待处理命令的编号(0~n;n≤85),程序存储器中存放着标号为PGTAB的转移表,则执行以下程序,将根据A内命令编号转向相应的命令处理程序。

PG:

MOVB,#3

MULAB;A←(A)*3

MOVDPTR,#PGTB;DPTR←转移表首址

JMP@A+DPTR

PGTB:

LJMPPG0;转向命令0处理入口

LJMPPG1;转向命令1处理入口

︴

LJMPPGn;转向命令n处理入口

2.条件转移指令组:

程序的转移时有条件的

(1).累加器判零转移指令

JZrel;若(A)=0,则PC←(PC)+2+rel。

若(A)≠0,则PC←(PC)+2

JNZrel;若(A)≠0,则PC←(PC)+2+rel。

若(A)=0,则PC←(PC)+2

例3.29编写程序将内部R

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 单片机 总结 复习 提纲

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx