基于IP核的DDS和FIR滤波器设计资料.docx

基于IP核的DDS和FIR滤波器设计资料.docx

- 文档编号:4992262

- 上传时间:2022-12-12

- 格式:DOCX

- 页数:17

- 大小:411.63KB

基于IP核的DDS和FIR滤波器设计资料.docx

《基于IP核的DDS和FIR滤波器设计资料.docx》由会员分享,可在线阅读,更多相关《基于IP核的DDS和FIR滤波器设计资料.docx(17页珍藏版)》请在冰豆网上搜索。

基于IP核的DDS和FIR滤波器设计资料

一、实验名称

基于IP核的DDS和FIR滤波器设计

二、实验目的和要求

目的要求:

1)掌握IP核的设计方法。

2)掌握和理解DDS的原理和波形产生方法。

3)理解掌握FIR滤波器设计方法。

4)掌握用VHDL硬件语言进行顶层文件设计。

5)掌握用Modelsim进行仿真操作。

三、实验内容和原理

1.DDS的原理

DDS称为直接数字频率合成器(DDFS),它具有输出相位连续、相对带宽较大、频率分辨率高、可编程、准确度和稳定度都比较高的优点。

它不仅能产生正弦、余弦、方波、三角波和锯齿波等波形,而且可以根据需要产生传统函数发生器所不能产生的任意波形。

DDS的基本原理是利用采样定理,根据相位间隔对正弦信号进行取样、量化、编码,然后储存在EPROM中构成一个正弦查询表,通过查表法产生波形。

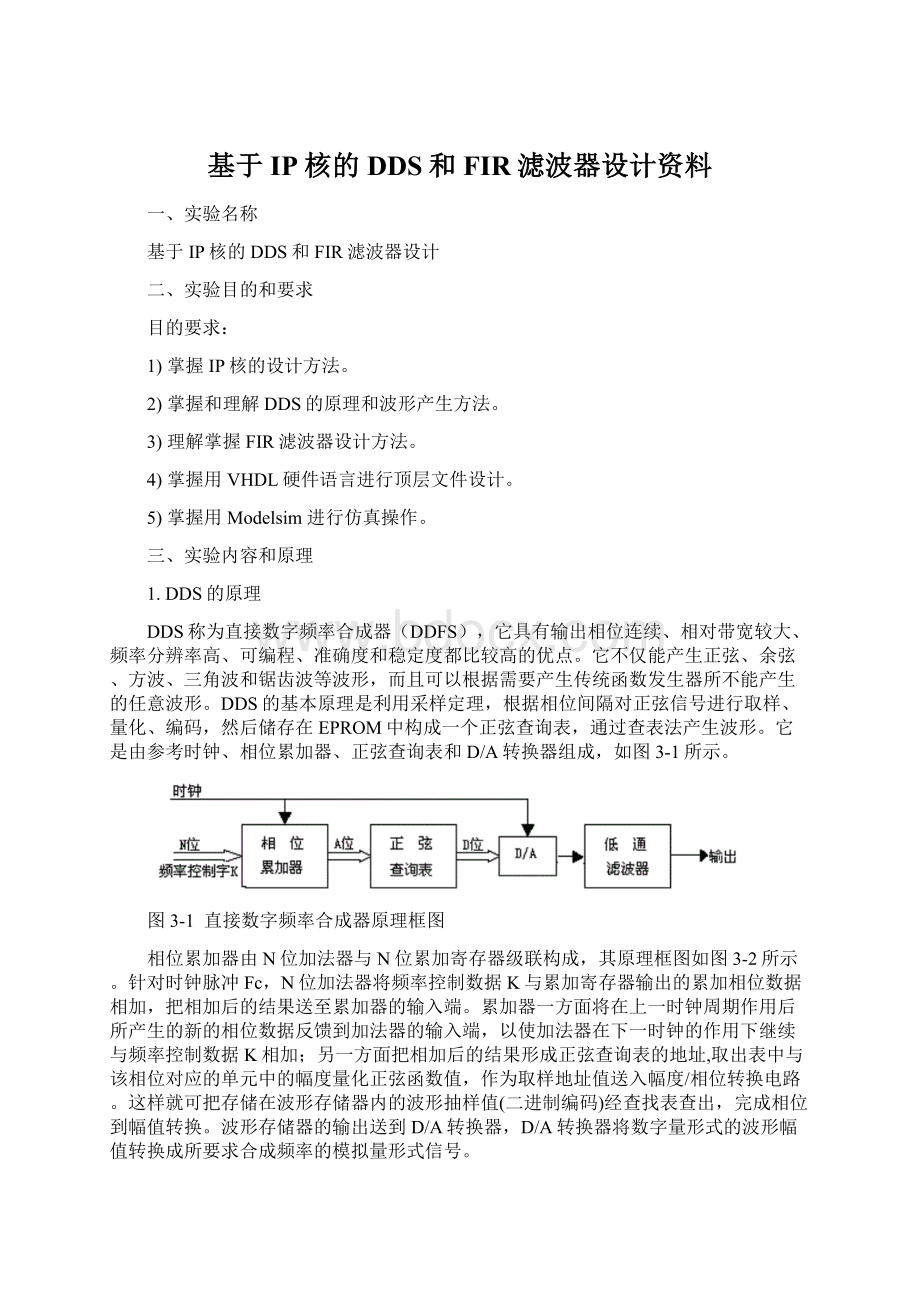

它是由参考时钟、相位累加器、正弦查询表和D/A转换器组成,如图3-1所示。

图3-1直接数字频率合成器原理框图

相位累加器由N位加法器与N位累加寄存器级联构成,其原理框图如图3-2所示。

针对时钟脉冲Fc,N位加法器将频率控制数据K与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加器的输入端。

累加器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据K相加;另一方面把相加后的结果形成正弦查询表的地址,取出表中与该相位对应的单元中的幅度量化正弦函数值,作为取样地址值送入幅度/相位转换电路。

这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。

波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

图3-2相位累加器原理框图

相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位。

当相位累加器加满量时就会产生一次溢出,溢出频率就是DDS输出的信号频率。

相位累加器的最大计数长度与正弦查询表中所存储的相位分隔点数相同,在取样频率(由参考时钟频率决定)不变的情况下,由于相位累加器的相位增量不同,将导致一周期内的取样点数不同,输出信号的频率也相应变化。

如果设定累加器的初始相位,则可以对输出信号进行相位控制。

由采样原理可知,如果使用两个相同的频率合成器,并使其参考时钟相同,同时设定相同的频率控制字、不同的初始相位,那么在原理上就可以实现输出两路具有一定相位差的同频信号。

也可以以正弦波为例说明DDS的基本原理,设正弦信号

表达式为

(1-1)

其中振幅为

频率为

,初始相位

。

实际应用中

与初始信号无关,若A=1,

则

相同的单位T内不同频率与相对应的相位增量不同,有

(1-2)

相位在时域内随时间均匀变化,因为DDS中相位累加是周期性的,因此相位与正弦信号线性特性一致的。

设K为频率控制字,

为时钟频率,N为相位累加器的长度,则合成的信号频率为:

(1-3)

改变频率控制字K输出频率随着变化,频率分辨率为

(1-4)

2.FIR滤波器

FIR(FiniteImpulseResponse)滤波器,即有限长单位冲激响应滤波器,它可以保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应式有限长的,因而滤波器是稳定的系统。

FIR滤波器具有以下特点:

(1)系统的单位冲激响应

在有限各n值处不为零。

(2)系统函数

在

处只有零点,即有限z平面只有零点,而全部极点都在

处(因果系统)。

(3)结构上是非递归结构,没有输出到输入的反馈。

FIR滤波器的基本结构有直接型、级联型、频率抽样型、快速卷积结构和线性相位结构,以下简要介绍其中几个基本结构。

直接型为最普遍的结构,根据差分方程可得出结构如下图所示:

图3-3FIR滤波器的直接型结构

级联型结构是将

分解成实系数二阶因子的乘积形式,如下图所示:

图3-4FIR滤波器级联型结构

线性相位型FIR滤波器单位响应

为实数,且满足偶对称或奇对称,对称中心在

处,具有严格的线性相位,结构如下图所示:

图3-5FIR滤波器线性相位型结构(N=5)

3.DDS和FIR滤波器IP核原理

IP核是一段具有特定电路功能的硬件描述语言程序,该程序与集成电路工艺无关,可移植到不同的半导体工艺中生产集成电路芯片。

由于具有复杂功能和商业价值的IP核一般具有知识产权,而它的本意也是知识产权核。

IP核有两种,与工艺无关的VHDL程序称为软核,具有特定电路功能的集成电路版图称为硬核,硬核一般不允许修改。

软IP设计周期短,设计投入少,为后续设计预留很大的发挥空间,增大了IP的灵活性和适应性。

XilinxISE中集成大量的IP库可供用户使用,在开发中无需了解硬件语言是如何实现的,提供了很大的方便性。

如下图所示为DDS的IP核符号文件。

图3-6DDS符号文件

其中CLK为DDS系统时钟输入信号,WE为写使能信号,DATA为输入数据,RDY表示有效数据输出,SINE和COSINE为输出波形,PHASE_OUT为相位输出值。

当WE有效时,在时钟作用下,通过改变输入数据DATA使输出正余弦频率发生改变。

FIR滤波器的IP核符号文件如下图所示:

FIR滤波器与DDS分别采用不同的时钟,FIR滤波器的系统时钟为36.864MHz,输入选择信号ND表示有新的数据到来。

FIR滤波器的滤波系数由MATLAB产生,在IP核参数修改时把coe文件加载到IP核中。

图3-7FIR滤波器IP核符号文件

四、实验环境(软、硬件环境,主要仪器设备)

软件环境:

ISEDesignSuite11.0,ModelsimSE6.5,MATLABR2012a

硬件环境:

PC机

操作系统:

WindowsXP

五、操作方法与实验步骤

1、DDSIP核设计

打开ISEDesignSuite11.0,新建工程命名为"dds_fir"。

在PreferredLanguage中择为VHDL,在新建的工程中右键NewSource选择IP(COREGenerator&ArchitectureWizard)并命名为dds,在弹出的DDSCompiler中修改系统时钟参数如下图所示:

图5-1DDSIP核的时钟设置

本次试验中DDS的系统时钟为2.304MHz,衰减范围为84dB,频率分辨率为10Hz,而后设置IP核的相位累加为可编程的。

如下图所示:

图5-2DDSIP核的相位累加设置

在OptionsPins中添加RDY信号管脚,如下图所示:

图5-3DDSIP核的可选信号添加

设置完成后点击Generate生成DDS的IP核,在工程中可以看到DDSIP核已添加到工程之中,并且该路径下生成有dds.xco文件。

2、FIR滤波器系数文件设计

MATLAB提供了功能齐全的滤波器设计,与信号处理交互式图形用户界面(InteractiveGraphiclaUserInterface),主要包括FDATool和SPTool两种交互工具。

其中FDATool主要用于数字滤波器的设计和分析,而SPTool不仅可以设计,分析滤波器,而且可以对信号进行时域和频域进行分析。

本次设计的硬件实现就是采用FDATool工具设计的滤波器。

打开MATLABR2012a软件,在MATLAB命令窗口中,执行“fdatool”命令,就会启动FDATool滤波器设计与分析工具,其图形界面如图5-4所示。

图5-4FDATool界面

Responsetype选择低通,选中FIR类型,再选择等波纹。

然后选择通带截止频率500kHz,阻带截止频率600kHz,通带最小衰减选择1db,阻带最小衰减选择80db,点击DESIGNFILTER按键,即可设计FIR滤波器了。

滤波器的频率响应曲线如图5-4中所示,滤波器的系数如下图所示。

图5-5超级文本工具查看生成的coe文件

3、FIR滤波器IP核设计

在新建的工程中右键NewSource选择IP(COREGenerator&ArchitectureWizard)并命名fir,在弹出的FIRCompiler中修改系统时钟参数如下图所示:

图5-6FIRIP核时钟设置

图5-7FIRIP核的控制管脚设置

设置完成后点击Generate生成DDS的IP核,在工程中可以看到DDSIP核已添加到工程之中,并且该路径下生成有dds.xco文件。

4、系统设计

系统总体原理框图如下,从图中可以看出,把DDS和FIR滤波器例化后就可以通过端口映射把模块相连,形成一个通过输入改变输入数据改变产生200kHz和900kHz的输出频率、然后进行滤波,只有200kHz的正弦波形输出。

图5-8系统设计原理

在新建的工程中右键NewSource选择VHDLModule,新建dds_fir.vhd文件。

鼠标点击dds和fir的IP核,显示高亮。

双击ViewHDLInstantiationTemplate,查看模板例化硬件语言。

把dds和fir的元件声明分别复制并粘贴在结构体中(begin之前),把管脚映射也复制粘贴在结构体中(begin之后)。

在实体中加入输入输出端口。

由于dds和fir滤波器有RDY和ND、SINE和din相连,所以要定义两个信号变量:

wire1和wire2,wire2为14位总线型变量,其中的端口映射关系参考实验代码。

由于输出数据仅需要14位,所以需加入以下代码:

process

begin

data_out<=wire3(29downto16);

endprocess;

代码编辑完成后保存、编译,如果没有错误开始进行仿真操作。

5、Modelsim仿真操作

在新建的工程中右键NewSource选择VHDLTestBench,新建dds_fir_tb.vhd文件。

在关联文件中选择dds_fir,生成TestBench后双击打开该文件。

把初始化的输入信号赋值为零,定义常量clk2304_period和clk36864_period分别为434ns和27ns。

图5-8添加激励代码

添加完成后在Project选项中打开DesignProperties,修改Simulator为Modelsim-SEMixed保存。

设置完成后,双击SimulatorBehavioralModel开始仿真。

把要查看的信号加入到波形显示窗口,这时会看到输出数据。

右键data_out选择format,选择analog,查看输出模拟波形。

从波形中可以看出,当输入数据"000101100011100011"(十六进制58E3)时,输出正弦波频率为200kHz,波形良好。

而输入数据"011001000000000000"(十六进制19000)时,输出没有波形,几乎被完全滤除。

具体TestBench代码和输出波形图参考第六部分与第七部分内容。

六、实验部分代码与截图

1、主代码

主代码dds_fir.vhd文件如下:

首先是库声明和实体定义,然后在结构体中进行元件声明和端口映射。

----------------------------------------------------------------------------------

--Company:

--Engineer:

--

--CreateDate:

15:

42:

3504/29/2014

--DesignName:

--ModuleName:

dds_fir-Behavioral

--ProjectName:

--TargetDevices:

--Toolversions:

--Description:

--

--Dependencies:

--

--Revision:

--Revision0.01-FileCreated

--AdditionalComments:

--

----------------------------------------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

--Uncommentthefollowinglibrarydeclarationifusing

--arithmeticfunctionswithSignedorUnsignedvalues

--useIEEE.NUMERIC_STD.ALL;

--Uncommentthefollowinglibrarydeclarationifinstantiating

--anyXilinxprimitivesinthiscode.

--libraryUNISIM;

--useUNISIM.VComponents.all;

entitydds_firis

port(clk2304:

instd_logic;

clk36864:

instd_logic;

we:

instd_logic;

data:

instd_logic_vector(17downto0);

data_out:

outstd_logic_vector(13downto0);

rfd:

outstd_logic;

rdy:

outstd_logic

);

enddds_fir;

architectureBehavioralofdds_firis

COMPONENTdds

PORT(

clk:

INSTD_LOGIC;

we:

INSTD_LOGIC;

data:

INSTD_LOGIC_VECTOR(17DOWNTO0);

rdy:

OUTSTD_LOGIC;

cosine:

OUTSTD_LOGIC_VECTOR(13DOWNTO0);

sine:

OUTSTD_LOGIC_VECTOR(13DOWNTO0);

phase_out:

OUTSTD_LOGIC_VECTOR(17DOWNTO0)

);

ENDCOMPONENT;

componentfir

port(

clk:

instd_logic;

nd:

instd_logic;

rfd:

outstd_logic;

rdy:

outstd_logic;

din:

instd_logic_vector(13downto0);

dout:

outstd_logic_vector(30downto0));

endcomponent;

signalwire1:

std_logic;

signalwire2:

std_logic_vector(13downto0);

signalwire3:

std_logic_vector(30downto0);

begin

inst1:

dds

PORTMAP(

clk=>clk2304,

we=>we,

data=>data,

rdy=>wire1,

--cosine=>cosine,

sine=>wire2

--phase_out=>phase_out

);

inst2:

fir

portmap(

clk=>clk36864,

nd=>wire1,

rfd=>rfd,

rdy=>rdy,

din=>wire2,

dout=>wire3

);

process

begin

data_out<=wire3(30downto17);

endprocess;

endBehavioral;

2、TestBench文件

在Stimulusprocess中加入了写使能信号,并给输入信号以激励,TestBench代码如下:

--------------------------------------------------------------------------------

LIBRARYieee;

USEieee.std_logic_1164.ALL;

--Uncommentthefollowinglibrarydeclarationifusing

--arithmeticfunctionswithSignedorUnsignedvalues

--USEieee.numeric_std.ALL;

ENTITYdds_fir_tbIS

ENDdds_fir_tb;

ARCHITECTUREbehaviorOFdds_fir_tbIS

--ComponentDeclarationfortheUnitUnderTest(UUT)

COMPONENTdds_fir

PORT(

clk2304:

INstd_logic;

clk36864:

INstd_logic;

we:

INstd_logic;

data:

INstd_logic_vector(17downto0);

data_out:

OUTstd_logic_vector(13downto0);

rfd:

OUTstd_logic;

rdy:

OUTstd_logic

);

ENDCOMPONENT;

--Inputs

signalclk2304:

std_logic:

='0';

signalclk36864:

std_logic:

='0';

signalwe:

std_logic:

='0';

signaldata:

std_logic_vector(17downto0):

=(others=>'0');

--Outputs

signaldata_out:

std_logic_vector(13downto0);

signalrfd:

std_logic;

signalrdy:

std_logic;

--Clockperioddefinitions

constantclk2304_period:

time:

=434ns;

constantclk36864_period:

time:

=27ns;

BEGIN

--InstantiatetheUnitUnderTest(UUT)

uut:

dds_firPORTMAP(

clk2304=>clk2304,

clk36864=>clk36864,

we=>we,

data=>data,

data_out=>data_out,

rfd=>rfd,

rdy=>rdy

);

--Clockprocessdefinitions

clk2304_process:

process

begin

clk2304<='0';

waitforclk2304_period/2;

clk2304<='1';

waitforclk2304_period/2;

endprocess;

clk36864_process:

process

begin

clk36864<='0';

waitforclk36864_period/2;

clk36864<='1';

waitforclk36864_period/2;

endprocess;

--Stimulusprocess

stim_proc:

process

begin

--holdresetstatefor100ns.

waitfor100ns;

waitforclk2304_period*10;

we<='1';

data<="000101100011100011";

waitforclk2304_period*500;

data<="011001000000000000";

waitforclk2304_period*500;

we<='0';

--insertstimulushere

wait;

endprocess;

END;

3、实验仿真结果图

(1)Modelsim仿真结果

如下图所示为Modelsim仿真实验结果,数据在没有转换格式前的截图。

图6-1Modelsim仿真数据结果

(2)Modelsim仿真输出模拟波形

如下图所示为Modelsim仿真结果为输出数据格式转换成模拟后的截图。

FIR滤波器输出为31位数据,顶层文件设计后的系统的输出是截取FIR输出数据的高14位,从波形来看输出波形和信号线wire3上波形并没有明显的区别。

所以,输出取高14位数据是可行的。

图6-2Modelsim仿真结果

七、实验结果与分析

从Modelsim仿真波形可以看出,当DDS输入数据"000101100011100011"(十六进制58E3)时,DDS输出端输出200kHz的正弦波,同时在信号线wire2也出现200kHz正弦波数据,当DDS输入数据"011001000000000000"(十六进制19000)时,DDS输出900kHz的波形数据,由于采样点原因,正弦波波形不平滑,同时信号线wire2也出现900kHz的正弦波数据,而经过FIR滤波器后900kHz的波形被滤除,输出波形数据为0。

FIR滤波器输出为31位数据,顶层文件设计后的系统的输出是截取FIR输出数据的高14位,从波形来看输出波形和信号线wire3上波形并没有明显的区别。

所以,输出取高14位数据是可行的。

在输入产生900kHz正弦波的数据之后一段时间wire3波形中有一些毛刺,而且波形毛刺时间间隔相差几乎相等,这说明FIR滤波器可能由于阶数过高的原因而产生噪声。

因此在设计过程中并不是阶数越高越好,设计中要充分考虑成本、噪声等问题。

八、体会、质疑、建议

通过本次实验基本掌握了ISE的使用方法,理解和掌握DDS和FIR滤波器的基本原理,掌握用ISE设计DDS和FIR滤波器IP核的设计方法以及编写简单代码进行简单的系统设计,掌握了TestBench如何添加激励文件以及用Modelsim进行仿真操作。

然而在本次实验中仍然存在一些问题:

首先,由于VHDL语言基础薄弱,在设计过程中不能熟练地编写代码,端口映射时发生了一下错误。

因此在以后的学习中理解VHDL语言的规则,熟练应用VHDL进行电路开发设计工作。

其次,由于软件安装复杂,安装过程不细心,Modelsim仿真出现许多错误,导致无法进行仿真和仿真结果出现错误,因此走了不少弯路。

所以在以后设计中,应该认真做好基础工作,为后续开发打下基础。

最

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基于 IP DDS FIR 滤波器 设计 资料

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

心力衰竭护理查房.pptx

心力衰竭护理查房.pptx