activehdl教程.docx

activehdl教程.docx

- 文档编号:4712226

- 上传时间:2022-12-07

- 格式:DOCX

- 页数:10

- 大小:390.58KB

activehdl教程.docx

《activehdl教程.docx》由会员分享,可在线阅读,更多相关《activehdl教程.docx(10页珍藏版)》请在冰豆网上搜索。

activehdl教程

ActiveHDL6.1使用介绍

作者:

邓旭

VHDL源代码编译

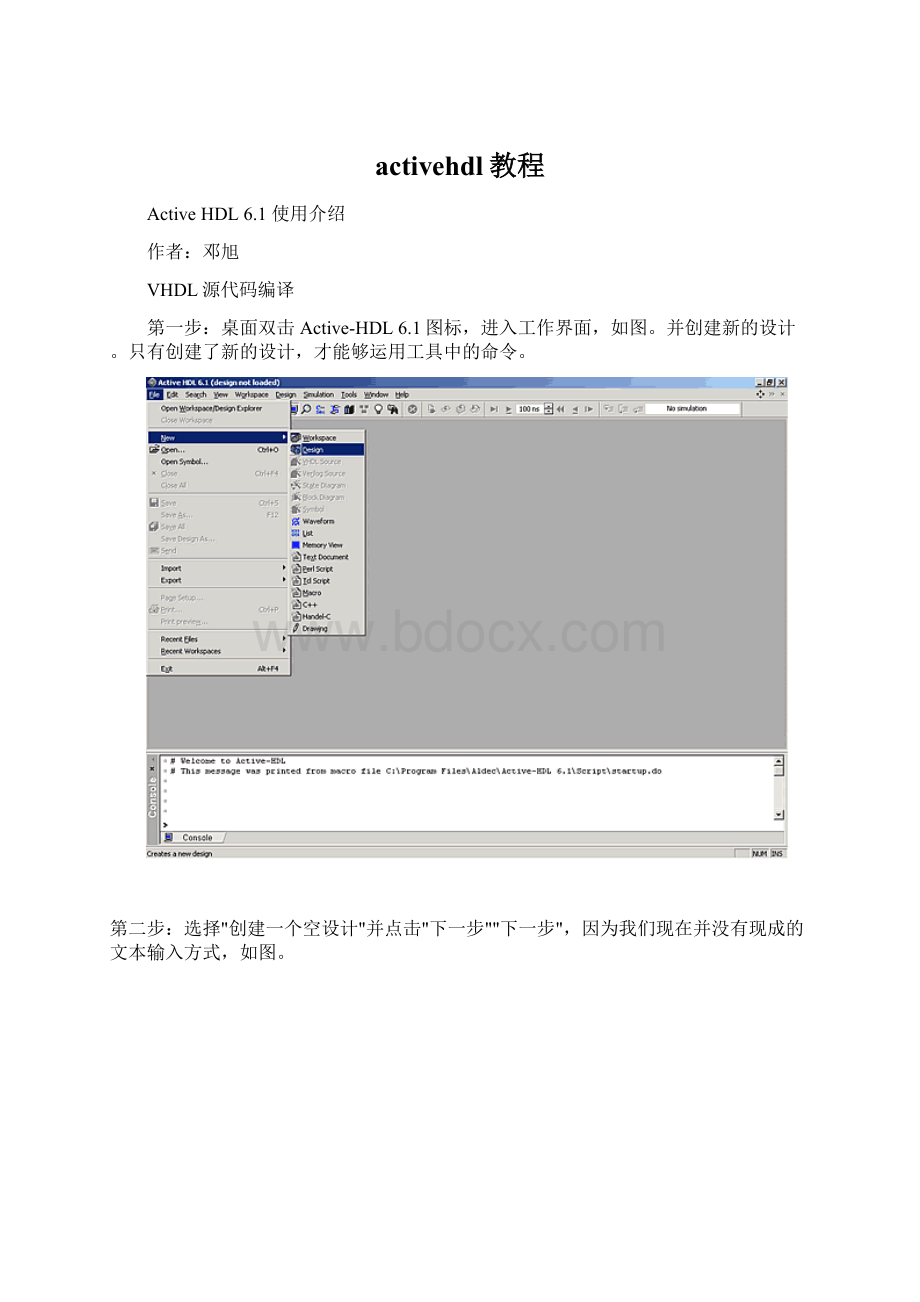

第一步:

桌面双击Active-HDL6.1图标,进入工作界面,如图。

并创建新的设计。

只有创建了新的设计,才能够运用工具中的命令。

第二步:

选择"创建一个空设计"并点击"下一步""下一步",因为我们现在并没有现成的文本输入方式,如图。

第三步:

设置设计名称和文件存放路径。

点击下"下一步"后点击"完成"。

第四步:

设置语言输入方式(选择VHDLSOURCE)并点击"下一步",如图:

第五步:

设置源文件的名称,实体,构造体名称。

注意:

实体和构造体名称应该不一样(这是VHDL输入方式的规定,如果实体和构造体的名称相同,在编译的时候会产生逻辑混乱,在仿真的时候,特别是进程中敏感量相同时候,功能仿真可能无法进行),这里我们设置为"user0"和"user1"以区别。

完成后点击"下一步"。

第六步:

输入端口名称(不仅需要设置端口的名称,还需要设置端口的特性),即把我们要完成的功能的这个程序看作是一个BLACKBOX,选择IN、OUT、BUFFER、INOUT。

这里只有MC、KC为输入,其余的为输出,分别设置为IN、OUT即可。

并点击"完成"。

第七步:

上面设置好的端口,这里的实体已经由ACTIVE-6.1软件自动生成,只需在构造体输入我们需要程序实现什么功能的算法就可以。

第八步:

把VHDL程序的实体和构造体部分写在对应的位置。

第九步:

编译。

在编译的过程中,就可以看到程序的算法有没有逻辑错误,或是否采用了不规则的语法,这是第一步检验程序的操作。

操作如下:

功能仿真

第一步:

将编译通过程序设为顶层。

操作如下:

第二步:

点击工具栏第四个图标,启动仿真窗口。

并在空白处单击右键。

第三步:

给信号加激励。

这里MC=2.048MHZ(占空比为1:

2),KC=8K(占空比为1:

512)。

对着信号单击右键。

第四步:

执行仿真命令SIMULATION-RUN,就可以看到程序的仿真波形。

接下来,就严格按照系统的要求,记录波形跳变的时间,仔细分析波形上反映的功能是否符合系统的要求。

如果不合乎系统的要求,就必须回到编写源代码这一步重新修改算法,直到波形反映出来的功能合乎我们的要求为止。

(并做出一些功能上的记录,把CPLD实现的功能反映给项目主管,商榷是否需要进一步提高精度,如果能实现功能,但精度不高,也需要回到源代码的编写这一步,重新修改算法,以求更为精确的算法)。

返回开发软件专栏

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- activehdl 教程

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx

人教版六年级语文下册口语交际.习作一优秀课件PPT格式课件下载.ppt

人教版六年级语文下册口语交际.习作一优秀课件PPT格式课件下载.ppt