HCPL电流检测.docx

HCPL电流检测.docx

- 文档编号:4562359

- 上传时间:2022-12-06

- 格式:DOCX

- 页数:8

- 大小:152.89KB

HCPL电流检测.docx

《HCPL电流检测.docx》由会员分享,可在线阅读,更多相关《HCPL电流检测.docx(8页珍藏版)》请在冰豆网上搜索。

HCPL电流检测

文件编号:

INVT0_013_0011_CBB_01

HCPL-7840电流检测

拟制:

时间:

2010-05-22

批准:

时间:

2010-05-22

文件评优级别:

□A优秀□B良好□C一般

1

芯片介绍

HCPL-7840是美国AGILENT公司推出的用于检测电机电流的线性光藕。

光藕的初级接收一组待测的模拟电压信号,次级输出一对差动的电压信号。

输入与输出之间在一定范围内是一种线性的当量关系,HCPL-7840增益偏差为5%,线性度为1%。

HCPL-7840包含有一个

A/D转换器,同时还匹配有一个D/A转换器,工作原理如图1所示,输入直流信号经过

调制器送至编码器量化、编码,在时钟信号控制下,以数码串的形式传送到发光二极管,驱动发光二极管发光。

由于电流强度不同,发光强度也不同,在解调端有一个光电管会检测出这一变化,将接收到的光信号转换成电信号,然后送到解码器和D/A转换器还原成模拟信号,经滤波后输出。

干扰信号因电流微弱不足以驱动发光二极管发光,因而在解调端没有对应的电信号输出,从而被抑制掉。

所以在输出端得到的只是放大了的有效的直流信号。

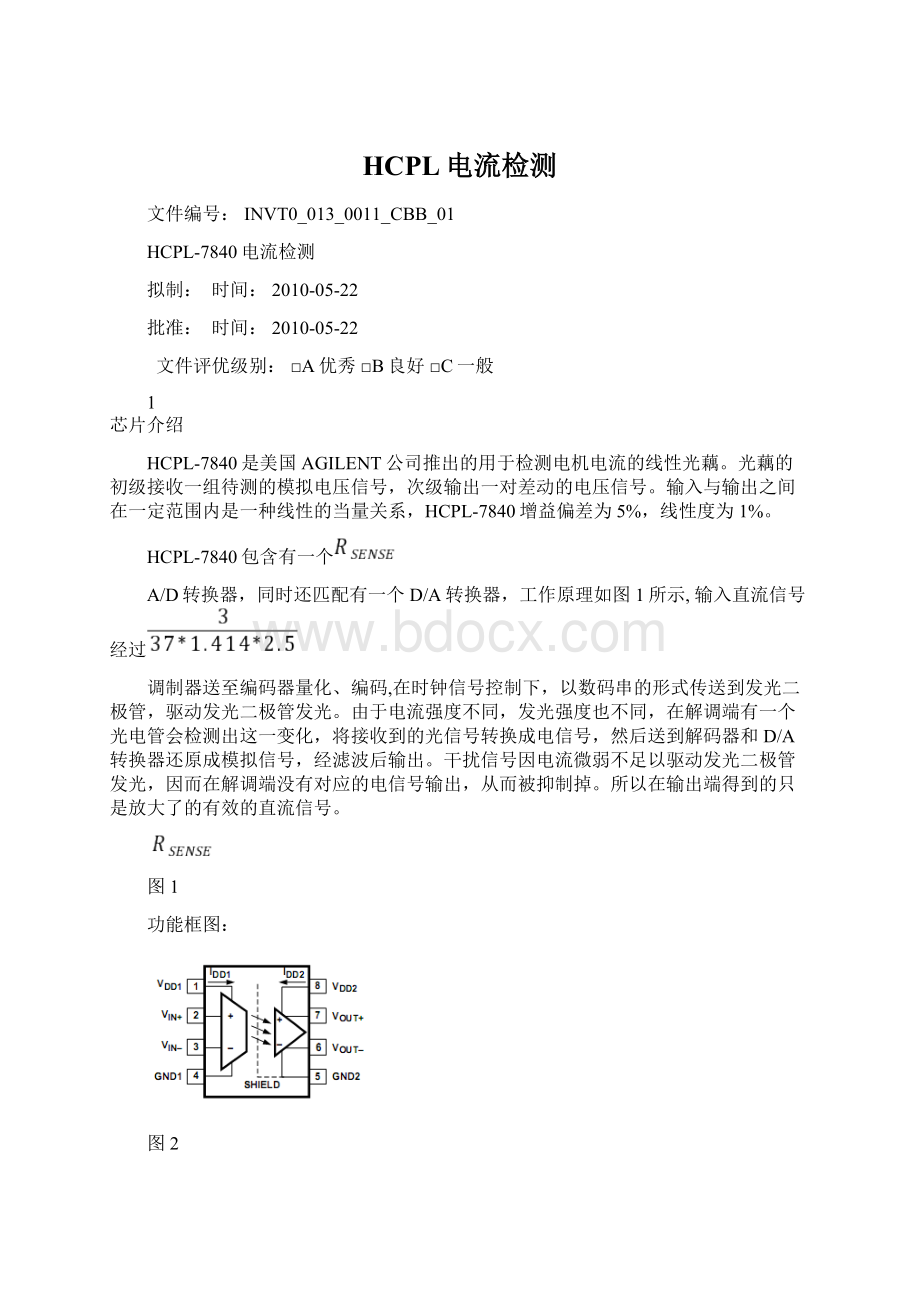

图1

功能框图:

图2

主要性能参数介绍:

parameter

symbol

MIN

TYP

MAX

UNIT

供电电压

VDD1,VDD2

V

增益(Vout/Vin)

G

V/V

输入电压(线性范围)

VIN+,VIN-

-200

+200

mV

输入失调电压

Vos

mV

输入阻抗

RIN

500

k?

输出阻抗

ROUT

15

?

延时时间

TPD50

us

典型应用介绍:

图3

图3中,RSENSE:

采样电阻

HCPL-7840:

线性光藕

78L05:

稳压管

MC34081:

运算放大器

HV+、HV-:

直流母线电压

GATEDRIVECIRCUIT:

驱动电路

HCPL-7840的初级电源由被检电流的上桥电源经5V稳压管提供,次级电源直接由控制电路电源5V供给。

当电机电流流过采样电阻时,电阻两端产生模拟电压,将此电压作为被测信号送入光藕的初级。

光藕的另一端送出一对差动的电压信号,若再经过运算放大器以后,可输出单端模拟电压信号。

当采样电阻阻值给定后,电机电流的变化引起电阻两端电压的变化。

由于HCPL-7840的传输线性度相当高,即使初级电压有毫伏级的变化,次级输出的差动电压也会随之改变。

因此作为被检测的电机电流值,和线性光藕的输出电压值之间有了一一对应的关系。

2目前公司典型应用介绍

图4

图5

图4中通过采样电阻(R226、R227、R228、R229)将W相输出电流信号送至HCPL-7840输入端,此阶段增益为G1=

;图5中将采样电流经过HCPL-7840输出,此阶段增益为G2=8;信号经过运放TL082放大后送至控制板,此阶段增益为G3;系统总增益为

G=G1*G2*G3。

以为例:

输出额定电流为37A,电流定标为:

倍额定电流峰值对应3VDC。

则要求驱动板采样系统总增益为G=

=。

每相采样电阻为4个6mohm/3W并联,电阻采样增益为G1=

=;

HCPL-7840增益G2=8;

后级运放设置增益为G3;则需设计G3=

=

=。

3参数计算

3.1电流采样电阻RSENSE选取:

RSENSE选取要考虑HCPL-7840的输入电压线性范围(-200mV—200mV)。

RSENSE<

=Ω

实际选取4个6mΩ/3W并联,

=Ω。

按150%额定电流计算采样电阻损耗:

PRSENSE=

*RSENSE=

功率降额

*100%=%

采样电阻应具有以下特点

①低阻值

②低感抗

③高精度

实际选取4个Ω/3W并联,料号3-24-10-016,精度1%,低感值电阻。

3.2HCPL-7840供电电源设计:

HCPL-7840采用78L05稳压供电,C23、C10、C11为滤波电容,选取贴片电容。

78L05输出后并联两个电容为了增大电容值,降低电源纹波。

※建议:

78L05前级输入可以考虑增加RC滤波。

在一些机型测试中发现78L05供电被干扰,在78L05前增加RC滤波后干扰消除。

这主要因为78L05从驱动电源取电,引线较长,容易被干扰。

如图6,其中78L05在白线最下方。

为达到较好的滤波效果,RC时间常数越大越好;同时RC时间常数要小于上电时控制板复位和初始化时间,一般为200ms。

HCPL-7840典型输入电流为10mA,考虑到电流较小,可在前增加1uF电容;78L05前面的电阻,按保证78L05输入电压为10V来选即可,即:

R*10mA<(16-10)V,得R<600Ω,取R=510Ω。

电阻功耗为10mA*10mA*510=,T=RC=<200ms。

实际选取R为510Ω/0603,C=1uF/0805,如图8。

通过后续对该RC滤波电路的验证,来作为修改CBB此处的依据。

图6

图8

3.3R84,C111设计:

HCPL-7840输入阻抗为500K,一般R84选取较小阻值,使得R84分压可以忽略不计。

此处R84取68欧。

R84与C111一起构成低通滤波环节,用于抑制高频干扰。

C111取10nF,RC低通滤波器截止频率为fp=

=234KHz;RC延时时间常数为T=R11*C111=。

考虑到RC滤波器对电流信号的延时影响不能太大,RC时间常数一般设计小于1us。

3.4运放电路设计:

运放增益G3=

=

=

运放电路增益G3=

=

。

选取R86=R109=2K,R81=R110=,R120=R135=20K。

R204为输出信号防短路电阻,取100欧姆。

R136作用为干扰信号提供一较低阻抗通路,降低对后级的影响,一般取2K。

C114、C115、C118为滤高频杂波信号电容,均取330P;RC时间常数为2K*330P=(RC时间常数一般设计小于1us)。

※建议:

C115可以考虑去掉。

对于C115,一些实验表明C115作用不大。

在一般的差分运放电路中也很难见到该位置的电容。

增加C115可以认为对滤波效果的加强,但可以通过增大C114,C118的容值达到一样得效果;同时增加C115也会增加电路的延时时间。

通过后续对去掉C115的电路的验证,来作为修改CBB此处的依据。

后附《滤波电容仿真分析报告》。

4器件清单

序号

料号

名称

型号

数量

位号

1

2-15-01-840

光耦;HCPL-7840/DIP-8

HCPL-7840

1

U11

2

3-24-10-016

低值电阻;6mΩ±1%-3W;P=10mm

FLQ50-3W-6mΩ-F/P=10mm

4

R226,R227,R228,R229

3

2-15-11-805

稳压器;5V/100mA/5%/SOT-89

FH78L05

1

U10

4

3-08-97-104

片状电容;100nF±10%-50V-0603-X7R

C1608X7R1H104KT

6

C109,C110

5

3-08-97-103

片状电容;10nF±10%-50V-0603

C1608X7R1H103KT

1

C111

6

3-24-90-680

片状电阻;1/10W-68Ω±1%-0603

68Ω±F-0603

1

R84

7

3-24-90-202

片状电阻;1/10W-2KΩ±1%-0603

2KΩ±F-0603

3

R86,R109,R136

8

3-24-90-472

片状电阻;1/Ω±1%-0603

Ω±F-0603

2

9

3-24-90-203

片状电阻;1/10W-20kΩ±1%-0603

20KΩ±F-0603

2

R120,R135

10

3-24-90-101

片状电阻;1/10W-100Ω±1%-0603

100Ω±F-0603

1

R204

11

3-08-99-331

片状电容;330pF±5%(10%)-50V-0603

C1608COG1H331JT

4

C114,C115,C118

12

2-15-11-082

运放;双单元/SOIC-8

TL082CDR

1

U9

5关键器件资料

6滤波电容仿真分析报告

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- HCPL 电流 检测

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

最新 预制混凝土管片快速拼装加固水下桥墩技术研究PPT文件格式下载.pptx

最新 预制混凝土管片快速拼装加固水下桥墩技术研究PPT文件格式下载.pptx