FPGA课程设计报告.docx

FPGA课程设计报告.docx

- 文档编号:4505025

- 上传时间:2022-12-01

- 格式:DOCX

- 页数:21

- 大小:51.26KB

FPGA课程设计报告.docx

《FPGA课程设计报告.docx》由会员分享,可在线阅读,更多相关《FPGA课程设计报告.docx(21页珍藏版)》请在冰豆网上搜索。

FPGA课程设计报告

ShenyangAgricutturalUniversity

FPGA课程设计报告

题目:

基于CPLD的1602字符液晶显示系统设计院系:

信息与电气工程学院

班级:

电子信息工程

学号:

学生姓名:

指导教师:

成绩:

2011年7月

基于CPLD勺1602字符液晶显示系统设计

一.设计题目:

基于CPLD勺1602字符液晶显示系统设计

二•设计要求技术指标:

要求用1602液晶显示字符;

显示内容:

学号+英文姓名;

显示方式:

流动显示,开关控制字符流动速度及方向;具有暂停和清屏的功能;

三•设计平台:

QUARTUSII6.0软件MARS-1270CPLD1602液晶

四•设计思路与设计步骤:

1.1602液晶指令介绍:

要想控制1602液晶显示字符,首先需要弄清楚1602有那些可控管脚,有哪些控制命令,如何控制其显示,如何控制其移动及如何控制其移动速度及方向等,下面首先介绍一下我所要用的指令及管脚等。

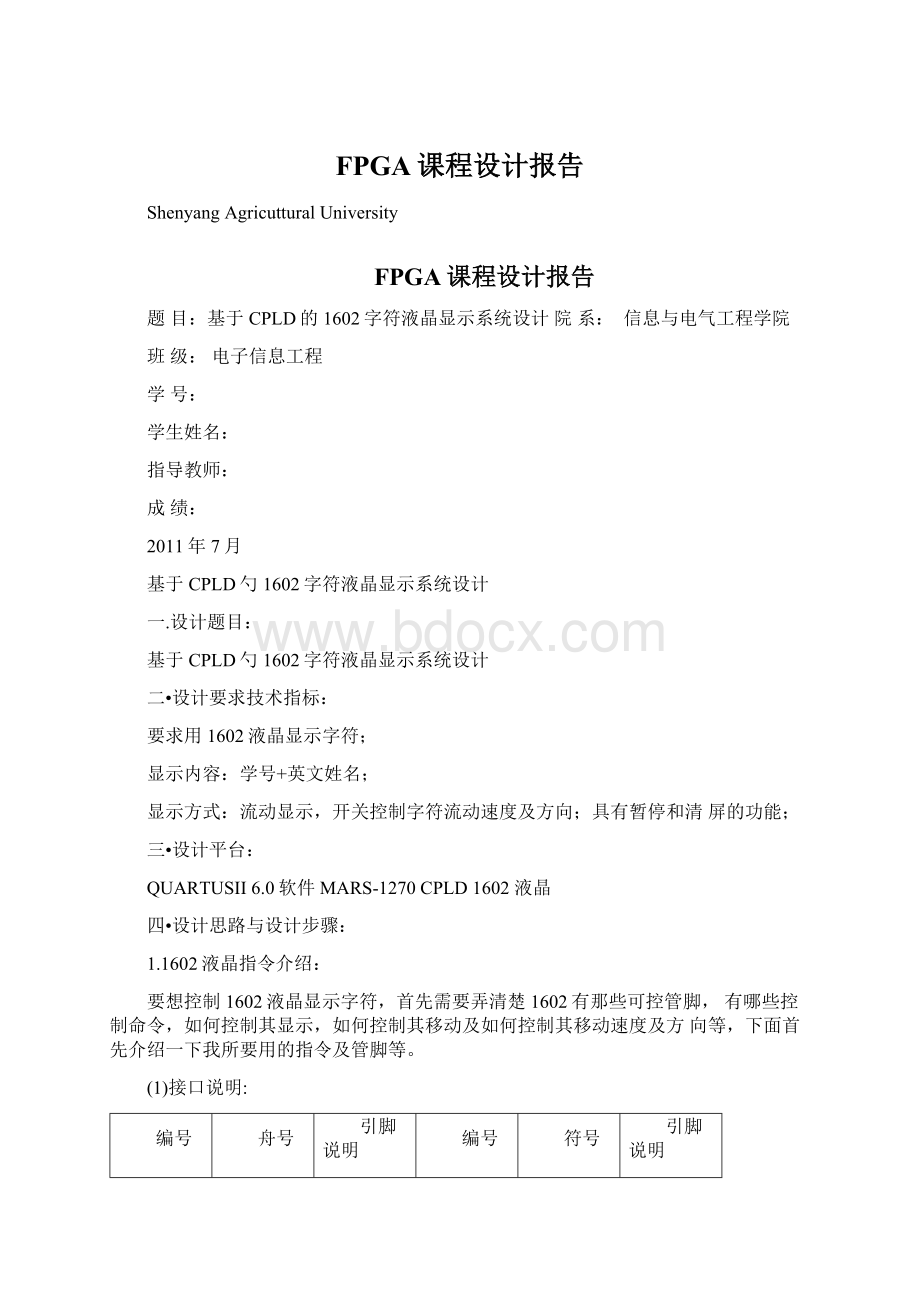

(1)接口说明:

编号

舟号

引脚说明

编号

符号

引脚说明

1

VSS

电踪地

9

D2

DataI/O

2

VDD

电源正极

IQ

D3

DataI/O

3

VL

液晶显示傭压信号

11

D4

DataI/O

4

RS

数据/命令选择端〔WL)

12

D5

Data1/O

5

R/W

读/写选择端(H/L)

13

06

DataI/O

6

E

便能佶号

14

D7

DataI/O

7

DO

DataI/O

15

BLA

背光源正檢

8

01

DataI/O

16

BLK

背光源负根

(2)基本操作时序:

A.读状态:

输入:

RS=LRW=H,E=H,输出:

DB0--DB7=犬态字

B.写指令:

输入:

RS=LRW=L,E下降沿脉冲,DBO--DB7指令码,输出:

无

C.读数据:

输入:

RS=HRW=H,E=H俞出:

DB0--DB7教据

D.写数据:

输入:

RS=HRW=L,E下降沿脉冲,DBO--DB7数据,输出:

无

(3)指令集及其设置说明:

A.清屏指令:

担令功能

梧令编码

/ns

RS

R/W

DB7

DB6

DB5

DB1

1清屏

0

0

0

Q

a

6

0

0

1

1.64

功能:

<1>清除液晶显示器即将DDRAM勺内容全部填入"空白"的ASCII码20H;<2>光标归位,即将光标撤回液晶显示屏的左上方;

<3>将地址计数器(AC)的值设为0。

B.进入设置模式指令:

指令功能

扌旨令编码

RS

R/W

DB7

DB6

DB5

DB1I

DB3

DB2

DB1

DB0

迸入模式设置

0

0

0

D

0

1

I/O

S

40

功能:

设定每次定入1位数据后光标的移位方向,并且设定每次写入的一个字符是否移动。

参数设定的情况如下所示:

位名设置

I/D0=写入新数据后光标左移1=写入新数据后光标右移

S0=写入新数据后显示屏不移1=写入新数据后显示屏整体右移1字符

C.显示开关控制指令:

位名设置

D0=显示功能关1=显示功能开

C0=无光标1=有光标

B0=光标闪烁1=光标不闪烁

D.设定显示屏或光标移动方向指令:

指令功能

指令编码

/U5

RS

R/W

DB7

DB6

DB5

DB3

DB2

D81

DBS

0

9

9

0

0

1

S/C

R/L

K

4D

功能:

使光标移位或使整个显示屏幕移位。

参数设定的情况如下:

S/CR/L

设定情况

0

0

光标左移1格,且AC值减1

0

1

光标右移1格,且AC值加1

1

0

显示器上字付全部左移一格,

但光标不动

1

1

显示器上字符全部右移一格,

但光标不动

E.功能设定指令:

扌旨令功能

挹令编码

/US

RS

R/U

DB7

DB6

DBS

DB4

DB3

D82

DB1

DBB

功能设定

0

0

0

0

1

DL

F

X

X

U0

功能:

设定数据总线位数、显示的行数及字型。

参数设定的情况如下:

位名设置

DL0=数据总线为4位1=数据总线为8位

N0=显示1行1=显示2行

F0=5X7点阵/每字符仁5X10点阵/每字符

F.设定CGRA地址指令:

指令功能

指令编码执行

7us

RS

R/W

DB7

DB6

085

DB4

DB3DB2

DB1

DB0

设定CGRRM體止

B

g

0

1

弱朋11的地址"位J

功能:

设定下一个要存入数据的CGRA的地址。

DB5DB4DB3为字符号,也就是你将来要显示该字符时要用到的字符

地址。

(000~111)(能定义八个字符)

DB2DB1DB0为行号。

(000~111)(八行)

G.设定DDRAM地址指令;

拒令功能

扌旨令编码

/us

RS

R/W

DS7

D86

DB4

DB3

DB2

DB1

DBO

设定BDRAM地址

a

a

1

CGRflW的地址IT位)

48

功能:

设定下一个要存入数据的DDRA的地址

H.数据写入DDRA或CGRAI指令:

指令功能

I指令编码

/US

RS

R/W

DB7

DBA

D眄

DBAi

0B3

DB2

DB1

DBD

数据写入到DDRAM或

CGRflll

1

0

昊写入的数据

4Q

功能:

<1>将字符码写入DDRAM以使液晶显示屏显示出相对应的字符;<2>将使用者自己设计的图形存入CGRA。

DB7DB6DB5可为任何数据,一般取“000”

DB4DB3DB2DB1DB0对应于每行5点的字模数据。

2.设计流程:

弄懂1602中各种管脚及其控制方法以及各种指令的指令码后,就可以进

行程序的编写了,首先整理一下编写流程:

:

初始化

3.设计源程序:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;useIEEE.STD_LOGIC_UNSIGNED.ALL;entitylcd_1602is

Port(clk:

instd_logic;

--读或写指令|数据控制端

--读|写控制端

使能端

reset:

instd_logic;lcdrs:

outstd_logic;lcdrw:

outstd_logic;lcden:

bufferstd_logic;--

data:

outstd」ogic_vector(7downto0);

key1:

instd_logic;--拨码开关控制移动与不动;

key2:

instd」ogic);

endlcd_1602;

ArchitectureBehavioraloflcd_1602is

Typestateis

(set_qingping,set_nobusy,set_cursor,set_switch,set_ddram,write_data,set_ddram1,write_data1,set_ddram2,write_data2,set_ddram3,write_data3,set_ddram4,write_data4,set_ddram5,write_data5,set_ddram6,write_data6,set_ddram7,write_data7,set_ddram8,write_data8,set_ddram9,write_data9,set_ddram10,write_data10,set_ddram11,write_data11,set_ddram12,write_data12,set_ddram13,write_data13,set_ddram14,write_data14,set_ddram15,write_data15,set_ddram17,write_data17,set_ddram16,write_data16,set_ddram18,write_data18,set_ddram19,write_data19,set_ddram20,write_data20,set_ddram21,write_data21,set_ddram22,write_data22,set_ddram23,write_data23,set_cgram,write_cgram,set_ddram24,write_data24,set_ddram25,write_data25,shift_cur,shift_display);--定义各种状态

typeram2isarray(0to7)ofstd_logic_vector(7downto0);

constantcgram:

ram2:

=(("00011111"),("00000100"),("00000100"),

("00011111"),("00000100"),("00000100"),("00000100"),("00011111"));

--把“王”字字模写入数组;

signalcurrent_state:

state;

signalclkcnt:

std_logic_vector(18downto0);

Constantdivcnt:

std_logic_vector(18downto0):

="1111001110001000000";

signalclkdiv:

std_logic;

signaltc_clkcnt:

std_logic;

signalclk_int:

std_logic;

signalclkdiv2:

std_logic;

signalclkdiv3:

std_logic;

signalclkdiv6:

std_logic;

begin

ledrw<='O';--读写控制端设为写有效

process(clk,reset)

Begin

if(reset='O')then

clkcnt<="OOOOOOOOOOOOOOOOOOO";

elsif(clk'eventandclk='1')then

if(clkcnt=divcnt)then

clkcnt<="OOOOOOOOOOOOOOOOOOO";

else

clkcnt<=clkcnt+1;--对系统时钟进行分频使其工作周期为12.5ms

endif;

endif;

endprocess;

tc_clkcnt<='1'whenclkcnt=divcntelse'O';--tc_clkcnt为12.5ms

process(tc_clkcnt,reset)

begin

if(reset='O')then

clkdiv<='O';

elsif(tc_clkcnt'eventandtc_clkcnt='1')then

clkdiv<=notclkdiv;--进一步分频使clkdiv=2*12.5ms;

endif;

endprocess;

process(clkdiv,reset)

begin

if(reset='O')then

clk_int<='O';

elsif(clkdiv'eventandclkdiv='1')then

clk_int<=notclk_int;--再进一步分频使clk_int=4*12.5ms

endif;

endprocess;

process(clk_int,reset)

begin

if(reset='O')then

clkdiv2<='0';--再进一步分频使clkdiv2=8*12.5ms

elsif(clk_int'eventandclk_int='1')then

clkdiv2<=notclkdiv2;

endif;

endprocess;

process(clkdiv2,reset)

begin

if(reset='O')thenclkdiv3<='0';--再进一步分频使clkdiv3=16*12.5ms

elsif(clkdiv2'eventandclkdiv2='1')then

clkdiv3<=notclkdiv3;

endif;

endprocess;

process(clkdiv3,reset)

begin

if(reset='0')thenclkdiv6<='0';--还是进一步分频使clkdiv6=32*12.5mselsif(clkdiv3'eventandclkdiv3='1')then

clkdiv6<=notclkdiv6;

endif;

endprocess;

process(clkdiv3,reset)

begin

if(reset='0')then

lcden<='0';

elsif(clkdiv3'eventandclkdiv3='0')then

lcden<=notlcden;--设置使能信号频率

endif;

endprocess;

附注:

进行多次分频的目地是为了使字符显示速度及移动速度等合适,便于观察。

control:

process(clk,reset,current_state)

variablecnt1:

std」ogic_vector(3downto0);--控制各种状态及其转换

begin

ifreset='0'then

current_state<=set_nobusy;

cnt1:

=(others=>'1');

lcdrs<='0';

elsifrising_edge(clkdiv6)then

--使用clkdiv6是为了和lcden吻合,达到使能目地

current_state<=current_state;

lcdrs<='0';

casecurrent_stateis

whenset_nobusy=>--测试空闲状态

data<="00111000";--38Hcurrent_state<=set_cursor;

whenset_cursor=>

data<="00000110";--进入模式设置状态写入新数据后光标右移

current_state<=set_switch;

whenset_switch=>data<="00001100";--显示开关控制状态;显示功能开

current_state<=set_qingping;

whenset_qingping=>data<="00000001";--清屏指令

current_state<=set_ddram;

whenset_ddram=>data<="10000000";--设置要显示数据的位置:

第1行第1列80H

current_state<=write_data;

whenwrite_data=>

lcdrs<='1';data<="00110001";--设置要显示的数据1current_state<=set_ddram1;

whenset_ddram1=>lcdrs<='0';--设置要显示数据的位置:

第1行第2列81H

data<="10000001";

current_state<=write_data1;

whenwrite_data1=>

lcdrs<='1';--设置要显示的数据2

data<="00110010";

current_state<=set_ddram2;

whenset_ddram2=>

lcdrs<='0';--设置要显示数据的位置:

第1行第3列82H

data<="10000010";--82H

current_state<=write_data2;

whenwrite_data2=>

lcdrs<='1';--设置要显示的数据8

data<="00111000";

current_state<=set_ddram3;

whenset_ddram3=>

lcdrs<='0';--设置要显示数据的位置:

第2行第4列83H

data<="10000011";

current_state<=write_data3;

whenwrite_data3=>

lcdrs<='1';--设置要显示的数据8

data<="00111000";

current_state<=set_ddram4;

whenset_ddram4=>

lcdrs<='0';--设置要显示数据的位置:

第1

data<="10000100";--82Hcurrent_state<=write_data4;

whenwrite_data4=>

lcdrs<='1';--设置要显示的数据4

data<="00110100";

current_state<=set_ddram5;

whenset_ddram5=>

lcdrs<='0';

data<="10000101";--设置要显示数据的位置:

第

current_state<=write_data5;

whenwrite_data5=>

lcdrs<='1';

data<="00110000";--设置要显示的数据0

current_state<=set_ddram6;

whenset_ddram6=>

lcdrs<='0';

data<="10000110";--设置要显示数据的位置:

第

current_state<=write_data6;

whenwrite_data6=>

lcdrs<='1';--设置要显示的数据1

data<="00110001";

current_state<=set_ddram7;

whenset_ddram7=>

lcdrs<='0';

data<="10000111";--设置要显示数据的位置:

第

current_state<=write_data7;

whenwrite_data7=>

lcdrs<='1';--设置要显示的数据5

data<="00110101";

current_state<=set_ddram8;

whenset_ddram8=>

lcdrs<='0';

data<="10001000";--设置要显示数据的位置:

第

行第5列84H

1行第6列85H

1行第7列86H

1行第8列87H

1行第9列88H

current_state<=write_data8;

whenwrite_data8=>

lcdrs<='1';

data<="00101101";--设置要显示的数据-

current_state<=set_ddram9;

whenset_ddram9=>

lcdrs<='0';

data<="10001001";--设置要显示数据的位置:

第

current_state<=write_data9;

whenwrite_data9=>

lcdrs<='1';

data<="01011010";--设置要显示的数据Z

current_state<=set_ddram10;

whenset_ddram10=>

lcdrs<='0';

data<="10001010";--设置要显示数据的位置:

current_state<=write_data10;

whenwrite_data10=>

lcdrs<='1';

data<="01000111";--设置要显示的数据G

current_state<=set_ddram11;

whenset_ddram11=>

lcdrs<='0';

data<="10001011";--设置要显示数据的位置:

current_state<=write_data11;

whenwrite_data11=>

lcdrs<='1';

data<="01001100";--设置要显示的数据L

current_state<=set_ddram12;

whenset_ddram12=>

lcdrs<='0';

data<="11000000";--设置要显示数据的位置:

1行第10列89H

第1行第11列90H

第1行第12列91H

第2行第1列C0H

current_state<=write_data12;

2行第2列C1H

current_state<=write_data13;

whenwrite_data13=>lcdrs<='1';--设置要显示的数据2

data<="00110010";

current_state<=set_ddram14;

whenset_ddram14=>

lcdrs<='0';

data<="11000010";--设置要显示数据的位置:

第

current_state<=write_data14;

whenwrite_data14=>

lcdrs<='1';--设置要显示的数据8

data<="00111000";

current_state<=set_ddram15;

2行第3列C2H

whenset_ddram15=>

lcdrs<='0';

data<="11000011";--设置要显示数据的位置:

第

current_state<=write_data15;

whenwrite_data15=>

lcdrs<='1';

data<="00111000";--设置要显示的数据8

current_state<=set_ddram16;

2行第4列C3H

whenset_ddram16=>

lcdrs<='0';

data<="11000100";--设置要显示数据的位置:

第

current_state

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 课程设计 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx