CPU习题课练习.docx

CPU习题课练习.docx

- 文档编号:4460765

- 上传时间:2022-12-01

- 格式:DOCX

- 页数:11

- 大小:401.84KB

CPU习题课练习.docx

《CPU习题课练习.docx》由会员分享,可在线阅读,更多相关《CPU习题课练习.docx(11页珍藏版)》请在冰豆网上搜索。

CPU习题课练习

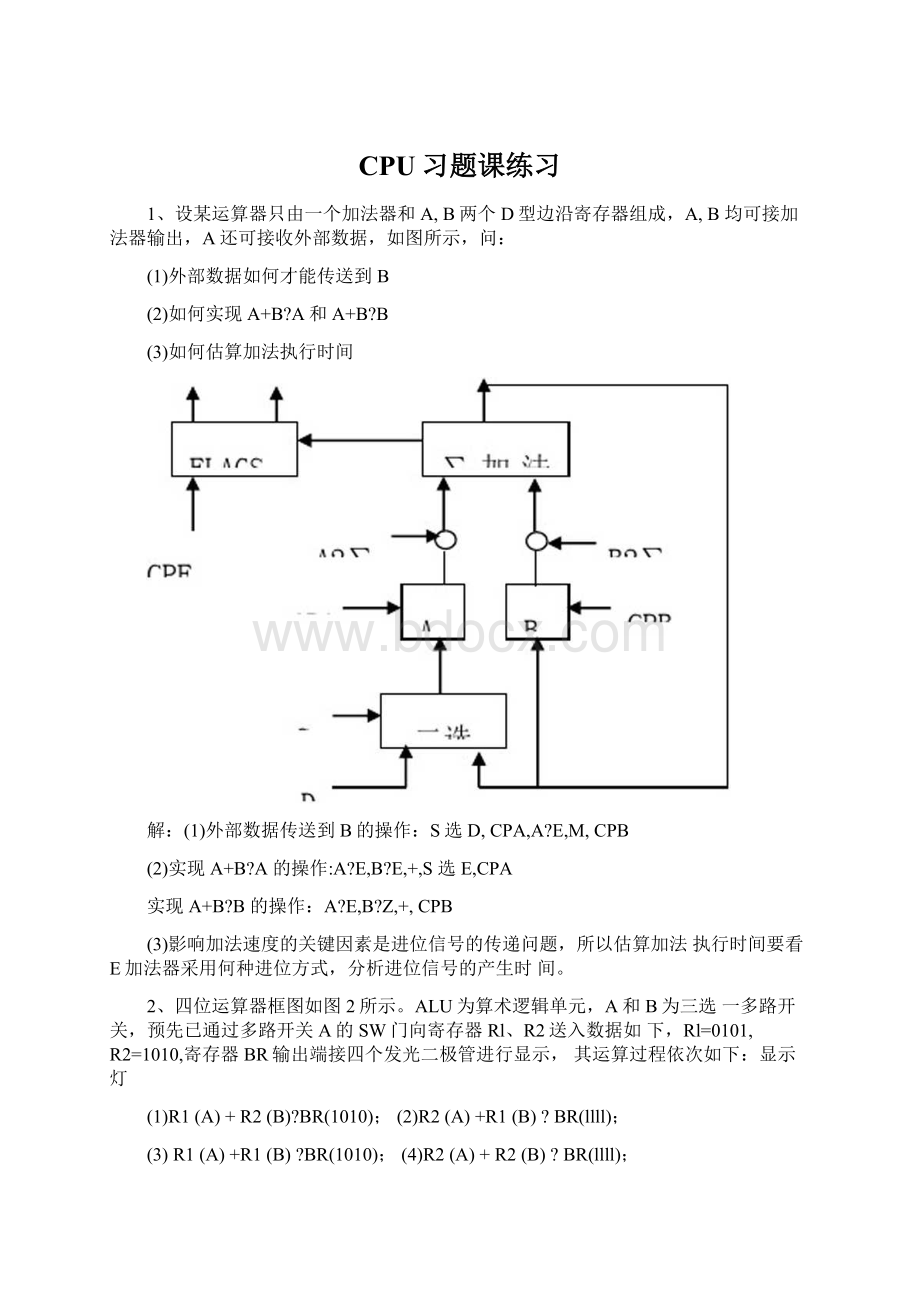

1、设某运算器只由一个加法器和A,B两个D型边沿寄存器组成,A,B均可接加法器输出,A还可接收外部数据,如图所示,问:

(1)外部数据如何才能传送到B

(2)如何实现A+B?

A和A+B?

B

(3)如何估算加法执行时间

解:

(1)外部数据传送到B的操作:

S选D,CPA,A?

E,M,CPB

(2)实现A+B?

A的操作:

A?

E,B?

E,+,S选E,CPA

实现A+B?

B的操作:

A?

E,B?

Z,+,CPB

(3)影响加法速度的关键因素是进位信号的传递问题,所以估算加法执行时间要看E加法器采用何种进位方式,分析进位信号的产生时间。

2、四位运算器框图如图2所示。

ALU为算术逻辑单元,A和B为三选一多路开关,预先已通过多路开关A的SW门向寄存器Rl、R2送入数据如下,Rl=0101,R2=1010,寄存器BR输出端接四个发光二极管进行显示,其运算过程依次如下:

显示灯

(1)R1(A)+R2(B)?

BR(1010);

(2)R2(A)+R1(B)?

BR(llll);

(3)R1(A)+R1(B)?

BR(1010);(4)R2(A)+R2(B)?

BR(llll);

(5)R2(A)+BR(B)?

BR(11U);(6)R1(A)+BR(B)?

BR(1010);

试分析运算器的故障位置,说明理由。

BSo

BSt

ASX

LDR:

p

解:

运算器的故障位置在多路开关B,其输出始终为R1的值。

分析如下:

(1)Ri(A)+R2(B)=1010,输出结果错

(2)R2(A)+RdB)=1111,结果正确,说明R2(A),Rj(B)无错

(3)Rt(A)+Rt(B)=1010,结果正确,说明Rt(A),Rx(B)无错由此可断定ALU和BR无错

(4)R2(A)+R2(B)=1001,结果错,由于R2⑷正确且&⑷=1010推知R2(B)=0101,显然多路开关B有问题

(5)R2(A)+BR(B)=1111,结果错,由于R2(A)=1010,BR(B)=1111,但现推知BR(B)=0101,证明开关B输出有错

(6)Ri(A)+BR(B)=1010,结果错,由于R】(A)=0101,本应BR(B)=1111,但现推知BR(B)=0101,证明开关B输出有错

综上所述,多路开关B输出有错。

故障性质:

多路开关B输出始终为0101,这有两种可能:

一是控制信号BS°,BS】始终为01,故始终选中寄存器Ri;二是多路开关B电平输出始终嵌在0101±o

3、某运算部件的基本结构如图3所示,假定此部件只有加(+)和减(-)两种基本操作,要求:

(1)给出运算部件的所有微命令。

(2)指出哪些微命令是相容的,哪些是相斥的

(3)试用位数最少的操作控制字段来表示全部微命令。

图3

解:

(1)运算部件的微命令如下图所示。

(2)R2?

Y与R1?

Y是相斥的;+与-是相斥的;DBUS2R1与DBUS7R2是相容的;R1?

X与R2?

Y是相容的。

(3)微命令采用字段直接编码法。

DBUS7R1与DBUS?

R2在指令的执行过程中不会同时出现,可以将它们放在同一字段,用2位来控制。

+与-也是相斥的,放在同一字段,用2位来控制,但由于能放在同一字段的微命令只有2位,采用直接控制法也只需用2位,所以采用直接控制。

根据以上分析,操作控制字段共有8个微命令,全部采用直接控制方式。

4、图4所示为双总线结构机器的数据通路,:

ER为指令寄存器,PC

为程序计数器(具有自增功能),M为主存(受R/W信号控制),AR为主存地址寄存器,DR为数据缓冲寄存器。

ALU由加减控制信号决定完成何种操作。

控制信号G控制的是一个门电路。

另外,线上标注有控制信号,例如Yi表示Y寄存器的输入控制信号,Rio表示寄存器R1的输出控制信号。

未标注的线为直通线,不受控制。

现有“ADDR2,RO”指令完成(RO)+(R2)〜R0的功能操作。

请画出该指令的指令周期流程图,并列出相应的微命令控制信号序列。

假设该指令的地址已放入PC中。

图4

解:

ADD指令是加法指令,参与运算的二数放在R0和R2中,相加结果

放在R0中。

指令周期流程图如下图所示,包括取指令阶段和执行

指令阶段两部分。

每一方框表示一个CPU周期。

其中框内表示数据

传送路径,框外列出微操作控制信号。

DRo,G,IRi

5、一台处理机具有如下指令格式

2位6位3位3位

X

0P

源寄存器

目标寄存

器

地址

格式表明有8个通用寄存器(长度16位),X指定寻址模式,主存实际容量为256k字。

假设不用通用寄存器也能直接访问主存中的每一个单元,并假设操作码域0P=6位,请问地址码域应分配多少位指令字长度应有多少位

假设X=ll时,指定的那个通用寄存器用做基值寄存器,请提出一个硬件设计规划,使得被指定的通用寄存器能访问1M主存空间中的每一个单元。

解:

(1)因为2性256K,所以地址码域=18位,操作码域=6位

指令长度=18+3+3+6+2=32位

(2)此时指定的通用寄存器用作基值寄存器(16位),但16位

长度不足以覆盖1M字地址空间,为此将通用寄存器左移,4位低位补0

形成20位基地址。

然后与指令字形式地址相加得有效地址,可访问主存

1M地址空间中任何单元。

6、某计算机有8条微指令L-Is,每条微指令所包含的微命令控制信号见下表所示,a-j分别对应10种不同性质的微命令信号。

假设微指令的控制字段仅限8位,请安排微指令的控制字段格式。

微指令

a

b

c

d

e

f

g

h

•

1

j

h

12

【3

14

16

17

【8

7

7

7

V

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

解:

微指令的控制字段为8位。

根据10个微命令的兼容性和互斥性,分成3组。

分别为2位、

2位和4位的小字段。

每个2位的组是3个微命令的编码,需

译码。

4位的组每位是1个微命令,不需译码。

2位2位4位

本题可以有以下4种不同的解答。

⑴互斥的d,h,i为一组。

互斥的e,f,J为

一组。

其余的a,b>c,g为一组。

⑵互斥的b,i,j为一组。

互斥的e,f,h为

一组。

其余的a,c,d,g为一组。

d,e为一组。

⑷互斥的b,g,j为一组。

互斥的e,f,h为一组。

其余的a,c

d,i为一组。

7、设某一微操作控制信号G既发生在指令1(设操作码0P为LI2=11)的节拍电位址、节拍脉冲A时间,也发生在指令2(设0P为BL=01)的节拍电位临节拍脉冲T2时间,写出Ci的逻辑表达式,并表示在如图所

示的GAL器件中。

(2)画图

8、CPU数据通路为双总线结构,如图所示。

图中:

ALU:

运算器IR:

指令寄存器

Ra:

ALU的输入寄存器PC:

程序计数器R广R4:

程序员可用通用寄存

器MAR:

存储器地址寄存器MDR:

存储器数据寄存器

(1)画出修正错误后的连线图。

(2)描述指令ADDaddr,R1(功能是R1+(addr)?

addr)的执行过程。

CC

解:

(1)画图

on

(2)指令ADDaddr,R1的执行过程

PC?

MAR;M?

MDR;MDR?

IR;IR(addr)?

MAR;M?

MDR;MDR?

&

Ri?

MDR;+;ADD?

MDR;addr?

MAR;MDR?

M

其中前3条微指令用来取指令;第4、5、6条微指令用来将IR地址部分给出的直接地址addr的内容送入Ra;第9条微指令实现加法并将结果送入MDR;第11条微指令将加法结果送回addr的存储器。

9、某计算机的数据通路如下图所示,其中M—主存,MBR—主存数据寄存器,MAR—主存地址寄存器,R0-R3—通用寄存器,IR—指令寄存器,PC-程序计数器(具有自增能力),C、D—暂存器,ALU—算术逻辑单元(此处做加法器看待),移位器一左移、右移、直通传送。

所有双向箭头表示信息可以双向传送。

请按数据通路图画出“ADD(Rl),(R2)”指令的指令周期流程图。

该指令的含义是两个数进行求和操作。

其中源操作地址在寄存器R1中,目的操作数寻址方式为自增型寄存器间接寻址(先取地址后加1)。

解:

解:

“ADD(Rl),(R2)+”指令是SS型指令,两个操作数均在主存中。

其中源操作数地址在R1中,所以是R1间接寻址。

目的操作数地址在R2中,由R2间接寻址,但R2的内容在取出操作数以后要加1进行修改。

指令周期流程图如下:

(每个步骤1分)

10、某指令系统指令字长为20位,具有双操作数、单操作数和无操作数3种指令格式,每个操作数地址规定用6位二进制表示,当双操作数指令和单操作数指令条数均取最大值时,这3种指令最多可能拥有的指令数各是多少

解:

解:

按控制操作码的思想来设计,双操作数指令条数最大为2「1=255条,单操作数指令条数最大为63条,无操作数指令条数最大为64条。

00000000XXXXXXXXXXXX

>■

•••

•♦•

255条二地址指令

XXXXXX

XXXXXX

0

00000

XXXXXX

•••

•••

63条一地址指令

1

11110

XXXXXX

64条零地址指令

•••••••••

111111111111

1K单总线CPU结构如图所示,其中有运算部件ALU.寄存器Y和乙通

用寄存器R0〜R3、指令寄存器IR、程序计数器PC、主存地址寄存器

MAR和主存数据寄存器MDR等部件。

试拟出转移指令JMP?

#A的读取

和执行流程。

(2)DBUS?

MDR,MDR?

IR

(3)PC?

YIR(地址段)+Y?

ZZ?

PC

12、假设某机器有86条指令,平均每条指令由12条微指令组成,

其中一条是取指微指令,是公用的,已知微指令字长48位,请问控制存

储器的容量需多大

解:

共有微指令(12-1)X86+1=947条,控存的容量为947X48bito

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CPU 习题 练习

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx