电子系统多路彩灯.docx

电子系统多路彩灯.docx

- 文档编号:4440883

- 上传时间:2022-12-01

- 格式:DOCX

- 页数:5

- 大小:126.84KB

电子系统多路彩灯.docx

《电子系统多路彩灯.docx》由会员分享,可在线阅读,更多相关《电子系统多路彩灯.docx(5页珍藏版)》请在冰豆网上搜索。

电子系统多路彩灯

1系统设计要求

需设计一个十六路彩灯控制器,6种花型循环变化,有清零开关,并且可以选择快慢两种节拍。

2系统设计方案

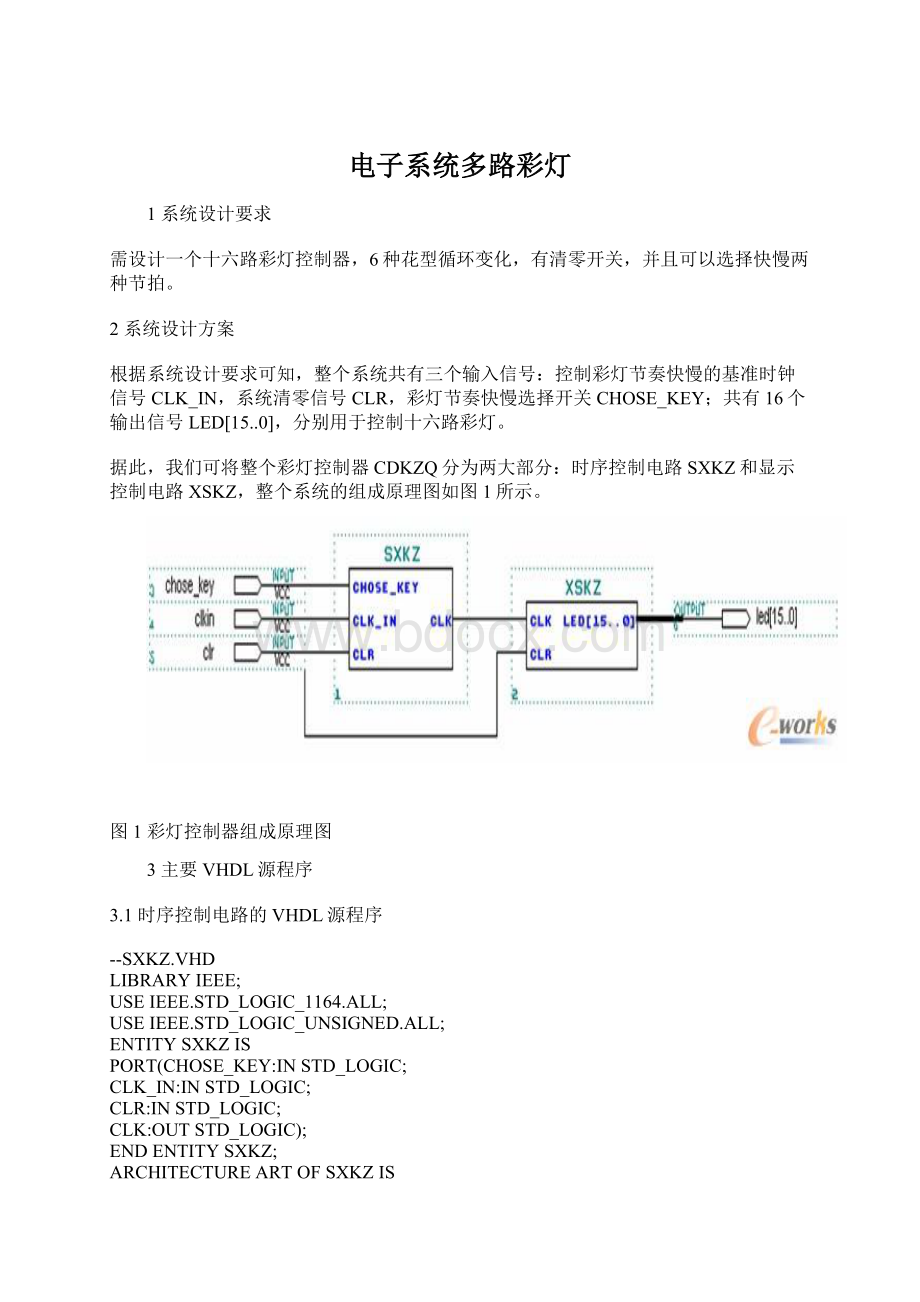

根据系统设计要求可知,整个系统共有三个输入信号:

控制彩灯节奏快慢的基准时钟信号CLK_IN,系统清零信号CLR,彩灯节奏快慢选择开关CHOSE_KEY;共有16个输出信号LED[15..0],分别用于控制十六路彩灯。

据此,我们可将整个彩灯控制器CDKZQ分为两大部分:

时序控制电路SXKZ和显示控制电路XSKZ,整个系统的组成原理图如图1所示。

图1彩灯控制器组成原理图

3主要VHDL源程序

3.1时序控制电路的VHDL源程序

--SXKZ.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSXKZIS

PORT(CHOSE_KEY:

INSTD_LOGIC;

CLK_IN:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

CLK:

OUTSTD_LOGIC);

ENDENTITYSXKZ;

ARCHITECTUREARTOFSXKZIS

SIGNALCLLK:

STD_LOGIC;

BEGIN

PROCESS(CLK_IN,CLR,CHOSE_KEY)IS

VARIABLETEMP:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

IFCLR='1'THEN--当CLR='1'时清零,否则正常工作

CLLK<='0';TEMP:

="000";

ELSIFRISING_EDGE(CLK_IN)THEN

IFCHOSE_KEY='1'THEN

IFTEMP="011"THEN

TEMP:

="000";

CLLK<=NOTCLLK;

ELSE

TEMP:

=TEMP+'1';

ENDIF;

--当CHOSE_KEY='1'时产生基准时钟频率的1/4的时钟信号,否则产生基准时钟

--频率的1/8的时钟信号

ELSE

IFTEMP="111"THEN

TEMP:

="000";

CLLK<=NOTCLLK;

ELSE

TEMP:

=TEMP+'1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

CLK<=CLLK;

ENDARCHITECTUREART;

3.2显示控制电路的VHDL源程序

--XSKZ.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYXSKZIS

PORT(CLK:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

LED:

OUTSTD_LOGIC_VECTOR(15DOWNTO0));

ENDENTITYXSKZ;

ARCHITECTUREARTOFXSKZIS

TYPESTATEIS(S0,S1,S2,S3,S4,S5,S6);

SIGNALCURRENT_STATE:

STATE;

SIGNALFLOWER:

STD_LOGIC_VECTOR(15DOWNTO0);

BEGIN

PROCESS(CLR,CLK)IS

CONSTANTF1:

STD_LOGIC_VECTOR(15DOWNTO0):

="0001000100010001";

CONSTANTF2:

STD_LOGIC_VECTOR(15DOWNTO0):

="1010101010101010";

CONSTANTF3:

STD_LOGIC_VECTOR(15DOWNTO0):

="0011001100110011";

CONSTANTF4:

STD_LOGIC_VECTOR(15DOWNTO0):

="0100100100100100";

CONSTANTF5:

STD_LOGIC_VECTOR(15DOWNTO0):

="1001010010100101";

CONSTANTF6:

STD_LOGIC_VECTOR(15DOWNTO0):

="1101101101100110";

--六种花型的定义

BEGIN

IFCLR='1'THEN

CURRENT_STATE<=S0;

ELSIFRISING_EDGE(CLK)THEN

CASECURRENT_STATEIS

WHENS0=>

FLOWER<="ZZZZZZZZZZZZZZZZ";

CURRENT_STATE<=S1;

WHENS1=>

FLOWER<=F1;

CURRENT_STATE<=S2;

WHENS2=>

FLOWER<=F2;

CURRENT_STATE<=S2;

WHENS3=>

FLOWER<=F2;

CURRENT_STATE<=S4;

WHENS4=>

FLOWER<=F4;

CURRENT_STATE<=S5;

WHENS5=>

FLOWER<=F5;

CURRENT_STATE<=S6;

WHENS6=>

FLOWER<=F6;

CURRENT_STATE<=S1;

ENDCASE;

ENDIF;

ENDPROCESS;

LED<=FLOWER;

ENDARCHITECTUREART;

分页

3.3整个电路系统的VHDL源程序

--CDKZQ.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCDKZQIS

PORT(CLK_IN:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

CHOSE_KEY:

INSTD_LOGIC;

LED:

OUTSTD_LOGIC_VECTOR(15DOWNTO0));

ENDENTITYCDKZQ;

ARCHITECTUREARTOFCDKZQIS

COMPONENTSXKZIS

PORT(CHOSE_KEY:

INSTD_LOGIC;

CLK_IN:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

CLK:

OUTSTD_LOGIC);

ENDCOMPONENTSXKZ;

COMPONENTXSKZIS

PORT(CLK:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

LED:

OUTSTD_LOGIC_VECTOR(15DOWNTO0));

ENDCOMPONENTXSKZ;

SIGNALS1:

STD_LOGIC;

BEGIN

U1:

SXKZPORTMAP(CHOSE_KEY,CLK_IN,CLR,S1);

U2:

XSKZPORTMAP(S1,CLR,LED);

ENDARCHITECTUREART;

4系统仿真/硬件验证

4.1系统的有关仿真

时序控制电路SXKZ、显示控制电路XSKZ及整个电路系统CDKZQ的仿真图分别如图2、图3和图4所示。

图2时序控制电路SXKZ仿真图

图3显示控制电路XSKZ仿真图

图4整个电路系统CDKZQ仿真图

4.2系统的硬件验证

系统通过仿真后,我们可根据自己所拥有的EDA实验开发系统进行编程下载和硬件验证。

考虑到一般EDA实验开发系统提供的输出显示资源有限,我们可将输出适当调整后进行硬件验证。

5设计技巧分析

(1)在时序控制电路SXKZ的设计中,利用计数器计数达到分频值时,对计数器进行清零,同时将输出信号反向,这就非常简洁地实现了对输入基准时钟信号的分频,并且分频信号的占空比为0.5。

(2)在显示控制电路XSKZ的设计中,利用状态机非常简洁地实现了六种花型的循环变化,同时利用六个十六位常数的设计,可非常方便地设置和修改六种花型。

(3)对于顶层程序的设计,因本系统模块较少,既可使用文本的程序设计方式,也可使用原理图的设计方式。

但对于模块较多的系统,最好使用文本的程序设计方式。

6系统扩展思路

(1)在彩灯的快慢节奏的控制上,若去掉快慢节奏控制开关,如何控制快慢节奏的交替变化。

(2)设计外围电路:

系统用方波信号源、直流工作电源、彩灯控制的驱动电路。

(3)若为课程设计,除要求设计调试程序、外围电路外,还可要求设计、制作整个系统,包括PCB的制作。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电子 系统 彩灯

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx