将turbo51挂接在AHB总线并实现加法功能.docx

将turbo51挂接在AHB总线并实现加法功能.docx

- 文档编号:4371640

- 上传时间:2022-12-01

- 格式:DOCX

- 页数:32

- 大小:586.07KB

将turbo51挂接在AHB总线并实现加法功能.docx

《将turbo51挂接在AHB总线并实现加法功能.docx》由会员分享,可在线阅读,更多相关《将turbo51挂接在AHB总线并实现加法功能.docx(32页珍藏版)》请在冰豆网上搜索。

将turbo51挂接在AHB总线并实现加法功能

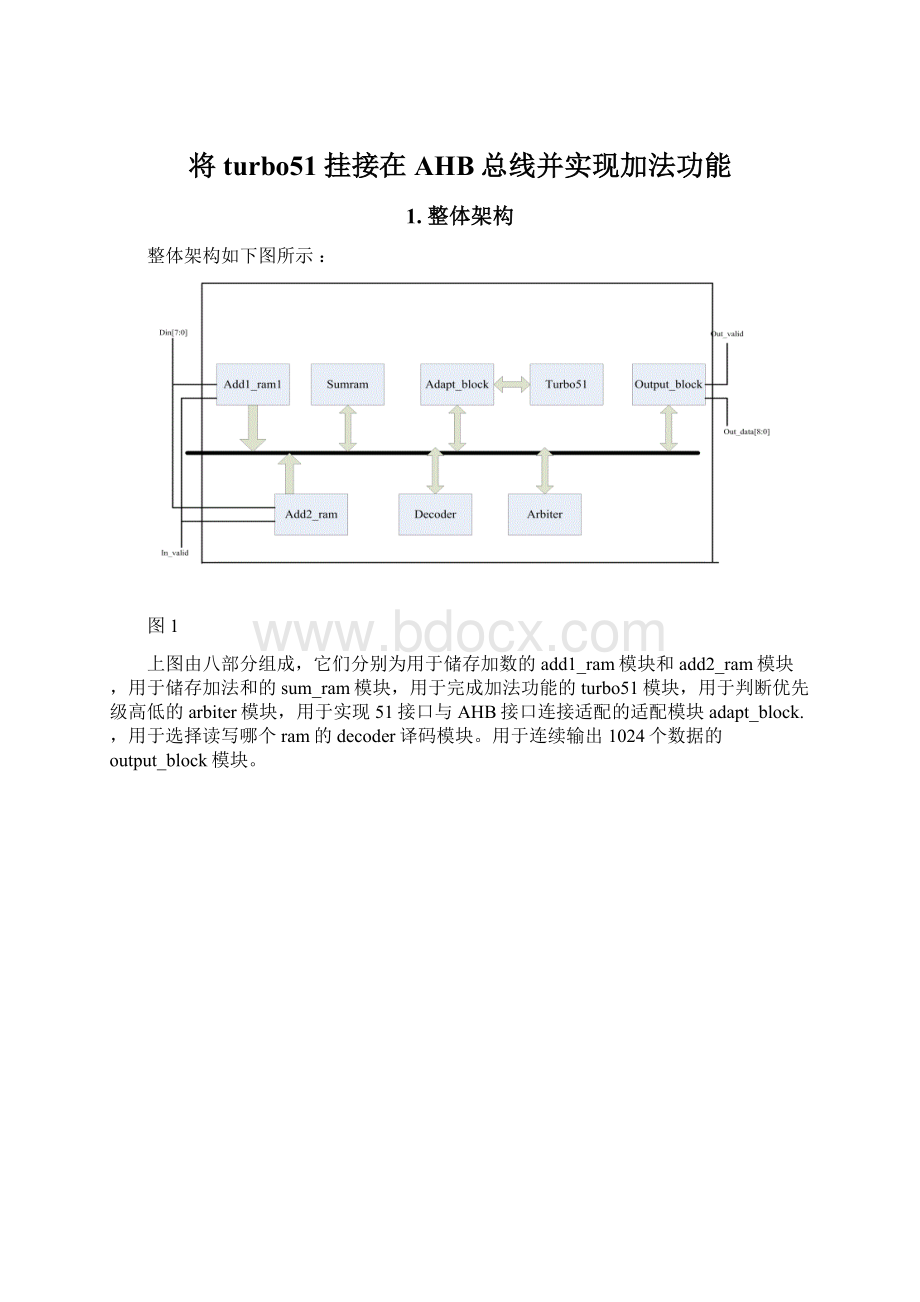

1.整体架构

整体架构如下图所示:

图1

上图由八部分组成,它们分别为用于储存加数的add1_ram模块和add2_ram模块,用于储存加法和的sum_ram模块,用于完成加法功能的turbo51模块,用于判断优先级高低的arbiter模块,用于实现51接口与AHB接口连接适配的适配模块adapt_block.,用于选择读写哪个ram的decoder译码模块。

用于连续输出1024个数据的output_block模块。

2.整体架构描述

图2

上图为一个基于AMBAAHB的系统,AMBAAHB总线协议设计使用一个中央多路选择器互联方案,使用该方案所有总线主机设备输出地址和控制信号来指示它们想执行的传输同时仲裁器决定哪一个主机能够将它的地址和控制信号联通到所有的主机,当然就需要一个译码器来控制读数据和相应多路信号选择器,多路信号选择器选中来自传输中所包含从机的适当信号。

此项目包括adapt_block和output_block两个主机模块及add1_ram,add2_ram,sum_ram三个从机模块.以及用于选择从机信号的decoder模块和用于判断主机优先级的arbiter模块.其中add1_ram,add2_ram用于存储加数,sum_ram用于存储加法和.output_block模块用于连续输出1024个加法和.此项目的核心模块为adapt_block模块,它将turbo51例化,并通过AHB总线将add1_ram和add2_ram中的数读入其模块并通过databus将加数送入turbo51中进行加法运算,最后将得出的加法和结果写入sum_ram模块中。

此模块既包括对add1_ram,add2_ram和sum_ram的读写控制,也包括对51接口和AHB接口的适配的实现。

为此次项目的重点。

3.各模块功能及其时序

本节是这篇文档的关键部分,主要论述了各个功能块的结构,对相应的时序也作了说明。

图3

3.1ADD1_RAM模块

接口说明:

PIN

I/O

DISCRIBE

HCLK

I

时钟信号,为所有总线提供时基。

所有信号时序都和HCLK的上升沿相关。

HRESETn

I

系统的复位信号低有效并用来复位系统和总线,这是唯一的低有效的信号。

DIN

I

从tb中输入,用于向ram中输入数据。

WRITE

I

从tb中输入,用于控制ram1的写操作。

HSEL_RAM1

I

用于选择RAM1进行读写操作的选择信号。

HADDR[31:

0]

I

从主机输出给从机的地址,用于选择相关地址。

32位系统地址总线。

HWRITE

I

从主机输出给从机的信号,用于指示读写操作。

当为高表示一个写操作,为低表示一个读操作。

HTRANS[1:

0]

I

表示当前传输的类型,可以是不连续,连续,空闲和忙。

HSIZE[2:

0]

I

表示传输的大小,典型情况是字节(8位),半字(16位),或者是字(32位)。

协议允许最大的传输大小可以达到1024位。

HBURST[2:

0]

I

表示传输是否组成了突发的一部分,支持四个,八个或者16个节拍的突发传输并且突发传输可以是增量或者是回环。

HWDATA[31:

0]

I

写数据总线用在写操作期间从主机到总线从机传输数据,建议最小的数据总线宽度为32位,然而,在要求高宽带运行时扩展(数据总线)还是很容易的。

HREADY_RAM1

O

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HRESP_RAM1[1:

0]

O

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRDATA_RAM1[31:

0]

O

读数据总线用来在读操作期间从总线从机向总线主机传输数据,建议最小的数据总线宽度为32位,然而在要求高宽带运行时扩展(数据总线)还是很容易的。

FULL_1

O

表示当前RAM1已经写满

(2)接口框图:

图4

(3)逻辑图:

图5

由于自动生成的RAM8_1024的输入和输出的数据和地址与总线所要求的位数不匹配,故需要通过ADD1_RAM对生成的RAM8_1024进行操作,使其能够连接在总线上并完成读和写的操作。

由上图可以看出当WRITE为高电平时,对RAM8_1024进行写操作,此时依次将DIN中的数据存储于RAM8_1024中,当WRITE为低电平时,读出haddr中的数据dout,并通过位拼接将{24’B0,dout}作为hrdata_ram1送入总线,从而实现将RAM8_1024挂接在总线上实现读写功能。

(4)内部详细设计:

这个模块为ADD1_RAM模块,深度为1024,数据位宽为8位。

主要用于存储加数。

通过tb来控制ADD1_RAM的写操作且从tb中输入数据进入ADD1_RAM。

该模块对自动生成的ram模块进行例化。

由于自动生成的ram模块没有读控制信号,其在地址addr输入以后会自动读出数据dout并通过HRDATA_RAM1送入总线进入主机ADAPT_BLOCK模块。

当WRITE为高电平1时,可以将从TB中写入的DIN写入RAM1中,从而完成对RAM1的写操作。

在此次项目中主要是将1024个加数通过DIN输入存储于该ADD1_RAM中。

并将这1024个加数依次送入ADAPT_BLOCK模块作为加数完成运算。

图6

上图中的WRITE是在TB中控制的,当WRITE为高时,将DIN输入到RAM1的MEMORY中,只到写入1024个数据以后,控制写操作的IN_VALID置低,此时,不再往里写数.

3.2ADD2_RAM模块:

接口说明:

PIN

I/O

DISCRIBE

HCLK

I

时钟信号,为所有总线提供时基。

所有信号时序都和HCLK的上升沿相关。

HRESETn

I

系统的复位信号低有效并用来复位系统和总线,这是唯一的低有效的信号。

DIN

I

从tb中输入,用于向ram2中输入数据。

WRITE

I

从tb中输入,用于控制ram2的写操作。

HSEL_RAM2

I

用于选择RAM2进行读写操作的选择信号。

HADDR[31:

0]

I

从主机输出给从机的地址,用于选择相关地址。

32位系统地址总线。

HWRITE

I

从主机输出给从机的信号,用于指示是读操作还是写操作。

当为高表示一个写操作,为低表示一个读操作。

HTRANS[1:

0]

I

表示当前传输的类型,可以是不连续,连续,空闲和忙。

HSIZE[2:

0]

I

表示传输的大小,典型情况是字节(8位),半字(16位),或者是字(32位)。

协议允许最大的传输大小可以达到1024位。

HBURST[2:

0]

I

表示传输是否组成了突发的一部分,支持四个,八个或者16个节拍的突发传输并且突发传输可以是增量或者是回环。

HWDATA[31:

0]

I

写数据总线用在写操作期间从主机到总线从机传输数据,建议最小的数据总线宽度为32位,然而,在要求高宽带运行时扩展(数据总线)还是很容易的。

HREADY_RAM2

O

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HRESP_RAM2[1:

0]

O

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRDATA_RAM2[31:

0]

O

读数据总线用来在读操作期间从总线从机向总线主机传输数据,建议最小的数据总线宽度为32位,然而在要求高宽带运行时扩展(数据总线)还是很容易的。

FULL_2

O

表示当前RAM已经写满

(2)接口框图:

图7

(3)逻辑图:

图8

由于自动生成的RAM8_1024的输入和输出的数据和地址与总线所要求的位数不匹配,故需要通过ADD1_RAM对生成的RAM8_1024进行操作,使其能够连接在总线上并完成读和写的操作。

由上图可以看出当WRITE为高电平时,对RAM8_1024进行写操作,此时依次将DIN中的数据存储于RAM8_1024中,当WRITE为低电平时,读出haddr中的数据dout,并通过位拼接将{24’B0,dout}作为hrdata_ram1送入总线,从而实现将RAM8_1024挂接在总线上实现读写功能。

(4)内部详细设计:

这个模块为ADD1_RAM模块,深度为1024,数据位宽为8位。

主要用于存储加数。

通过tb来控制ADD1_RAM的写操作且从tb中输入数据进入ADD1_RAM。

该模块对自动生成的ram模块进行例化。

由于自动生成的ram模块没有读控制信号,其在地址addr输入以后会自动读出数据dout并通过HRDATA_RAM1送入总线进入主机ADAPT_BLOCK模块。

当WRITE为高电平1时,可以将从TB中写入的DIN写入RAM1中,从而完成对RAM1的写操作。

在此次项目中主要是将1024个加数通过DIN输入存储于该ADD1_RAM中。

并将这1024个加数依次送入ADAPT_BLOCK模块作为加数完成运算。

图9

上图中的WRITE是在TB中控制的,当WRITE为高时,将DIN输入到RAM2的MEMORY中,只到写入1024个数据以后,控制写操作的IN_VALID置低,此时,不再往里写数.

3.3SUM_RAM模块:

接口说明:

PIN

I/O

DISCRIBE

HCLK

I

时钟信号,为所有总线提供时基。

所有信号时序都和HCLK的上升沿相关。

HRESETn

I

系统的复位信号低有效并用来复位系统和总线,这是唯一的低有效的信号。

HSEL_SUMRAM

I

用于选择SUM_RAM进行读写操作的选择信号。

HADDR[31:

0]

I

从主机输出给从机的地址,用于选择相关地址。

32位系统地址总线。

HWRITE

I

从主机输出给从机的信号,用于指示读写操作。

当为高表示一个写操作,为低表示一个读操作。

HTRANS[1:

0]

I

表示当前传输的类型,可以是不连续,连续,空闲和忙。

HSIZE[2:

0]

I

表示传输的大小,典型情况是字节(8位),半字(16位),或者是字(32位)。

协议允许最大的传输大小可以达到1024位。

HBURST[2:

0]

I

表示传输是否组成了突发的一部分,支持四个,八个或者16个节拍的突发传输并且突发传输可以是增量或者是回环。

HWDATA[31:

0]

I

写数据总线用在写操作期间从主机到总线从机传输数据,建议最小的数据总线宽度为32位,然而,在要求高宽带运行时扩展(数据总线)还是很容易的。

HREADY_SUMRAM

O

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HRESP_SUMRAM[1:

0]

O

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRDATA_SUMRAM[31:

0]

O

读数据总线用来在读操作期间从总线从机向总线主机传输数据,建议最小的数据总线宽度为32位,然而在要求高宽带运行时扩展(数据总线)还是很容易的。

FULL_SUMRAM

O

表示当前RAM已经写满

(2)接口框图:

图10

(3)逻辑框图:

图11

由于自动生成的RAM9_1024的输入和输出的数据和地址与总线所要求的位数不匹配,故需要通过SUM_RAM对生成的RAM9_1024进行操作,使其能够连接在总线上并完成读和写的操作。

由上图可以看出当HWRITE,HSEL_SUMRAM,HREADY_SUMRAM为高电平时,WR为’1’,对RAM9_1024进行写操作,此时依次将HWDATA[8:

0]中的数据存储于RAM9_1024中,当为WR低电平时,读出haddr中的数据dout,并通过位拼接将{23’B0,dout}作为hrdata_sumram送入总线。

故对SUM_RAM模块进行读写操作是由HWRITE来控制的,而HWRITE是由主机产生的,故对从机SUM_RAM的读写时通过主机来控制的。

(4)内部详细设计:

这个模块为SUM_RAM模块,深度为1024,数据位宽为9位。

主要用于存储数据。

其中存储的数据是通过主机ADAPT模块实现RAM1及RAM2中的数据相加的和。

图12

3.4OUTPUT_BLOCK模块

(1)接口说明:

PIN

I/O

DISCRIBE

HCLK

I

时钟信号,为所有总线提供时基。

所有信号时序都和HCLK的上升沿相关。

HRESETn

I

系统的复位信号低有效并用来复位系统和总线,这是唯一的低有效的信号。

HBUSREQ_OUTPUT

I

OUTPUT_BLOCK模块产生的请求占用总线的信号,送入仲裁器,让其作出判断。

HGRANT_OUTPUT

I

授予信号由仲裁器产生并且表示相关主机是当前请求总线的主机中优先级最高的主机,优先考虑锁定传输。

HADDR_OUTPUT[31:

0]

O

32位系统地址总线。

HWRITE_OUTPUT

O

当为高表示一个写操作,为低表示一个读操作。

用于控制对从机的读写操作。

HTRANS_OUTPUT[1:

0]

O

表示当前传输的类型,可以是不连续,连续,空闲和忙。

HSIZE_OUTPUT[2:

0]

O

表示传输的大小,典型情况是字节(8位),半字(16位),或者是字(32位)。

协议允许最大的传输大小可以达到1024位。

HBURST_OUTPUT[2:

0]

O

表示传输是否组成了突发的一部分,支持四个,八个或者16个节拍的突发传输并且突发传输可以是增量或者是回环。

HWDATA_OUTPUT[31:

0]

O

写数据总线用在写操作期间从主机到总线从机传输数据,建议最小的数据总线宽度为32位,然而,在要求高宽带运行时扩展(数据总线)还是很容易的。

HREADY

I

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HRESP[1:

0]

I

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRDATA[31:

0]

I

读数据总线用来在读操作期间从总线从机向总线主机传输数据,建议最小的数据总线宽度为32位,然而在要求高宽带运行时扩展(数据总线)还是很容易的。

FULL_SUM

I

RAM_SUM的满信号,当SUM_RAM中满了,就可将其中的数据读出。

OUT_DATA

O

输出的加法和数据

OUT_VALID

O

写操作时能信号,当其为高电平,可以将RAM_SUM中的数据读出。

(2)接口框图;

图13

(3)内部详细设计:

图14

上图为output_block模块的状态机,根据上图我们可以看出:

当FULL_SUMRAM为高电平时READ_EN为高,此时output_block模块申请总线,当HGRANT_OUTPUT为高电平时,即仲裁器将总线权给OUTPUT_BLOCK模块,开始进入READ状态,之后一直处于READ状态,直到ADDR为32’h800003ff,才进入IDLE状态。

结束输出数据,放弃总线权。

这样就可以实现连续输出1024个加法和。

图15

根据上图我们可以看出:

当output_block模块进入read状态以后的下一个状态将产生的地址付给haddr_output,从而选定sum_ram模块,又由于HWRITE为低电平,故对RAM_SUM进行读操作,将值通过dout读出并通过拼接{23’b0,dout}传送入hrdata,最终读出里面的数据OUT_DATA;实现将sum_ram中的加法和连续输出。

3.5arbiter模块

(1)接口说明:

PIN

I/O

DISCRIBE

HCLK

I

时钟信号,为所有总线提供时基。

所有信号时序都和HCLK的上升沿相关。

HRESETn

I

系统的复位信号低有效并用来复位系统和总线,这是唯一的低有效的信号。

HBUSREQ_ADAPT

I

主机请求访问总线的信号,表示主机adapt_block请求访问总线。

HBUSREQ_OUTPUT

I

主机请求访问总线的信号,表示主机output_block请求访问总线。

HGRANT_ADAPT

O

授予信号由仲裁器产生并且表示相关主机是当前请求总线的主机中优先级最高的主机,优先考虑锁定传输。

HGRANT_OUTPUT

O

授予信号由仲裁器产生并且表示相关主机是当前请求总线的主机中优先级最高的主机,优先考虑锁定传输。

HADDR_ADAPT[31:

0]

I

32位系统地址总线。

由adapt_block模块产生的。

从adapt_block模块输入。

HADDR_OUTPUT[31:

0]

I

32位系统地址总线。

由output_block模块产生的。

HADDR[31:

0]

I

32位系统地址总线。

输出到总线上控制从机的读写地址。

HWRITE_ADAPT

I

当为高表示一个写操作,为低表示一个读操作。

用于控制对从机的读写操作。

由adapt_block模块产生。

HWRITE_OUTPUT

I

当为高表示一个写操作,为低表示一个读操作。

用于控制对从机的读写操作。

由output_block模块产生。

HWRITE

O

当为高表示一个写操作,为低表示一个读操作。

用于控制对从机的读写操作。

输出到总线上控制从机的读写。

HTRANS_ADAPT[1:

0]

I

表示当前传输的类型,可以是不连续,连续,空闲和忙。

从adapt_block模块输入。

HTRANS_OUTPUT[1:

0]

I

表示当前传输的类型,可以是不连续,连续,空闲和忙。

从output_block模块输入。

HTRANS[1:

0]

O

表示当前传输的类型,可以是不连续,连续,空闲和忙。

HSIZE_ADAPT[2:

0]

I

表示传输的大小,典型情况是字节(8位),半字(16位),或者是字(32位)。

协议允许最大的传输大小可以达到1024位。

从adapt_block模块输入。

HSIZE_OUTPUT[2:

0]

I

表示传输的大小,典型情况是字节(8位),半字(16位),或者是字(32位)。

协议允许最大的传输大小可以达到1024位。

从output_block模块输入。

HSIZE[2:

0]

O

表示传输的大小,典型情况是字节(8位),半字(16位),或者是字(32位)。

协议允许最大的传输大小可以达到1024位。

HBURST_ADAPT[2:

0]

I

表示传输是否组成了突发的一部分,支持四个,八个或者16个节拍的突发传输并且突发传输可以是增量或者是回环。

从adapt_block模块输入。

HBURST_OUTPUT[2:

0]

I

表示传输是否组成了突发的一部分,支持四个,八个或者16个节拍的突发传输并且突发传输可以是增量或者是回环。

从output_block模块输入。

HBURST[2:

0]

O

表示传输是否组成了突发的一部分,支持四个,八个或者16个节拍的突发传输并且突发传输可以是增量或者是回环。

输出给总线。

HWDATA_ADAPT[31:

0]

I

写数据总线用在写操作期间从主机到总线从机传输数据,建议最小的数据总线宽度为32位,然而,在要求高宽带运行时扩展(数据总线)还是很容易的。

从adapt_block模块输入。

HWDATA_OUTPUT[31:

0]

I

写数据总线用在写操作期间从主机到总线从机传输数据,建议最小的数据总线宽度为32位,然而,在要求高宽带运行时扩展(数据总线)还是很容易的。

从output_block模块输入。

HWDATA[31:

0]

O

写数据总线用在写操作期间从主机到总线从机传输数据,建议最小的数据总线宽度为32位,然而,在要求高宽带运行时扩展(数据总线)还是很容易的。

输出到总线。

(2)接口框图:

图16

(3)逻辑框图:

图17

(4)内部详细设计:

功能说明:

仲裁器被用来确保任意时刻只有一个主机能够访问总线,仲裁器的功能是检测许多不同的使用总线的请求和决定当前请求总线的主机中哪个的优先级最高。

然后将优先级高的主机所产生的HADDR,HWRITE,以及HWDATA放入总线。

在此次项目中,由于当ADD1_RAM和ADD2_RAM都写满后,ADAPT_BLOCK模块开始对其进行读操作,故此时要占用总线,此时我们根据实际情况规定ADAPT_BLOCK的优先级高,故ADAPT_BLOCK先占用总线,HGRANT_ADAPT先为高,当SUM_RAM模块写满以后,OUTPUT_BLOCK要求占用总线,此时又将总线权转交给OUTPUT_BLOCK模块。

完成输出SUMRAM中的数据的操作。

图18

上图为总线移交的过程。

我们可以看出先是ADAPT_BLOCK提出请求,仲裁器将总线权给了ADAPT_BLOCK模块,当ADAPT_BLOCK模块执行完毕,OUTPUT_BLOCK模块才开始占用总线。

3.6decoder模块

(1)接口说明

PIN

I/O

DISCRIBE

HCLK

I

时钟信号,为所有总线提供时基。

所有信号时序都和HCLK的上升沿相关。

HRESETn

I

系统的复位信号低有效并用来复位系统和总线,这是唯一的低有效的信号。

HADDR[31:

0]

I

从主机输出给从机的地址,用于选择相关地址。

32位系统地址总线。

HSEL_RAM1

O

用于选择SUM_RAM进行读写操作的选择信号。

HSEL_RAM2

O

用于选择SUM_RAM进行读写操作的选择信号。

HSEL_SUMRAM

O

用于选择SUM_RAM进行读写操作的选择信号。

HREADY

O

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HREADY_RAM1

I

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HREADY_RAM2

I

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HREADY_SUMRAM

I

当HREADY为高时表示总线上的传输已经完成,在扩展传输时该信号可能会被拉低。

HRESP[1:

0]

O

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRESP_RAM1[1:

0]

I

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRESP_RAM2[1:

0]

I

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRESP_SUMRAM[1:

0]

I

传输响应给传输状态提供了附加信息。

提供四种不同的响应:

OKEY,,ERROR,RETRY,SPLIT

HRDATA_RAM1[31:

0]

I

读数据总线用来在读操作期间从总线从机向总线主机传输数据,建议最小的数据总线宽度为32位,然而在要求高宽带运行时扩展(数据总线)还是很容易的。

HRDATA_RAM2[31:

0]

I

读数据总线用来在读操作期间从总线从机向总线主机传输数据,建议最小的数据总线宽度为32位,然而在要求

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- turbo51 AHB 总线 实现 加法 功能

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx