基本逻辑门电路.docx

基本逻辑门电路.docx

- 文档编号:4271050

- 上传时间:2022-11-28

- 格式:DOCX

- 页数:22

- 大小:351.18KB

基本逻辑门电路.docx

《基本逻辑门电路.docx》由会员分享,可在线阅读,更多相关《基本逻辑门电路.docx(22页珍藏版)》请在冰豆网上搜索。

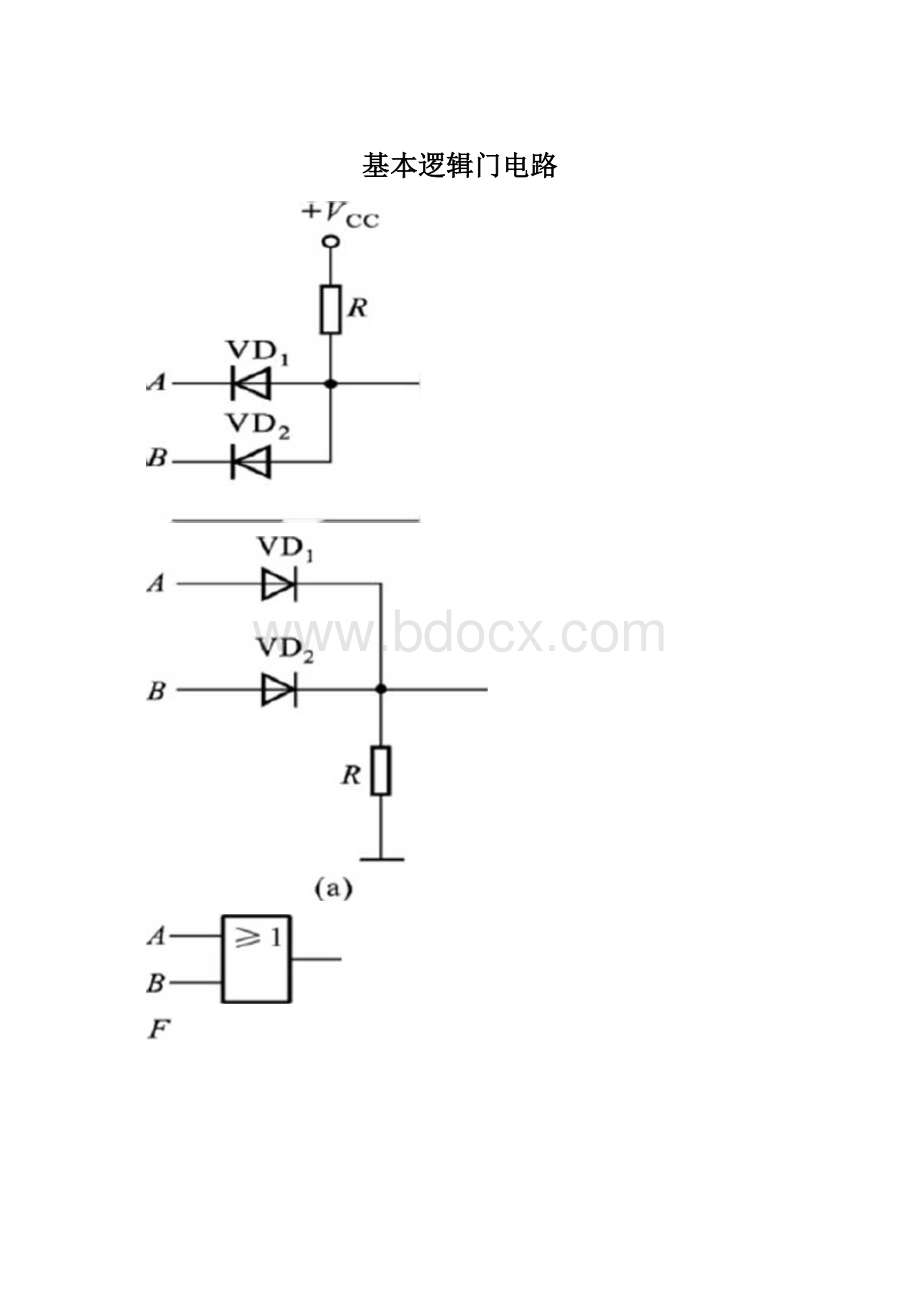

基本逻辑门电路

(b)

第一节基本逻辑门电路

1.1门电路的槪念:

实现基本和常■用逻辑运算的电子电路,叫逻辑门电路。

实现与运算•的叫与门,实现或运算的叫或门,实现非运算的叫非门,也叫做反相器,等等(用逻辑1表示高电平;用逻辑0表示低电平)

11.2与门:

逻辑表达式F二A5

TL

(a)(b)(c)

即只有当输入端A和B均为1时,输出端Y才为1,不然Y为0.与门的常用芯片型号有:

74LS08;74LS09等.

11.3或门:

逻辑表达武H

即当输入端A和B有一个为1时’输出端Y即为1,所以输入端A和B均为。

时,Y才会为0•或门的常用芯片型号有:

74LS32等._

1J•4.非门逻辑表送氐一Ff

即输出端总是与输入端相反•非门的常用芯片型号有,741504,?

LSO5,74LS06,74LS14等.

门・5•与非门逻辑表达式F二AB

即只有当所育输入端A和B均为1时,输出端Y才为0,不然Y为仁与非门的常用芯片型号有:

74LSOO,7403,74S742132等.

11・6•或非门:

逻辑表达式F=A+B

A——

>13—F

B——

即只要输入端A和B中有一个为]时,输出端丫即为0•所以输入端A和吕均为0时’丫才会为1•或非门常见的芯片型号有:

74LS02等.

11.7•同或门:

违辑表达式F#盼八B

B+AB

-B

11.9.与或彳

A

B

B

1L8.异丄

A

辑表达式F二AMCD

cQp

D

11.10.RS#

电路结构把两个与非门G1、G2的输入.输出端交叉连接,即可构成基本竺触发器,其逻辑电路如图

7.2.1.(Q所示。

它有两个输入端R、S和两个输出端4©—

工作原理:

Q诜

基本rs触发器的逻辑方程为:

&RQ

根据上述两个式子得到它的四种输入与输岀的关系:

1.当R=1、S=Q时,则Q=0,Q=1,触发器豊K2.当R=0、S=1时,则Q二1,B0,触发器置0。

如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q有两种互补的稳定状态。

一股规定触发器Q端的状态作为触发器的状态。

通常称触发器处于某种狀态,实际是指它的Q端的状态"Q二l、Q=0时称触发器处于1态,反之触发器处于0态。

S=0,R二1使触发器置1,或称置位。

因置位的决定条件是8=0,故称S端为置1端。

R=0,S=1时,使触发器置。

或祢复位。

同理,称尺歸为萱0端或复位端,若触发器原来为1态,欲使之变为0态,必须令R端的电平由1变D,S端的电平由0变1。

这里所加的输入信号(低电平)称为触发信号,由它们导致的转换过程称为稠转。

由干这里的触发信号是电平,因此这种触发器称为电平控制触发器。

从功能方面看,它只能在S和R的作用下苣0和直1,所以又祢尢豊0遂I触艮器,或称为宣位复位触发器。

其逻辑符号如图7.2.1(b)所示,由于置D或置1都是触发信号低电平有效,因此,S端和R端都画有小圆圈。

3.当R=S=1时,触发器状态保持不变。

触发器保持状态时,输入端都加非有效电平(高电平),需妥触发翻转时,要求在某一输入端加一负脉冲,例如在S端加负脉冲使触发器苣1,该脉冲信号回到高电平后,触发器仍维捲1状态不变,相当于把$端某一时刻的电平信号存皤起来,这体现了触发器具有记忆功能。

4.当R=S=O时,触发器状态不确定

在此条件下,两个与非门的输出端Q和Q全为1,在两个输入信号都同时撤去(回到1)后,由于两个与非门的延迟时间无魁确定,触发器的状态不能确定是1还是0,因此称这种情况为不定状态这种情况应当避免。

从另外一个角度来说,正因为R端和S端完成置0、置1都是低电平有效,所以二者不能同时为0。

此外,还可以用或非门的输入、输出端交叉连接构成置D、置1触发器,其逻辑图和逻辑符号分别如图八2.2(a)和¥.2.2Cb)所示。

这种触发器的触发信号是高电平有效,因此在逻辑符号的S端和R端没有小圆圈。

图7.2.2两或非门组成的基本RS触发器

2.特征方程

(S+*=l(約束条件》

表7.2.1基本RS斤竣器状态转移真值表

基本RS触发器的特性:

1.基本RS蝕发器具有置位、复位和保持(记忆〉的功能;

2.基本RS触发君的触•发信号是低电平有效,属于电平触发方式;

3.基本RS触发器存在约束条件®S二1),由于两个与非门的延迟时间无法确定;当R二S二0时,将导致下一状态的不确定。

4.当输入信号发生变化时,输出即刻就会发生相应的变化,即抗干扰性能较差。

第二节TTL逻辑门电路

以双极型半导体管为基本元件,集成在一块硅片上.并具有一定的逻辑功能的电路称为取极型逻辑集成电路,简称TTL逻辑门电路°Transistor-TransistorLogic,即BJT-BJT逻辑门电路,是数字电子技术中常用的一种逻辑门电路,应用较早,技•术已比较成熟。

TTL主要有BJT(BipolarJimctionTransistoi即双极结型晶体管,晶徉三极管)和电阻构成,具有速度快的特点。

最早的TTL门电路是74系列,后来出现了74H系列,74L系歹>J,74LS,74AS,74ALS系列。

但是由TTTL功耗大蒔缺.点,正逐渐被CMOS电路取代。

12.JCMOS逻辑门电路

CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改逬,CMOS电路的性能有可貶超越TTL而成为占主导地位的逻辑器件°CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL,此外,几乎所有的超大规模存储器件,以及PLD器件都釆用CMOS艺制造,且费用较低。

a早期主产的CM0S门电路为4000系列,随后发展为40OOB系列。

当前与TTL兼容的CMO器件如74HCT系列誓可与TTL器件交换使用。

下面首先讨i仑CMOS反相器,黙后介绍其他CMO逻辑门电路。

(b)电垢符号

(3)结构示总图

管结构閤

W0S

MOS管兰要参数:

仁开启电压VT

•开启电压(又称闻值电压):

使得源极S和漏极D之间开始形成导电沟道所需的桶极电压;

•标准的N沟道MOS管,VT约为3-6V;

•通过工艺上的改进,可以使MOS管的S值降到2-3vo

2.直流输入电阻Rgs

•即在栅濾极之间加的电压与栅极电流之比

•这一特性有时以流过柵极的栅流表朴MOS管的Rgs可以很容易地超过1010Q,

3.漏源击穿电压BV%

•在Vgs=O(增强型)的条件下,在增加漏源电压过程中使咕开始剧增时的\/出称为漏源击穿电压BVdsa比剧增的原因有下列两个方面:

(1)漏极附近耗尽层的雪崩击穿必

(2)漏源极间的穿通击穿必•有些MOS管中,其沟道长度较短,不断增加Vw会使漏区的耗尽层一宣扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后

,淚区中的多数载流子,将直接烫耗尽层电场的吸引,到达漏区,产生大的I。

4.栅源击穿电压BVgs

•在增•加栅源电压过程中,使栅极电流]G由零开始剧增时的Vgs,称为栅源击穿电压BVeg-

5.低频跨导g”•在V”为某一固定数值的条件下,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

-弘反映了栅源电压对漏极电流的控制能力

•是表征MOS管放大能力的一个重要蔘数:

》•—股在十分之几至几mAAZ的范围内

6.导通电阻Rog•导通电阻Ron说明了Vm对怙的影响,是漏极特性某一点切线的斜率的倒数

•在饱和区,Id几乎不随Vos改更Ron的数值很大,一般在几十千欧到几百千欧之间a•由于在数字电路中,MOS^导通时经常工作在Vds=0的状态下,所以这时的导通电阻Ron可用像点的Ron来近似

•对一股的MOS管而言,Ron的数值在几百欧以内

7.极间电替•三个电极之间都存在着极间电容:

栅源电容Cos•栅漏电容Cgd和漏源电容CD®・Cgs和Cgo约为1〜呂PF

•C”约在01-1pF之间

8.低频噪声系数NFq•噪声是由管子内部载協子运动的不规则性所引起的

亠•由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出

现不规则的电压或电流变化A•噪声性能的大小通常用噪声系数NF来表

示,它的单位为分贝(dB》•这个数值越小,代表管子所产生的噪声越小

A•低频噪声系数是在低频范围内测出的噪声系数丄•场效应管的噪声系数约为几个分贝,它比双极性三极管的艮小

第三节单元电路

13.1CMOS反相器

由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。

由N沟道和P沟道两种MOSFET组成的电路称为互补MOS或CMOS电路。

上下图表示CMOS反相器电路,由两只壇强型M0

SFET组成,其中一个为N沟道结构,另一个为P沟道结构。

为了电路能正常工作,要求电源电压vdd大于两个管子的开启电压的绝对值之和,&mD>(Vtn+IVtpI)。

简化电路

1.工作原理

首先考虑两种极限情况:

当VI处于逻辑0时,相应的电压近似为0V;

而当w处于逻辑1时,相应的电压近似対VDD.假设在两种情况下N沟道管Tn

为工作管P沟道管Tp为负载管,但是,由干电路是互补对称的,这种假设可以是

任惫的,相反的情况亦将导致相同的结果。

必T图分析了当vl=VDD时的工

作情况。

在TN的输出特性ID—VDS(V0SN=VDD)(注恿Vdsn=v。

)上,巷加一条负载线,它是负载管丁p在VgGP=0V时的输出特性iu-VsD。

由于Vsgp 两条曲线的交点即工作点。 显然,这时的输出电压vol^OV(典型值<10mV,而通过两管的电流接近于零。 这就是说,电路的功耗很小(微瓦量级) Vco 下国分析了另一种极限请况,此时对应于VI=0V.此时工作管0在Vgsn=0的信况下运用,其输出特性ID-VDS几平与橫轴重含,负载曲线是负载管Tp在vsGP=Vdd时的输出特性1D—VDS»由图可知’工作点决定了VquVohuVdd;通过两器件的电流接近零值O可见上述两种极限情况下的功耗都很低。 由此可知,基本CMOS反相器近似于一理想的逻辑苴元,其输出电压接近于零或也皿而功耗几乎为零。 2.传输特性 下图为CMOS反相器的传输特性图。 国中Vdd=10V,Vtn=IVtp|=Vt=2Vo由于\/odA(Vtz+VtpI),因此,当Vqd-|Vip|>vI>Vtn时,Tz和Tp两管同时导通。 考虑到电路是互补对称的,一器件可将另一器件视为它的漏极负载"还应注意到,器件在放大区(饱和区)呈现恒流待性,两器件之一可当作高阻憤的负载。 因此,在过渡区域,传输特性变化比较怎剧,两管在Vi=Vdd/2处转换狀态。 vqW Tn鐵止, 严一Tn在饱和区 Yoh~VddIO A Tp在可变电阻区 8 一 B' Tn和Tp均在饱和区 6 / 4 一 - cTp在饱和区 2 — \/-Tn在可变电阻区 %处OLH 246810 3一工作速度 CMOS反柑器在电容负载情况丁,它的开通时间与关阳时间是相等的,这是因対电路具有互补对称的性质。 下图表示当时,Tz截止,Tp导通,由V"通过Tp向负载电容Cl充电的惜況。 由干CMOS反相器中,两管的g“值均设计得较大,其导通电阻较小,充电回珞的时间常数较小。 类似地,亦可分析电容Cl的放电过程。 CMOS反相器的平均传输延迟时间约为10ns。 13.2CMOS逻辑门电路 1.与非门电路 下图是2瑜入端CMOS与非门电路,其中包括两个串联的N沟道堆强型MOS管和两个并联的P洶道増强型M0S簷。 每个输入端连到一个N沟道和一个R沟道MOS管的栅极。 当输入端A、B中只要有一个为低电平时,就会使与它相连的NMOS止,与它相连的PMOSW导通,输出为高电平;仅 当A、日全为高电平时,才会使两千串联的NMOS管都导通,使两个并联的PMOS管都截止,输出为低电平。 因此,这种电路具有与非的逻辑功能,即n个辎入端的与非门必须有c个NMOS管串联和n^PMQS管并联。 2•或非门电路 下图是2瑜入端CMOS或非门屯路。 其中包括两个并联的N沟道培强型MOS管和两个串联的P沟道增强型MOS管。 当输入端A、B中只更有一个为高电平时,就会使与它相连的NMOS管导通,与它相连的PMOS管截止,输出为低电平: 仅当A、B全为低电平时,两个并联NMOS管都截止,两个串联的PMOS管都导通,输出为高电平’ 因此,这种电路具有或非的逻辑功能,其逻辑表达式为L-乔® 显然,n个输入端的或非门必须有n个NMOS管并联和n个PMOS管并联。 上比较CMOS与非门和或非门可知,与非门的工作管是彼此串联的,其输出电压随管子个数的培加而培加: 或非门则相反,工作管彼此并联,对输出电压不致有明显的彫响。 因而或非门用得较多。 13.3.#或门电路 上團为CMOS异或门电路。 它由一级或非门和一级与或非门组成。 或非 门的输出X而与或非门的输出L即为输入A、B的异或 L=A•B+X =力・B+A+B =力・B+A-B =A®B 如在异或门的后面增加一级反相器就构成异或非门,由 于具有匚==月送+刁的功能,因而称为同或门。 异成门和同或门的逻辑符号 如下图所示. L=AQLi 同或门 异或门 13.4BiCMOS门电路 双极型CMOS或BiCMOS的侍点在于,利用了取极型器件的速度快和 MOSFET旳功耗低两方面的优势,因而这种逻辑门电路受到用户的重视 1.BiCMOS反相器 Voo(5V) 上图表示基本的BiCMOS反相器电路,为了淸楚起见諦OSFET用符号IV1表示BJT用丁表示。 「和丁2构成推拉式输出级。 而Mp、Mw.Mi、IVI2所组成的输入级与基本的CMOS反相器很相似。 输入信号w同时作用于Mp和Mn的栅极。 当r为高电压时Mn导通而Mp截止;而当V|为低电压时,情况则相反%导通,%截止Q当緇出端接有同类BiCMOS门电路时,输出级能提供足够大的电流为电容性负载充电。 同理,己充电的电容负载也能迅速地通过T2放电。 上述电路中Ti和丁2的基区存储电荷亦可通过和IVL释放,以加快亠电路的开关速度。 当W为高电压时g导通,Tj基区的存储电荷迅速消散。 这种作用与TTL门电路的输入级中「类似。 同理,当w为低电压吋,电源电压Vdd通过Mp以撤励M使IVk导通,显燃T2基区的存储电荷通过卜(2而消散。 可见,门电路的开关速度可得到改善。 2.BiCMOS门电路 根据前述的CMOS门电路的结构和工作原理,同样可以用BiCMOS技术实现或非门和与非门。 如果要丈现或非逻辑关系,输入信号用来驱动并联的N沟道MOSFET,而P沟道MOSFET则彼此串联。 正如下图所示抄2输入端或非门。 当A和B均为低电平时,则MOSFETMPA和均导通,「导通而皿“和Wb均截止,输出L为高电平。 与此同时,通过fVU和“阳被Vw所做励,从而为T2的基区存储电荷提供一条释放通路。 >另一方面,当两输入端A和B中之一为高电平时,则皿人和M°b的通路被断开,并且匾仏或岡忧导通,将使输出端为低电平。 同时.M仆或M汨为「的基极存储电荷提供一条释放道路.因此,只要有一个输入端接高电平,辅出即为低电平。 13.5、CMOS传输门 MOSFET的输出特性在原.点附近呈线性对称关系侶而它们常用作稹拟开关。 模拟开关广泛地用于取样——保持电路、斩波电路、模数和数模转换电路等。 丁面着重介绍CMOS传输门。 -5V 111 vo/vf 所谓传输门(TG)就是一种传瑜模拟信号的模拟开关。 CMOS传输门由一个P沟道和一个N沟道增强型MOSFET并联而成如上图所示。 Tp和Tn是结构对称的器件,它们的漏极和源极是可互换的。 设它们的开启电压|Vt|=2V且输入模拟信号的变化范围为・5V到+5V°为便衬底与漏源极之间的PN结任何时刻都不致正偏,故Tp的衬底接+5V电压,而Tn的衬底接《5V电压。 两管的栅极由互补的信号电压(+5V和-5V)来控制,分别用C和°表示. 传输门的工作情况如下: 当C端接低电压一5V时0的栅压即为・5V,v[取・5V到+5V范围内的任意值时,丁! m均不导通。 同时,Tp的栅压为+5V^,TP亦不导通。 可见,当C端接低电压时,开关是斷开旳。 >为使开关接通,可将C端接高电压+5VD此时TN的栩压为+5Vm在・5V到+3V的范围内,儿导通。 同时Tp的棚压为・5V,vi在到+5V的范国内Tp将导通。 由上分析可知,当v,<-3V时,仅有g导通,而当W>+3V时,仅有Tp导通当5在■3V到+3V的范围内,Tn和Tp两管均导通。 进一步分析还可看到,一管导通的程度愈深,另一管的导通程度则相应地减小。 换句话说,当一管的导通电阻减小,则另一管的导通电阻就增加。 由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。 这是CMOS传输出门的优点。 在正常工作时,模拟开关的导通电阻值约为数百欧,当它与输入阻抗为兆欧级的运放串接时,可以忽略不计。 CMOS传输门除了作为传输模拟信号的开关之外,也可作为各种逻辑电賂的基本单元电路。 13.6整痢电路 桥式整流电琏 13.7谑波电路 (a)e)(c) (a)C型滤波电路 (b)慳儿型滤波电路 (c) 】】型滤波电路 图1 (3)几种常见的桥式整流谑波电路: A电容滤波电路, ctcrN B电感滤波电路 13.8.反馈电路 1.正反馈: 是指反馈回来的信号增强输入信号(常用与振荡电路〉; 负反馈: 是指反馈回来的信号削弱原输入信号(用与放犬电路人 2.判别正负反馈的方法一一瞬时极性法 "瞬时极性法“是用来判断正反馈还是负反馈的。 我们在放大器输入端的基极施加一个信号电压VI,设某一瞬时该信号的极性为正信号,用”(+)”表示,经三极管V的集电极倒相后变为负信号,用气-y来表示。 发射极与基极同相位,仍为”(+)■信号,多级放大器在这一瞬时的极性依次类推,假设在这一瞬时反馍电阻RF的反馈信号使输入信号加强,则为正反馈•’使得输入信号削弱,则为负反馈。 1.负反僮放大电路的四种类型: A电压串轶负反馈B电压并疲负反馈 C电流串联负反馈D电流并联负反馈 13.9放大电路 三种基本组态的放大电路图: 共发射极放大电路 注意: 放大电路共发射极时,A1和Au都比较大,但是辎出电压和辅入电压的相位相反: 共基极时,Ai比较大,但是Au较小,输出电压与输入电压同相,并且具有跟随关系,它可作为输入级,输出级或起隔离作用的中间级: 共集电极时、Ai较小,AII较大,输出电压与输入电压同相,多用于竟频带放大等。 对于多级放电电路: 在多级放大器中,由于各级之间是串联起来的,后一级的输入电阻就是前级的负载,所以,多级放大器的总电压放大倍数等于各级放大倍数的乘积,即Au=AuiAu2……A^C, 注臥若反馈信号取自辎出电压宿号则称为电压反馈;若反馈信号取自辅出电流信邑则称为电流反馈。 [通舗釆用将负载电阻短路的方法来判别电压反馈和电流反绩。 具体方法足: 若将负载电阻RL短路,如果反馈作用消失,则为电压反馈;如果反馈作用存在,则为电流反馈。 ); 若反锁信号与输入信号在基本放大电路的输入端以电压串联的形式迭加,则称为串联反馈;若反馈信号与输入信号在基本放大輕的输入端以电流并联的形式迭加,则称为并联反馈D 13.10.振荡电路 K电感三点式振荡器 考虑S、a间的互感,电路的振荡频率可近似表示为 f&= °2兀伍2%J(厶+厶+22/疋 f*■ 振荡频率m°GG

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基本 逻辑 门电路

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx