组合逻辑电路仿真.docx

组合逻辑电路仿真.docx

- 文档编号:4125608

- 上传时间:2022-11-28

- 格式:DOCX

- 页数:14

- 大小:364.44KB

组合逻辑电路仿真.docx

《组合逻辑电路仿真.docx》由会员分享,可在线阅读,更多相关《组合逻辑电路仿真.docx(14页珍藏版)》请在冰豆网上搜索。

组合逻辑电路仿真

组合逻辑电路仿真

一、组合逻辑电路的分析

本次仿真实验要求对两个问题进行仿真模拟:

1、设计一个四人表决电路,在三人以上同意时灯亮,否则灯灭。

并要求采用与非门实现。

2、设计一个4位二进制码数据X围指示器,要求能够区分0≤X≤4、5≤X≤9、10≤X≤15三种情况,同样要求采用与非门实现。

下面先对两个问题进行逻辑化分析。

1、四人表决电路

在本问题中,很容易就可以看出问题的核心在于“四个人的表决意见决定灯的亮与灭”。

所以该问题的输入变量是四个人的表决意见,输出变量为灯的亮灭。

以A、B、C、D分别表示四个人的意见为“同意”,以它们的非表示“不同意”。

而以F来表示灯处于“亮”的状态。

则“三人以上同意时灯亮,否则灯灭”可以很容易的用以下逻辑表达式来表示:

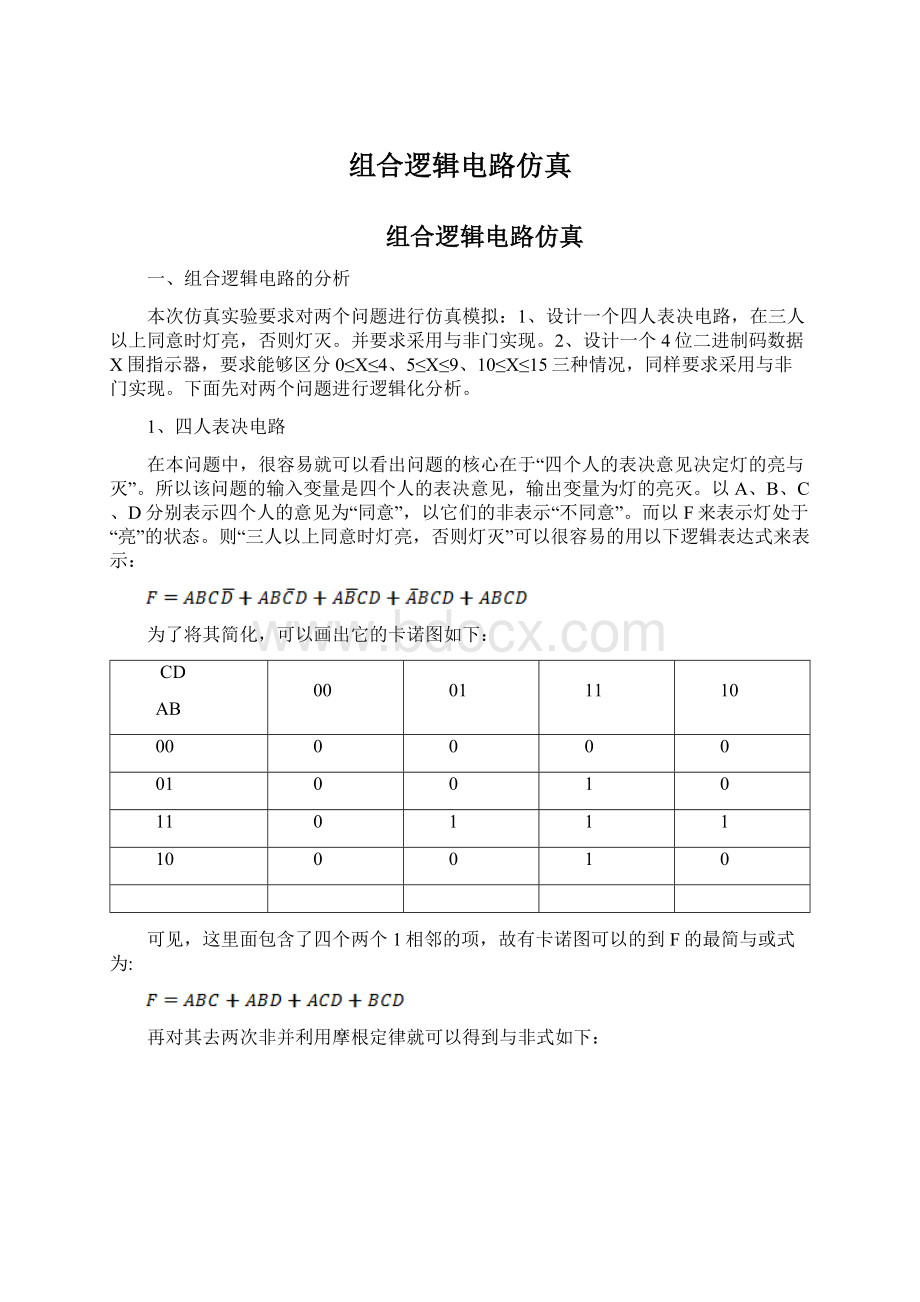

为了将其简化,可以画出它的卡诺图如下:

CD

AB

00

01

11

10

00

0

0

0

0

01

0

0

1

0

11

0

1

1

1

10

0

0

1

0

可见,这里面包含了四个两个1相邻的项,故有卡诺图可以的到F的最简与或式为:

再对其去两次非并利用摩根定律就可以得到与非式如下:

这就是第一个问题的逻辑转化。

2、4位二进制码数据X围指示器

四位二进制码可以表示十进制下的0到15这十六个数,按照0≤X≤4、5≤X≤9、10≤X≤15分为三组分别用三个灯的亮灭来代表输入的二进制码属于其中的哪一组。

同上例,采用A、B、C、D取0或1依次表示这四位二进制码的从高到低位的取值(例如:

A=0,B=1,C=0,D=0表示四位二进制码0100)。

则对于第一组来说,共有5个四位二进制码包含在其中,用卡诺图表示如下:

CD

AB

00

01

11

10

00

1

1

1

1

01

1

0

0

0

11

0

0

0

0

10

0

0

0

0

化简即得:

同理,也有5个数包含在第二组中,卡诺图如下:

CD

AB

00

01

11

10

00

0

0

0

0

01

0

1

1

1

11

0

0

0

0

10

1

1

0

0

化简即得:

第三组包含了6个数,卡诺图如下:

CD

AB

00

01

11

10

00

0

0

0

0

01

0

0

0

0

11

1

1

1

1

10

0

0

1

1

化简即得:

对以上三个式子都去两次非并利用摩根定律可得:

这样就完成了第二个问题的逻辑转化。

二、组合逻辑图及模拟结果

1、本问题的输出量只有一个,表达式也已经表示成了与非式,因此,其逻辑图可以很容易的通过Multisim软件模拟画出,如下:

这里我用了4个开关来作为四个输入变量的控制量,即第n个开关“开”表示第n个人“同意”;用灯泡的亮灭来代表输出(题目中要求三人以上同意时灯亮);则应有三个以上开关闭合时灯亮,否则灯灭。

可能的输入情况有:

0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100、1101、1110、1111共16种情况,可能情况比较多下面就不把模拟结果做一一展示了,只选取其中有代表性的四种情况进行展示。

模拟情况如下:

1)四个开关都断开,表示四人都不同意,灯灭。

2)只有开关B闭合,表示只有B一个人同意,灯灭。

3)有两个开关(A、C)闭合,表示A、C两个人同意,灯灭。

4)有三个开关(A、B、D)闭合,表示A、B、D三个人同意,灯亮。

5)四个开关都闭合,表示四个人都同意,灯亮。

2、根据前面对本问题分析所得到的逻辑表达式:

可以发现,输入变量为A、B、C、D,但是在后面的逻辑运算中它们的“非”都用到了,也就是第一步我们要得到这四个变量的非。

然后再进行后面的与非运算。

三个输出变量的状态也可以用三个灯泡来表示,这里采用了三个颜色不同的灯泡用以区分。

到这里,逻辑图就可以很容易的用Multisim软件模拟出来:

其中,最上面的X1灯泡亮时,表示输入数字在0≤X≤4X围内,X2亮时表示输入数字在5≤X≤9X围内,X3亮时表示输入数字在10≤X≤15X围内。

这里我还是用了四个开关,每个开关“开”表示1,“关”表示0,四个开关以ABCD的顺序来表示四位二进制数。

四位二进制数同上,也有16中情况,这里不做一一展示,只对每一类给出一种模拟结果。

模拟结果如下:

1)0≤4≤4,灯泡X1亮,其它灭。

2)5≤8≤9,灯泡X2亮,其它灭。

3)10≤15≤15,灯泡X3亮,其它灭。

三、电路功能情况

两个问题中的符号表示都与上面模拟中保持相同,则电路功能情况可以用如下的功能表(真值表)来表示:

第一个问题的功能表如下:

A

B

C

D

F

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

0

0

1

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

0

1

1

1

1

1

1

第二个问题的功能表如下:

A

B

C

D

F1

F2

F3

0

0

0

0

1

0

0

0

0

0

1

1

0

0

0

0

1

0

1

0

0

0

0

1

1

1

0

0

0

1

0

0

1

0

0

0

1

0

1

0

1

0

0

1

1

0

0

1

0

0

1

1

1

0

1

0

1

0

0

0

0

1

0

1

0

0

1

0

1

0

1

0

1

0

0

0

1

1

0

1

1

0

0

1

1

1

0

0

0

0

1

1

1

0

1

0

0

1

1

1

1

0

0

0

1

1

1

1

1

0

0

1

四、电路的优化

在上面对第二个问题的分析和模拟的过程中,可以很明显的发现“三个灯泡始终有且仅有一个是亮着的”,根据这一特点并考虑到电路输出其实只有三个状态(若果用二进制数表示只需两位),所以可以对电路进行简化。

简化的方法可以用如下的表格来表示:

X

F1

F2

F3

0≤X≤4

1

0

0

5≤X≤9

0

1

0

10≤X≤15

0

0

1

输入的三个状态用后面F1、F2、F3的状态来代表,如果把F3一列去掉,则变为:

X

F1

F2

0≤X≤4

1

0

5≤X≤9

0

1

10≤X≤15

0

0

可以发现,只用F1、F2的状态也可以表示电路的这三种状态(与两位二进制数表示三种状态原理相同)。

所以可以删去原先电路中的一个灯泡。

为使电路中用到的门个数达到最少,可以删掉电路中与X2相连的那一系列电路(这一系列包含的门数最多,删掉后电路保留的门数最少)。

得到的电路如下:

模拟结果变为:

1)0≤4≤4

2)5≤8≤9

3)10≤15≤15

相应的功能表也发生变化:

A

B

C

D

F1

F3

0

0

0

0

1

0

0

0

0

1

1

0

0

0

1

0

1

0

0

0

1

1

1

0

0

1

0

0

1

0

0

1

0

1

0

0

0

1

1

0

0

0

0

1

1

1

0

0

1

0

0

0

0

0

1

0

0

1

0

0

1

0

1

0

0

1

1

0

1

1

0

1

1

1

0

0

0

1

1

1

0

1

0

1

1

1

1

0

0

1

1

1

1

1

0

1

五、组合逻辑电路采用的元器件

本实验要求只采用与非门来实现电路功能,而由第一部分的分析可以看出,全部电路只涉及到两输入与非门、三输入与非门、四输入与非门以及非门。

而非门又可以通过与非门的输入端输入相同变量来实现非门的功能,故而本实验可以只由这三种与非门来实现。

所采用的元器件自然选择集成了4个两输入与非门的74LS00、集成了3个三输入与非门的74LS10和集成了2个四输入与非门的74LS20芯片。

74LS00芯片的引脚逻辑图如下:

74LS10芯片的引脚逻辑图如下:

图中的

表示的是三输入的与非门(国际标准)。

74LS20芯片的引脚逻辑图如下:

同样,图中的

表示的是四输入的与非门(国际标准)。

在第一个问题中,从模拟的电路图来看,三输入与非门用到了四个,四输入与非门用到了1个,根据74LS10和74LS20芯片的引脚图,可以确定实现这个电路功能需要2个74LS10和1个74LS20。

在第二个问题中,从优化后的模拟电路图来看,必须用到的两输入与非门有5个,必须用到的三输入与非门有1个,还有四个非门可以用任意一种与非门实现。

根据74LS00和74LS10芯片的引脚图,可以确定实现这个电路功能需要2个74LS00和1个74LS10。

具体的接线图可以根据逻辑图自由发挥,这里就不再详述了。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 组合 逻辑电路 仿真

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx