VHDL数字钟设计报告001.docx

VHDL数字钟设计报告001.docx

- 文档编号:3974740

- 上传时间:2022-11-26

- 格式:DOCX

- 页数:17

- 大小:165.42KB

VHDL数字钟设计报告001.docx

《VHDL数字钟设计报告001.docx》由会员分享,可在线阅读,更多相关《VHDL数字钟设计报告001.docx(17页珍藏版)》请在冰豆网上搜索。

VHDL数字钟设计报告001

VHDL数字钟设计报告

一.数字钟总体设计方案:

1.1设计目的

正确显示时、分、秒;

可手动校时,能分别进行时、分的校正;

整点报时功能;

1.2设计思路

数字钟的设计模块包括:

分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路、整点报时和译码显示电路。

每一个功能模块作为一个实体单独进行设计,最后再用VHDL的例化语句将各个模块进行整合,生成顶层实体top。

该数字钟可以实现3个功能:

计时功能、设置时间功能和报时功能。

二.数字钟模块细节

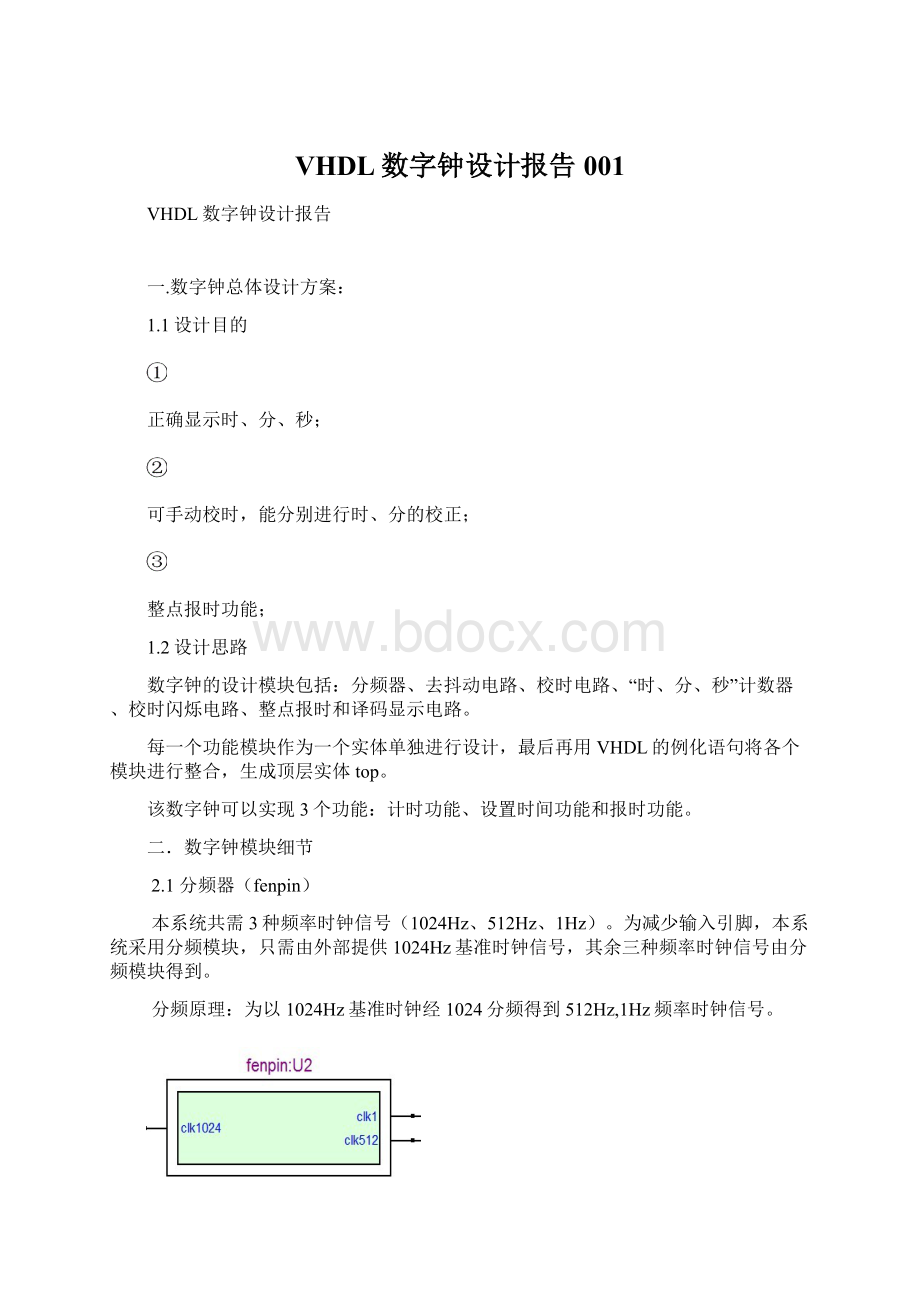

2.1分频器(fenpin)

本系统共需3种频率时钟信号(1024Hz、512Hz、1Hz)。

为减少输入引脚,本系统采用分频模块,只需由外部提供1024Hz基准时钟信号,其余三种频率时钟信号由分频模块得到。

分频原理:

为以1024Hz基准时钟经1024分频得到512Hz,1Hz频率时钟信号。

分频器管脚

代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.std_logic_arith.all;

entityfenpinis

port(clk1024:

instd_logic;

clk1,clk512:

outstd_logic

);

endfenpin;

architecturecmloffenpinis

begin

process(clk1024)

variablecount1:

integerrange0to512;

variableq1:

std_logic;

begin

ifclk1024'eventandclk1024='1'then

ifcount1=512then

q1:

=notq1;

count1:

=0;

else

count1:

=count1+1;

endif;

endif;

clk1<=q1;

endprocess;

process(clk1024)

variablecount512:

integerrange0to1;

variableq512:

std_logic;

begin

ifclk1024'eventandclk1024='1'then

ifcount512=1then

q512:

=notq512;

count512:

=0;

else

count512:

=count512+1;

endif;

endif;

clk512<=q512;

endprocess;

endcml;

2.2校时电路(jiaoshi)

本模块要实现的功能是:

正常计时、校时、校分在每个状态下都会产生不同控制信号实现相应的功能。

校时管脚图

代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityjiaoshiis

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:

instd_logic;

hclkout,mclkout:

outstd_logic

);

endjiaoshi;

architecturecmlofjiaoshiis

signalh_m:

std_logic;

begin

p1:

process(rst,rvs,hclkin,mclkin,h_m,mtime)

begin

ifrst='0'then

null;

elsifrvs='1'then

hclkout<=hclkin;

mclkout<=mCLKin;

elsifh_m='0'then

hclkout<=hclkin;

mclkout<=mtime;

else

hclkout<=mtime;mclkout<=mclkin;

endif;

endprocess;

p2:

process(select_rvs)

begin

ifselect_rvs'eventandselect_rvs='1'then

h_m<=noth_m;

endif;

endprocess;

endcml;

管脚图

仿真图

2.3时计数器(hour)分计数器(mine)秒计数器(second)

时计数器管脚图

时代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityhouris

port(rst,hclk:

instd_logic;

hour0,hour1:

bufferstd_logic_vector(3downto0)

);

endhour;

architecturecmlofhouris

begin

process(rst,hclk,hour0,hour1)

begin

ifrst='0'then

hour0<="0000";

hour1<="0000";

elsifhclk'eventandhclk='1'then

ifhour0="0011"andhour1="0010"then

hour0<="0000";

hour1<="0000";

elsifhour0="1001"then

hour0<="0000";

hour1<=hour1+1;

else

hour0<=hour0+1;

endif;

endif;

endprocess;

endcml;

分计数器管脚图

分代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitymineis

port(rst,mclk:

instd_logic;

mco:

outstd_logic;

min0,min1:

bufferstd_logic_vector(3downto0)

);

endmine;

architecturecmlofmineis

signalmin0_t,min1_t:

std_logic_vector(3downto0);

begin

process(rst,mclk,min0,min1)

begin

ifrst='0'then

min0<="0000";

min1<="0000";

elsifmclk'eventandmclk='1'then

ifmin0="0101"andmin1="1001"then

min0<="0000";

min1<="0000";

mco<='1';

elsifmin0="0010"andmin0="1001"then

min1<="0011";

min0<="0000";

mco<='0';

elsifmin0="1001"then

min1<=min1+1;

min0<="0000";

else

min0<=min0+1;

endif;

endif;

endprocess;

endcml;

秒计数器管脚图

秒代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitysecondis

port(rst,sclk:

instd_logic;

sco:

outstd_logic;

sec0,sec1:

bufferstd_logic_vector(3downto0)

);

endsecond;

architecturecmlofsecondis

signalsec0_t,sec1_t:

std_logic_vector(3downto0);

begin

process(rst,sclk,sec0,sec1)

begin

ifrst='0'then

sec0<="0000";

sec1<="0000";

elsifsclk'eventandsclk='1'then

ifsec0="0101"andsec1="1001"then

sec0<="0000";

sec1<="0000";

sco<='1';

elsifsec0="0010"andsec0="1001"then

sec1<="0011";

sec0<="0000";

sco<='0';

elsifsec0="1001"then

sec1<=sec1+1;

sec0<="0000";

else

sec0<=sec0+1;

endif;

endif;

endprocess;

endcml;

2.4校时闪烁电路(flashnjiaoshi)

如果正在进行校时,flashjiaoshi将实现使当前正在校时项(小时或分钟)以1Hz的频率闪烁,以便于操知道正在被校正。

校时闪烁电路管脚图

代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityflashjiaoshiis

port(rst,sclk,rvs,select_rvs:

instd_logic;

hour0in,hour1in,min0in,min1in:

instd_logic_vector(3downto0);

hour0out,hour1out,min0out,min1out:

outstd_logic_vector(3downto0)

);

endflashjiaoshi;

architecturecmlofflashjiaoshiis

signalh_m:

std_logic;

begin

p1:

process(rst,sclk,rvs,hour0in,hour1in,min0in,min1in,h_m)

begin

ifrst='0'then

null;

elsifrvs='1'then

hour0out<=hour0in;

hour1out<=hour1in;

min0out<=min0in;

min1out<=min1in;

elsifh_m='0'then

hour0out<=hour0in;

hour1out<=hour1in;

ifsclk='1'then

min0out<=min0in;

min1out<=min1in;

else

min0out<="1111";

min1out<="1111";

endif;

else

min0out<=min0in;

min1out<=min1in;

IFsCLK='1'then

hour0out<=hour0in;

hour1out<=hour1in;

else

hour0out<="1111";

hour1out<="1111";

endif;

endif;

endprocessp1;

p2:

process(select_rvs)

begin

ifselect_rvs'eventandselect_rvs='1'then

h_m<=noth_m;

endif;

endprocessp2;

endcml;

2.5整点报时电路

整点报时管脚图

代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitybaoshiis

port(clk1024,clk512:

instd_logic;

min0,min1,sec0,sec1:

instd_logic_vector(3downto0);

speak:

outstd_logic);

endbaoshi;

architecturecmlofbaoshiis

begin

speak<=clk512

when(min1="0101"andmin0="1001"andsec1="0101")and(sec0="0011"orsec0="0101"orsec0="0111")else

clk1024

when(min1="0101"andmin0="1001"andsec1="0101"andsec0="1001")else'0';

endcml;

2.6译码显示电路

该显示用的是动态扫描电路

译码显示管脚图

波形图

代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityxianshiis

port(clk512:

instd_logic;

h1,h0,m1,m0,s1,s0:

instd_logic_vector(3downto0);

seg7:

outstd_logic_vector(6downto0);

select_sig:

outstd_logic_vector(5downto0)

);

endxianshi;

architecturecmlofxianshiis

signaldata:

std_logic_vector(3downto0);

signalorder:

std_logic_vector(2downto0);

begin

process(clk512)

begin

ifclk512'eventandclk512='1'then

caseorderis

when"000"=>data<=h1;select_sig<="011111";

when"001"=>data<=h0;select_sig<="101111";

when"010"=>data<=m1;select_sig<="110111";

when"011"=>data<=m0;select_sig<="111011";

when"100"=>data<=s1;select_sig<="111101";

when"101"=>data<=s0;select_sig<="111110";

whenothers=>data<="1000";select_sig<="111111";

endcase;

iforder="101"thenorder<="000";

elseorder<=order+1;

endif;

endif;

endprocess;

process(data)

begin

casedatais

when"0000"=>seg7<="0000001";

when"0001"=>seg7<="1001111";

when"0010"=>seg7<="0010010";

when"0011"=>seg7<="0000110";

when"0100"=>seg7<="1001100";

when"0101"=>seg7<="0100100";

when"0110"=>seg7<="0100000";

when"0111"=>seg7<="0001111";

when"1000"=>seg7<="0000000";

when"1001"=>seg7<="0000100";

whenothers=>seg7<="1111111";

endcase;

endprocess;

endcml;

2.7数字钟整体设计(top)

本数字钟的设计包括分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路和译码显示电路。

以上已经有了各个功能模块的实现方法,现在将各个模块综合在一起,构成一个完整的数字钟。

代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitytopis

port(clk1024,key,reset:

instd_logic;

keyin:

instd_logic_vector(1downto0);

select_sigout:

outstd_logic_vector(5downto0);

seg7out:

outstd_logic_vector(6downto0);

speak:

outstd_logic

);

endtop;

architecturecmloftopis

componentfenpinis

port(clk1024:

instd_logic;

clk1,clk512:

outstd_logic

);

endcomponentfenpin;

componentjiaoshiis

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:

instd_logic;

hclkout,mclkout:

outstd_logic

);

endcomponentjiaoshi;

componenthouris

port(rst,hclk:

instd_logic;

hour0,hour1:

bufferstd_logic_vector(3downto0)

);

endcomponenthour;

componentminuteis

port(rst,mclk:

instd_logic;

mco:

outstd_logic;

min0,min1:

bufferstd_logic_vector(3downto0)

);

endcomponentminute;

componentsecondis

port(rst,sclk:

instd_logic;

sco:

outstd_logic;

sec0,sec1:

bufferstd_logic_vector(3downto0)

);

endcomponentsecond;

componentflashjiaoshiis

port(rst,sclk,rvs,select_rvs:

instd_logic;

hour0in,hour1in,min0in,min1in:

instd_logic_vector(3downto0);

hour0out,hour1out,min0out,min1out:

outstd_logic_vector(3downto0)

);

endcomponentflashjiaoshi;

componentxianshiis

port(clk512:

instd_logic;

h1,h0,m1,m0,s1,s0:

instd_logic_vector(3downto0);

seg7:

outstd_logic_vector(6downto0);

select_sig:

outstd_logic_vector(5downto0)

);

endcomponentxianshi;

componentbaoshiis

port(clk1024,clk512:

instd_logic;

min0,min1,sec0,sec1:

instd_logic_vector(3downto0);

speak:

outstd_logic);

endcomponentbaoshi;

signalscanCLKSig:

std_logic;

signalsecCLKSig:

std_logic;

signalhCLKSig0,hCLKSig1:

std_logic;

signalmCLKSig0,mCLKSig1:

std_logic;

signalsec1Sig,sec0Sig:

std_logic_vector(3downto0);

signalmin1Sig0,min0Sig0:

std_logic_vector(3downto0);

signalmin1Sig1,min0Sig1:

std_logic_vector(3downto0);

signalhour1Sig0,hour0Sig0:

std_logic_vector(3downto0);

signalhour1Sig1,hour0Sig1:

std_logic_vector(3downto0);

begin

U1:

fenpinPORTMAP(clk1024=>clk1024,clk512=>scanCLKSig,clk1=>secCLKSig);

U2:

jiaoshiPORTMAP(rst=>reset,rvs=>key,select_rvs=>keyin(0),

mtime=>keyin

(1),

hclkin=>hCLKSig0,mclkin=>mCLKSig0,hclkout=>hCLKSig1,mclkout=>mCLKSig1);

U3:

hourPORTMAP(rst=>reset,hCLK=>hCLKSig1,hour1=>hour1Sig0,

hour0=>hour0Sig0);

U4:

minutePORTMAP(rst=>reset,mclk=>mCLKSig1,mco=>hCLKSig0,

min1=>min1Sig0,min0=>min0Sig0);

U5:

secondPORTMAP(rst=>reset,sCLK

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- VHDL 数字 设计 报告 001

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx