与非门实验步骤.docx

与非门实验步骤.docx

- 文档编号:3902221

- 上传时间:2022-11-26

- 格式:DOCX

- 页数:17

- 大小:916.18KB

与非门实验步骤.docx

《与非门实验步骤.docx》由会员分享,可在线阅读,更多相关《与非门实验步骤.docx(17页珍藏版)》请在冰豆网上搜索。

与非门实验步骤

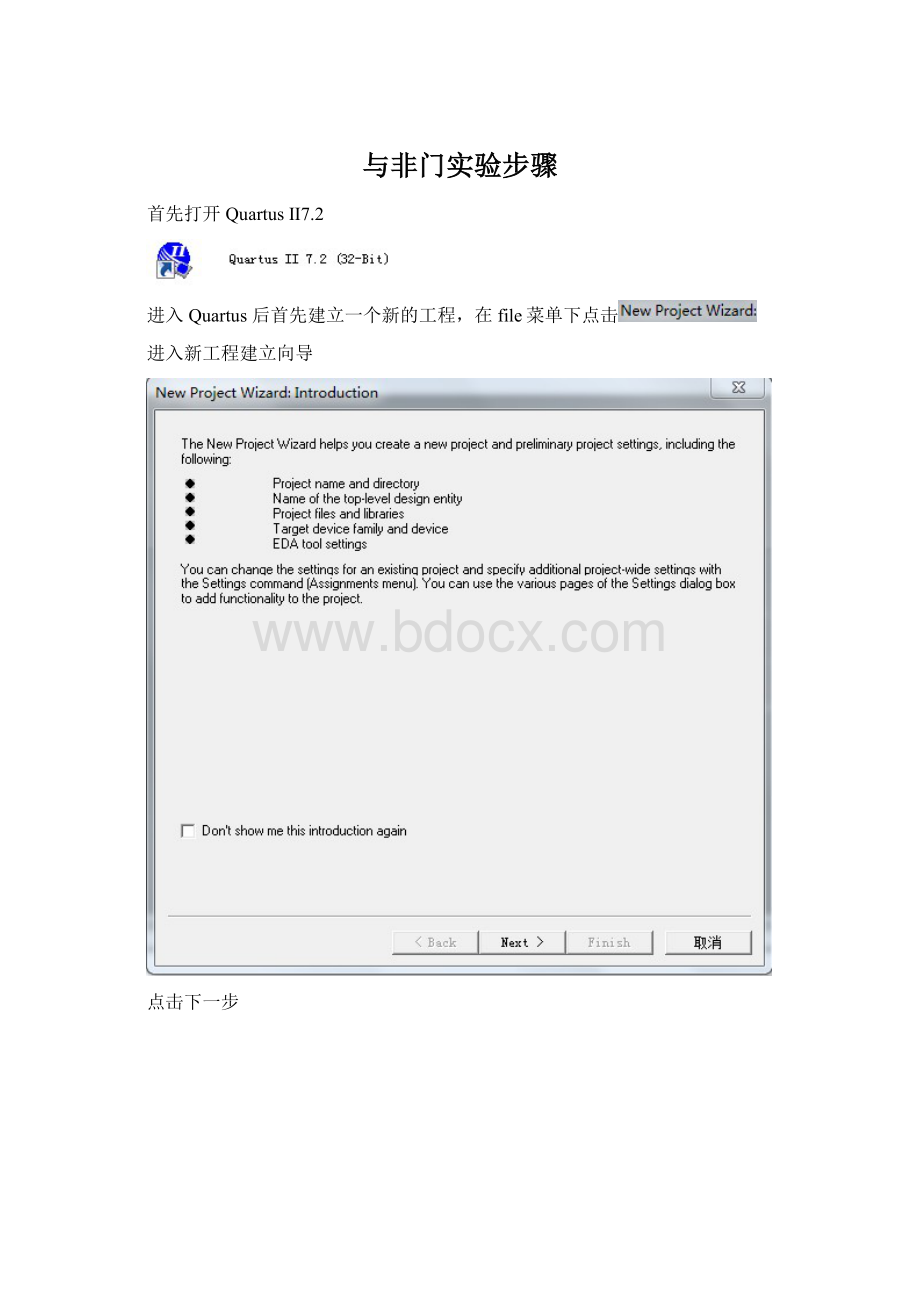

首先打开QuartusⅡ7.2

进入Quartus后首先建立一个新的工程,在file菜单下点击

进入新工程建立向导

点击下一步

第一项是工程的位置,第二项是工程的名称,第三项是工程顶层模块名称

注意事项:

工程顶层模块名称要与程序中的顶层模块名称相同,不然在后面软件编译的时候出现错误信息;路径中最好不要有中文和和空格。

然后点击下一步

添加设计文件,然后下一步

我们要选择的芯片是Cyclone,封装是PQFP,管脚是240管脚,速度等级是8,输入后下面会出现两种芯片,我们选择的是第1种,点击下一步

我们默认设置,下一步

点击完成。

进入Quartus界面,在界面的左侧有我们所加入的设计文件

点击设计文件,打开我们的设计文件

首先进行语法分析,点击语法分析按钮

如果程序正确,分析结束后,会出现

下一步,指定设备:

点击Assignment—device选择器件

这里芯片我们已经在前面设置过了,点击高级选项

在General中,默认设置

Configuration中,把下载设备改成EPCS1

下一步按默认设置

下一步,在不用的管脚中设成输入三态

点击确定。

下一步,指定管脚:

选择assignment—pins

查找说明手册或原理图定义管脚。

然后我们进行全局编译:

选择Processing--

选项进行编译

仿真工程

选择new—otherfiles,建立VWF文件

加入要观察的信号

可以用nodefinder…进行管脚设置

选择好信号

利用左边的工具栏改变波形

注意事项:

可以在Edit中的EndTime改变仿真的结束时间和间隔

选择processingSimulatortool,先进行功能仿真

先点击

产生仿真需要的网表文件,点击开始,仿真结束后打开图形

然后进行时序仿真,将Simulatormode改为timing

打开图形,产生延时

延时为与非门的延时,大约为10纳秒左右

程序下载:

首先确认电缆已连接到主机与FPGA实验平台的JTAG插口上,选择tools—programmer

在handwaresetup中选择下载电缆USB6.0,并把Program/configure打钩下载就行了

AS下载

首先确认电缆已连接到主机与FPGA实验平台的AS插口,在旁边的工具栏中添加.pof文件,并在Program/configure打钩,然后下载

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 与非门 实验 步骤

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx