数电期末复习题docx.docx

数电期末复习题docx.docx

- 文档编号:3806407

- 上传时间:2022-11-25

- 格式:DOCX

- 页数:21

- 大小:184.29KB

数电期末复习题docx.docx

《数电期末复习题docx.docx》由会员分享,可在线阅读,更多相关《数电期末复习题docx.docx(21页珍藏版)》请在冰豆网上搜索。

数电期末复习题docx

一、填空

1.计算机内部使用的数字符号只有0和1两个O

2.将十进制数175转换成二进制数为」0101111o

3.二进制数(111010010)2转换成十六进制数是—__(1D2)」6。

4.实现下列进制转换(F8)16=()犷()2

(48)10=()16=()2。

5.逻辑函数F=A+AB可化简为_A+B_。

6.写出题22图示电路输出函数F的表达式F=go

7.TTL门的输入端悬空,逻辑上相当于接—一电平。

&逻辑电路按其输出信号对输入信号响应的不同,可以分为组合逻辑电路与时序逻辑电路两大类。

9•由n个变量构成的任何一个最大项有一种变量取值使其值为lo

10.正逻辑的或门可以是负逻辑的丄—门电路。

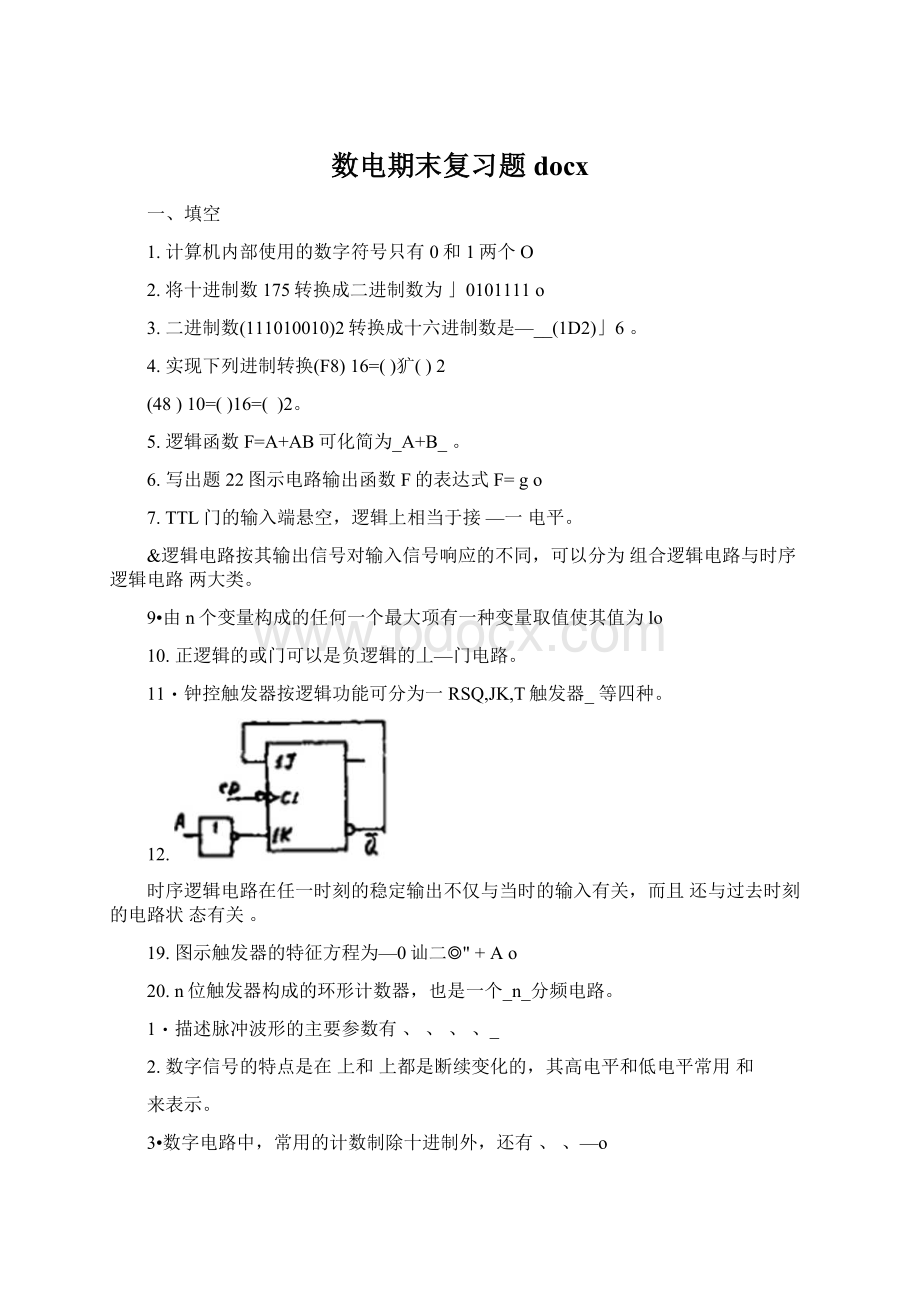

11・钟控触发器按逻辑功能可分为一RSQ,JK,T触发器_等四种。

12.

时序逻辑电路在任一时刻的稳定输出不仅与当时的输入有关,而且还与过去时刻的电路状态有关。

19.图示触发器的特征方程为—0讪二◎"+Ao

20.n位触发器构成的环形计数器,也是一个_n_分频电路。

1・描述脉冲波形的主要参数有、、、、_

2.数字信号的特点是在上和上都是断续变化的,其高电平和低电平常用和

来表示。

3•数字电路中,常用的计数制除十进制外,还有、、—o

4•用的BCD码有、、、等。

5.

(10110010)2二()10

7.(75)沪()2

9.逻辑代数又称为—代数。

最基本的逻辑关系有—、、_、三种。

10.逻辑函数的常用表示方法有—、、、o

11.逻辑代数中与普通代数相似的定律有、、。

摩根定律又称为。

12.模拟信号转换为数字信号,需要经过、、、四个过程。

13.单稳态触发器暂态时间取决于o

14.CMOS"或非”门,多余的不用输入端处理方法:

o

CMOS“与非”门不用的多余输入端的处理方法:

o

15.OCf]称为门,多个OC门输岀端并联到一起可实现功能。

2.将模拟信号转换为数字信号的过程叫—转换;将数字信号转换为模拟信号的过程叫—转换。

3.基本RS触发器在正常工作时,它的约束条件是臣+£=1则它不允许输入R=—且S=的

信号。

15.TTL与非门的扇出系数是o

16.RAM与ROM的区别是o

17.动态存储单元为不丢失信息,必须定期刷新。

18.(40F)16=()2=()10o

19.F(A,B,C)二1,其最小项表达式F二工m()°

2.0在一个CP脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的,触发方式

为式或式的触发器不会出现这种现象。

21•存储器的和是反映系统性能的两个重要指标。

22.4位移位寄存器,经过个CP脉冲后可将4位串行输入数据全部输入到寄存器内,再

经过个CP可以在串行输出端依次输出该4位数据。

23.D触发器的特性方程是;JK触发器的特性方程是o

33•由于R-S触发器有—个稳态,因此它可记录—位二进制码。

若存储一字节二进制信息,需要个触发器。

34.组合电路与时序电路的主要区别:

。

35.若要制成一个60分频器,至少需要片CT74195o

36.只读存储器ROM的特点是所存储的信息只能读出,最大的优点是掉电后信息不消失。

37.74LS76中的JK触发器是上升沿/下降沿)触发,74LS74中的D触发器是上

升沿/下降沿)触发。

1.集电极开路门的英文缩写为门,工作时必须外加—和_。

3.TTL与非门电压传输特性曲线分为—区区、—区、_区。

4.国产TTL电路相当于国际SN54/74LS系列,其中LS表示。

5.常用的组合逻辑部件有,,和。

8.—个基本RS触发器在正常工作时,不允许输入R=S=1的信号,因此它的约束条件是O

二、选择题

1.下列四个数中最大的数是()

A.(AF)16B.(001010000010)8421bcd

C.(10100000)2D.(198)io

2.将代码(10000011)8421BCD转换成二进制数为()

A.(01000011)2B.(01010011)2

C.(l0000011)2D.(000100110001)2

3.N个变量的逻辑函数应该有最小项()

A.2n个B.t?

个

C.2"个D.(2—1)个

4.下列关于异或运算的式子中,不正确的是()

A.A㊉A=0

C.A㊉0=AD.A㊉l=A

5.在下列逻辑电路中,不是组合逻辑电路的有()

A.译码器B.编码器C.全加器D.寄存器

6.八路数据分配器,其地址输入端有()

()个

A.1B.2C.3D.4

6.用四选一数据选择器实现函数Y=AjA0Ao,应使()

A.Do=D2=O,D1=D3=1B.Do=D2=1,山二。

3二0

C・D°二I)严0,lb二lb二1D.Do二D严1,I)2-l)3=0

12.能起定时作用的电路是()

A.施密特触发器B.单稳态电路C.多谐振荡器

D.译码器

7.具有十进制计数功能和二进制计数功能的集成电路分别是()

A、CT74LS74、CT74LS290B、CT74LS148、CT74LS161

C、CT74LS290.CT74LS161D、CT74LS16KCT74LS194

9.n位触发器构成的扭环形计数器,其无关状态数有()个。

A.2n-nB.2n-2nC.2nD.2n-1

11.对于钟控RS触发器,若要求其输出“0”状态不变,则输入的RS信号应为()

A.RS-XOB.RS-OXC.RS=X1D.RS=1X

13.为把50Hz的正弦波变成周期性矩形波,应当选用()

A.施密特触发器B.单稳态电路C.多谐振荡器D.译码器

14.电路输入端A、B和输出端Y的波形。

试问该电路是什么?

()

A.与门B.与非门C.或门D.或非门

a_n_rL_rLn_B_JIIIy-LJl_l

12.多谐振荡器与单稳态触发器的区别之一是(C)

A.前者有2个稳态,后者只有1个稳态

B.前者没有稳态,后者有2个稳态

C.前者没有稳态,后者只有1个稳态

D.两者均只有1个稳态,但后者的稳态需要一定的外界信号维持

13・欲得到D触发器的功能,以下诸图中唯有图(A)是正确的。

14.时序逻辑电路的一般结构由组合电路与(B)组成。

A.全加器B.存储电路

C.译码器D・选择器

15・函数F=AB+AB转换成或非一或非式为(B)

A.A+B+A+BB.A+B+A+B

C.AB+ABD.A+B+A+B

9.下列逻辑式中,正确的“或”逻辑公式是()。

A.

A+A=1

B.A+A=0C.

A+A=AD.

A+A=A

10.

下列逻辑式中,

正确的逻辑公式是(

)°

A.

~X+B=AB

B.A+B=A+BC

・A+B=AB

D.>1+0=0

11.

下列逻辑式中,正确的“或”逻辑式是(

)。

A.

1+1=1B.

1+1=2C.1+1=10

D..4+0=1

12.

逻辑式F=^BC可变换为()。

A.

F=力+E+C

B.F=A+B-\-C

C.F=ABC

D.F=A+B+c

13.模拟电路中晶体管大多工作于()。

A.放大状态B.截止状态、饱和状态C.击穿状态

若RAM的地址码有8位,行、列地址译码器的输入端都为4个,则它们的输出线(即字线加位线)共有条。

()

A.8B.16C.32D.256

以下电路中常用于总线应用的有。

A三态门B.OC门C.漏极开路门D.CMOS与非门

13.按输出状态论,施密特触发器属于()触发器。

A.双稳态B.单稳态C.无稳态

14.施密特触发器常用于对脉冲波形的()。

A.延时与定时B.计数与寄存C.整形与变换

1.某主从型JK触发器,当J=K=“L时,C端的频率/=200Hz,则Q的频率为()。

(a)200Hz(b)400Hz(c)l00Hz

2.触发器输出的状态取决于()。

(a)输入信号(b)电路的原始状态(c)输入信号和电路的原始状态

)o

3•时序逻辑电路与组合逻辑电路的主要区别是(

(a)时序电路只能计数,而组合电路只能寄存

(b)时序电路没有记忆功能,组合电路则有

(c)时序电路具有记忆功能,组合电路则没有

4.计数器如图所示,原状态为“IV,送入一个C脉冲后的新状态为()o(afir5(b)“o(r(c)tuor,(d)r(r

23.同步计数器和异步计数器的不同点是()0

(a)前者各触发器是同步进位的,后者则不同步

(b)前者由JK端接受计数信号,后者则由时钟脉冲端接受计数信号

(c)前者计数慢,后者计数快

24.计数器是一种()0

(a)组合逻辑电路(b)时序逻辑电路(c)脉冲整形电路

如果要构成位二进制计数器,需用触发器的个数最少为()。

(a)z?

(b)刀+1(c)z7-1

25•某计数器最大输入脉冲数为15,组成该计数器所需最少的触发器个数为()0

(a)2(b)3(c)4

26.某计数器最大输入脉冲数为8,组成该计数器所需最少的触发器个数为()。

(a)2(b)3(c)4

27.某计数器最大输入脉冲数为12,组成该计数器所需最少的触发器个数为()0

(a)2(b)3(c)4

2&—位十进制计数器由()位二进制计数器组成。

(a)2(b)3(c)4

3-7.下列四个选项错误的是o

A.TTb^A+B

B.A+B=AB

C.(AB)C=A^BC)

D.A+A=O

1

1

1

0

1

1

1

0

1

1

1

1

1

1

1

S)

00

01

00

01

11

11

10

图3-1题3・8

3-8.下列卡诺图化简错误的是

A.Y=AC^BC+AB

B.Y=AB+BC+AC

c.y=B+C+D

D.Y=BCD

4・1.若在编码器中有50个编码对象,则要求输出二进制代码位数为位。

A.5

B.6

C.10

D.50

4-2.一个16选一的数据选择器,其地址输入(选择控制输入)端有个。

A.1

B.2

C.4

D.16

4-3.四选一数据选择器的数据输出Y与数据输入Xi和地址码Ai之间的逻辑表达式为Y=o

A.AiA()X0+AiA°X]+A]AoX2+AtA0X3

B.AiAoXo

C.AiAoXj

D.A1A0X3

4-4.一个8选一数据选择器的数据输入端有个。

A.2

B.3

C.4

D.8

4-5.在下列逻辑电路中,不是组合逻辑电路的有

A.译码器

B.编码器

C.全加器

D.寄存器

4-6.八路数据分配器,其地址输入端有个。

A.1

B.2

C.3

D.4

4-7.用四选一数据选择器实现函数Y=A]A°+A』o,应使。

A.Do=D2=O,

D1=D3=1

B.D°=D2=1,Di=D3=0

C.Do=D]=O,D?

=D3=1

D.D°=D]=1,D2=D3=0

4-8.如果用三线■八线译码器(74LS138)和其他辅助门电路来实现逻辑函数Y=A2+A2A1,应

()

A.用与非门,Y=

B.用与门,

C.用或门,丫=可+可

D.用或门,Y=y0+y1+r44-r5+y6+y7

4-9.当编码器74LS147的输入端Ii、15、【6、17为低电平,其余输入端为高电平时,输出信号为()

A.1110

B.1010

C.1001

D.1OOO

4-10.下面—的描述是正确的。

()

A.组合逻辑电路任意时刻的稳态输出,与输入信号作用前电路原来状态有关。

B.编码器能将特定的输入信号变为二进制代码;而译码器能将二进制代码变为特定含义的输出信号,所以编码器与译码器使用是可逆的。

C.数据选择器与数据分配器中地址控制的作用是相同的。

D.用4选1数据选择器不能实现3变量的逻辑函数。

5.对于下图电路分析错误的是()。

A.此电路为异步五进制加法器

B.此电路具有自启动功能

C.此电路为异步五进制加法器,具有自启动功能

D.此电路为异步五进制加法器,无自启动功能

8.JK触发器组成下图3所示电路。

分析该电路是进制计数器。

()

图3

A.同步5进制计数器

B.异步5进制计数器

C.同步10进制计数器

D.异步10进制计数器三、分析题

1.图题2-5中,哪个电路是正确的?

并写出其表达式。

图题2-5

答案:

(a)7

!

Y=ABi

、CD

(b)

X

(c)

X

(d)

Y=AB

(e)

7

C=0时,

Y=A

C=1时,

Y=B

2.

已知Y=ABC^ABD^ACD+CD^ABC+ACD

空白的卡诺图如图所示,用卡诺图表示逻辑函数Y,并用卡诺图法化简。

3•设:

Y,=AB,Y.=A+B,Y)=A㊉B。

已知A、B的波形如图题1-5所示。

试画出£、丫幼Y?

对应A、B的波形。

Ajn^_n_rL

B

图题1-5

答案:

a

B

Y1\_]

丫2—ii~in

4.写出图题1-6各逻辑图的表达式。

图题1-6

答案:

X=AB+BC+BC

Y=AB^BC

Z=AC•BC

5.知真值表如表题1-6(a)>(b),试写出对应的逻辑表达式。

ABC

Y

000

0

001

1

010

1

011

0

100

1

101

0

110

0

111

1

ABCD

Y

0000

0

0001

0

0010

0

0011

0

0100

0

0101

0

0110

0

0111

1

1000

0

1001

0

1010

1

1011

1

1100

0

1101

1

1110

1

1111

1

表题1-6(a)表题1-6(b)

答案:

a)Y=ABC+~ABC+ABC+ABC

⑹Y=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD

6.试画出所示电路在CP脉冲作用下的各级波形。

设触发器的初始状态均为0。

7.画出图4电路的状态图,

并说明它为几进制计数器。

7

0-4-

+妝・

74LS161功能表见表1。

表174LS161功能表

cpJLJLJLJLJLJLJLJL

答案:

解:

Illi―1010—1011

1210v—1102——1100

为六进制计数器

8.分析图题3-1所示逻辑电路的逻辑功能。

A*Be

CM

图题3-1

9.已知下降沿有效的JK触发器C’P、J、K及异步置1端金、异步置0端0的波形如图题4-4所示,试画出Q的波形(设Q的初态为0)o

Pd

■

•

1

i•

:

:

11

1I

11

11

•1

••

i

ii

ie

Ii

ii

1

•ei

Sd

1

1

•

1

1

•

!

=u

••••

••••

11

11

•1

••

•1

•I

11

ii

ii

it

ii

ie

i

•

•

•

•

J」

•

•e

•i

i

••■

•••

••••

••1

9"1

・1

11

,1

•・

•1

L・■"H

lI

ti

■•

•e

•e

•

1

•

•

•

K

1

•••

:

:

_L

ifn

Ie

••

•

19

ti

•i

•

•

•

图题4-4

答案:

Q的波形如图所示

10.已知CP、D的波形如图题4-9,试画出高电平有效和上升沿有效D触发器Q的波形(设Q的

初态为0)o

cpj~LrLTLrLn_rL

图题4-9

答案:

Q的波形如图所示:

Q(CP上齐沿)

(a)(b)

图题5-6

11•试分析图题5-6所示(a)、(b)两个电路,画出状态转换图,并说明是几进制计数器。

答案:

(a)8进制(b)5进制12•试分析图题5-1所示的时序电路(步骤要齐全)。

QiQo

图题5-1

状态方程:

Qo11+1=Q1nQ0n

Qin+1=Q7Qon

答案:

驱动方程:

Jo=Q「,Ko=l;

Ji=Qon»K]=l;

状态转换表:

Qin

Qo11

Qin+1

Qon+1

0

0

0

1

0

1

1

0

1

0

0

0

1

1

0

0

状态转换图:

1U

逻辑功能:

能自启动的同步三进制加法计数器

13.试分析图题5-2所示的时序电路(步骤要齐全)

图题5-2

5-1答案:

异步八进制加法计数器

四、设计题

1.设计一个三人多数表决电路,写出真值表、卡诺图、表达式,并画出最简的与非逻辑图。

答案(略)

2.某医院有7间病房:

1、2、……7,1号病房是最重的病员,2、3、……7依次减轻,试用74LS148.74LS48.半导体数码管组成一个的呼叫、显示电路,要求:

有病员压下呼叫开关时,显示电路显示病房号(提示:

用的74LS48Yex作74LS48的灭灯信号)。

己知8线-3线优先编码器74LS148的功能表如表题3-6,符号图如题图3-6所示。

表题3・674LS148的功能表

输入

输出

5

I.ILfI41«fh

T

T

r

Y

YX

1

XXXXXXXX

1

1

1

1

1

0

11111111

1

1

1

0

1

0

xxxxxxxo

0

0

0

1

0

0

XXXXXxoi

0

0

1

1

0

0

XXXXX011

0

1

0

1

0

0

XXXX0111

0

1

1

1

0

0

XXX01111

1

0

0

1

0

0

XX011111

1

0

1

1

0

0

X01111111

1

1

0

1

0

0

01111111

1

1

1

1

0

BVRBO

RBTvufJA-

B「

C

D

bcdefg

2

-21054

111±11n11

3.用74LS138实现下列逻辑函数(允许附加门电路):

Yt=AC

Y2=ABC+AC

答案:

CBA

+5VO

F

GND

Y0YTY2Y3Y4Y5Y6Y7

A0A1A2S1S2S2

AY1

AY2

4.试用74LS151实现逻辑函数:

Y=A+BC

CBA

答案:

A?

"LS151頁

A2

S

izcsS£卜QQQQ2Q

5.试分别采用“反馈归零法"和“预置法”,用74LS163构成8进制计数器,要求:

输出8421BCD

码。

答案:

反馈归零法:

预置法:

oEZIO

OOOO

74LS163CP<

QO工Vdh|3|C^

VWf

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 期末 复习题 docx

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx