附录 II实验箱硬件资源连接.docx

附录 II实验箱硬件资源连接.docx

- 文档编号:3499637

- 上传时间:2022-11-23

- 格式:DOCX

- 页数:16

- 大小:18.71KB

附录 II实验箱硬件资源连接.docx

《附录 II实验箱硬件资源连接.docx》由会员分享,可在线阅读,更多相关《附录 II实验箱硬件资源连接.docx(16页珍藏版)》请在冰豆网上搜索。

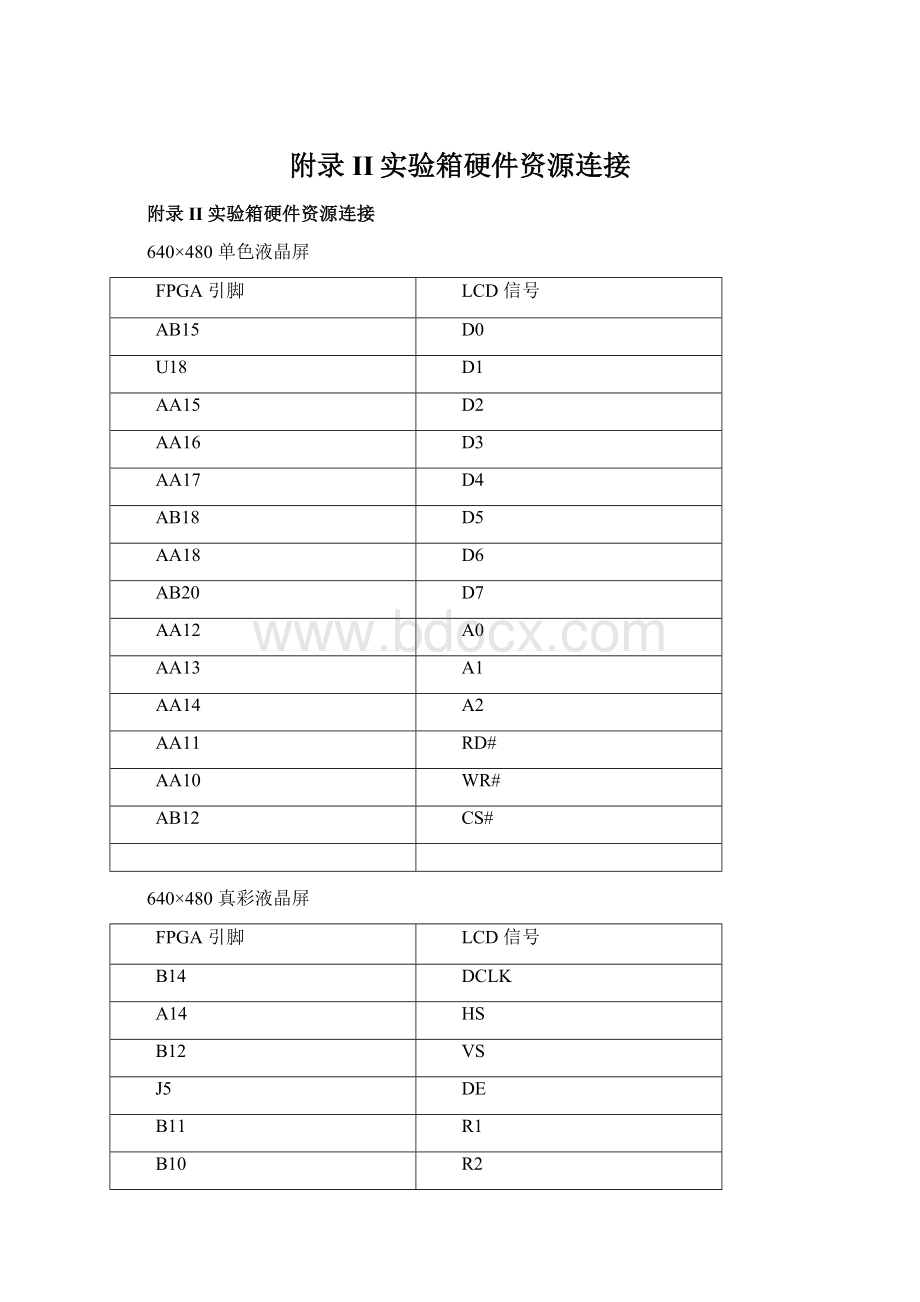

附录II实验箱硬件资源连接

附录II实验箱硬件资源连接

640×480单色液晶屏

FPGA引脚

LCD信号

AB15

D0

U18

D1

AA15

D2

AA16

D3

AA17

D4

AB18

D5

AA18

D6

AB20

D7

AA12

A0

AA13

A1

AA14

A2

AA11

RD#

AA10

WR#

AB12

CS#

640×480真彩液晶屏

FPGA引脚

LCD信号

B14

DCLK

A14

HS

B12

VS

J5

DE

B11

R1

B10

R2

A10

R3

F11

R4

G10

R5

G11

G0

G12

G1

J7

G2

G9

G3

F7

G4

E8

G5

F9

B1

F10

B2

E10

B3

F12

B4

E12

B5

8个用户LED

FPGA引脚

LED序号

G13

LED1

G15

LED2

G14

LED3

H12

LED4

H11

LED5

J10

LED6

L9

LED7

H10

LED8

动态译码模式七段码LED

FPGA引脚

七段码管信号

F13

a

F14

b

F15

c

E15

d

F16

e

F17

f

E18

g

F18

dp

G18

sel0

G17

sel1

G16

sel2

静态模式七段码LED

FPGA引脚

七段码管信号

F13

a

F14

b

F15

c

E15

d

F16

e

F17

f

E18

g

F18

dp

总线+片选模式七段码LED

FPGA引脚

七段码管信号

F13

a

F14

b

F15

c

E15

d

F16

e

F17

f

E18

g

F18

dp

AF5

cs0(左起)

AE4

cs1

AF4

cs2

AC12

cs3

G18

cs4

G17

cs5

G16

cs6

AA6

cs7

8个用户开关

FPGA引脚

开关序号

H8

K1

J8

K2

J9

K3

A4

K4

B4

K5

A5

K6

B5

K7

A6

K8

4×4键盘阵列

FPGA引脚

键盘阵列信号

B6

Col0

A7

Col1

B7

Col2

A8

Col3

B8

Row0

A9

Row1

B9

Row2

E5

Row3

16×16点阵LED

FPGA引脚

LED点阵信号

D9

Col1

C9

Col2

D10

Col3

C10

Col4

D11

Col5

C11

Col6

C12

Col7

D12

Col8

D18

Col9

D17

Col10

C17

Col11

D16

Col12

C16

Col13

D15

Col14

C15

Col15

D14

Col16

B22

Row1

A22

Row2

B21

Row3

A21

Row4

B20

Row5

A20

Row6

B19

Row7

A19

Row8

C8

Row9

D8

Row10

C7

Row11

D7

Row12

C6

Row13

D6

Row14

D5

Row15

C4

Row16

8个用户按键

FPGA引脚

按键序号

P25

S1

P26

S2

N25

S3

N26

S4

H6

S5

G6

S6

G5

S7

F6

S8

时钟和信号源

FPGA引脚

时钟源

C13()zxzc()()()

24MHz~1Hz,共10个时钟可选(右)

D13

24MHz~1Hz,共10个时钟可选(左)

实时时钟(RTC)

FPGA引脚

DS1302信号

AE12

SCLK

AE10

IO

AF10

RST

交通等LED

FPGA引脚

交通灯LED信号

B18

R_H(水平)

A18

Y_H(水平)

B17

G_H(水平)

A17

R_V(垂直)

B16

Y_V(垂直)

B15

G_V(垂直)

步进电机

FPGA引脚

步进电机信号

V21

STEP_A

V20

STEP_B

U12

STEP_C

V18

STEP_D

直流电机

FPGA引脚

直流电机信号

AE9

PWM(FPGA→MOTOR)

AF14

SPEED(MOTOR→FPGA)

串行ADC和串行DAC

FPGA引脚

串行ADC信号

串行DAC信号

K7

SCLK

/

J6

DOUT

/

K6

CS#

/

K9

/

SCLK

P7

/

DIN

K8

/

CS#

高速并行ADC和DAC

FPGA引脚

高速ADC信号

高速DAC信号

J11

D0

/

J14

D1

/

H16

D2

/

K16

D3

/

H17

D4

/

J18

D5

/

K17

D6

/

J17

D7

/

N9

OE

/

J16

CLK

/

F21

/

D0

F20

/

D1

E20

/

D2

D21

/

D3

C22

/

D4

C21

/

D5

D20

/

D6

D19

/

D7

C19

/

CLK

触摸屏控制(TSC)

FPGA引脚

TSC信号

AA6

SCLK

AF4

DOUT

AE4

DIN

AF5

CS#

AC12

PENIRQ

IICEEPROM

FPGA引脚

IIC信号

AC5

SCL

AD4

SDA

1-Wire温度传感器

FPGA引脚

1-Wire信号

K5

CLK/DAT

视频编解码

FPGA引脚

解码芯片信号

编码芯片信号

AC17

D0

/

AD17

D1

/

AC16

D2

/

AD16

D3

/

AC15

D4

/

AD15

D5

/

AC14

D6

/

AC13

D7

/

AD19

VS

/

AC19

HS

/

AC18

FID

/

AC20

AVID

/

AD13

PCLK

AC5

SCL

SCL

AD4

SDA

SDA

AD5

RESET

RESET

AC6

/

D0

AD6

/

D1

AC7

/

D2

AD7

/

D3

AC8

/

D4

AC11

/

D5

AD11

/

D6

AC10

/

D7

AD12

/

PCLK

AD10

/

HS

AC9

/

VS

AD8

/

BLANK

VGA接口

FPGA引脚

VGA信号

AC6

R

AD6

G

AC7

B

AD10

HS

AC9

VS

RS-232串口

FPGA引脚

RS-232信号

AD21

TXD

AC21

RXD

10M以太网接口

FPGA引脚

RTL8019AS信号

F1

D0

G2

D1

H1

D2

J2

D3

L2

D4

H15

D5

J13

D6

U9

D7

C3

A0

B3

A1

B2

A2

C2

A3

D2

A4

D1

RD#

E2

WR#

E1

CS#

N2

INT

通用IO接口(GeneralIO)

FPGA引脚

IO信号

AA20

J31

AB21

J32

Y15

J33

W17

J34

Y11

J35

Y13

J36

W8

J37

W10

J38

T8

J39

U17

J40

P1

J41

R8

J42

USB1.1设备接口

FPGA引脚

PDIUSBD12信号

U10

D0

V9

D1

Y10

D2

Y12

D3

Y14

D4

Y16

D5

V11

D6

Y18

D7

AE11

A0

AF13

OE#

W11

WE#

AE13

CS#

AE14

INT#

音频接口

FPGA引脚

UDI1341信号

AE5

SYSCLK

AF6

L3MODE

AE6

L3CLOCK

AF7

L3DATA

AE7

BCK

AF8

WS

AE8

DATAO

AF9

DATAI

SD卡接口

FPGA引脚

SD卡信号

AB10

DI

AA9

DO

AB8

CLK

AD23

CS

AC22

WP

AD22

CD

PS键盘/鼠标接口

FPGA引脚

PS2键盘信号

PS2鼠标信号

W12

CLK

/

V10

DAT

/

V14

/

CLK

V13

/

DAT

扩展接口

FPGA引脚

JP9(左侧插针)引脚

JP8(右侧插针)引脚

信号说明

/

33,34,35,36

29,30,31,32,33,34

GND

/

37,38,39,40

/

+5V

/

/

35,36,37,38,39,40

+12V

A19

1

/

FPGA_IO

B19

2

/

FPGA_IO

A20

3

/

FPGA_IO

B20

4

/

FPGA_IO

A21

5

/

FPGA_IO

B21

6

/

FPGA_IO

A22

7

/

FPGA_IO

B22

8

/

FPGA_IO

C4

9

/

FPGA_IO

D5

10

/

FPGA_IO

D6

11

/

FPGA_IO

C6

12

/

FPGA_IO

D7

13

/

FPGA_IO

C7

14

/

FPGA_IO

D8

15

/

FPGA_IO

C8

16

/

FPGA_IO

D9

17

/

FPGA_IO

C9

18

/

FPGA_IO

D10

19

/

FPGA_IO

C10

20

/

FPGA_IO

D11

21

/

FPGA_IO

C11

22

/

FPGA_IO

C12

23

/

FPGA_IO

D12

24

/

FPGA_IO

D14

25

/

FPGA_IO

C15

26

/

FPGA_IO

D15

27

FPGA_IO

C16

28

FPGA_IO

D16

29

FPGA_IO

C17

30

FPGA_IO

D17

31

FPGA_IO

D18

32

FPGA_IO

AA20

/

1

FPGA_IO

AB21

/

2

FPGA_IO

W17

/

3

FPGA_IO

Y15

/

4

FPGA_IO

Y13

/

5

FPGA_IO

Y11

/

6

FPGA_IO

W10

/

7

FPGA_IO

W8

/

8

FPGA_IO

U7

/

9

FPGA_IO

T8

/

10

FPGA_IO

R8

/

11

FPGA_IO

P1

/

12

FPGA_GCLK

N1

/

13

FPGA_GCLK

U17

/

14

FPGA_IO

W19

/

15

FPGA_IO

V17

/

16

FPGA_IO

W16

/

17

FPGA_IO

W15

/

18

FPGA_IO

L10

/

19

FPGA_IO

V14

/

20

FPGA_IO

V13

/

21

FPGA_IO

W12

/

22

FPGA_IO

V10

/

23

FPGA_IO

V21

/

24

FPGA_IO

V20

/

25

FPGA_IO

U12

26

FPGA_IO

V18

27

FPGA_IO

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 附录 II实验箱硬件资源连接 II 实验 硬件 资源 连接

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx