有关CDSP的Cache的操作.docx

有关CDSP的Cache的操作.docx

- 文档编号:332051

- 上传时间:2022-10-09

- 格式:DOCX

- 页数:11

- 大小:85.91KB

有关CDSP的Cache的操作.docx

《有关CDSP的Cache的操作.docx》由会员分享,可在线阅读,更多相关《有关CDSP的Cache的操作.docx(11页珍藏版)》请在冰豆网上搜索。

篇幅之一TIC64x+DSPCACHE一致性分析与维护

作者:

DSP技术应用工程师陈永康

摘要

在各种数字信号处理系统中,CACHE被广泛用于弥补Core与存储器之间的速度差异。

在CACHE的使用过程中,存在不同类型存储器之间数据是否一致的问题。

本文着重分析TI高性能C64x+DSP系列中各级CACHE之间数据一致性问题以及如何进行一致性维护。

1.概述

CACHE作为Core和低速存储器之间的桥梁,基于代码和数据的时间和空间相关性,以块为单位由硬件控制器自动加载Core所需要的代码和数据。

如果所有程序和数据的存取都由Core完成,基于CACHE的运行机制,Core始终能够得到存储器中最新的数据。

但是当有其它可以更改存储器内容的部件存在时,例如不需要Core干预的直接数据存取(DMA)引擎,就可能出现由于CACHE的存在而导致Core或者DMA不能够得到最新数据的现象,也就是CACHE一致性的问题。

2.C64x+存储器组织结构

TI对高性能C64x核进行了改进,使其性能大大提升,称之为C64x+DSP核。

基于C64x+核开发的DSP芯片,所有部件都以交换网络(SCR)为核心连接起来。

SCR上的部件分为两类:

Master和Slave。

Master包括Core、EDMA以及串行高速IO(sRIO),EMAC等外设。

Master可以直接通过SCR发起到Slave的数据传输。

Slave包括每一个Core的内存,DDR2外存以及其它不能直接发起数据传输的外设,Slave之间的数据传输,需要通过DMA协助完成。

各款基于C64x+DSP的数据手册上详细描述了SCR的配置和Master、Slave的情况。

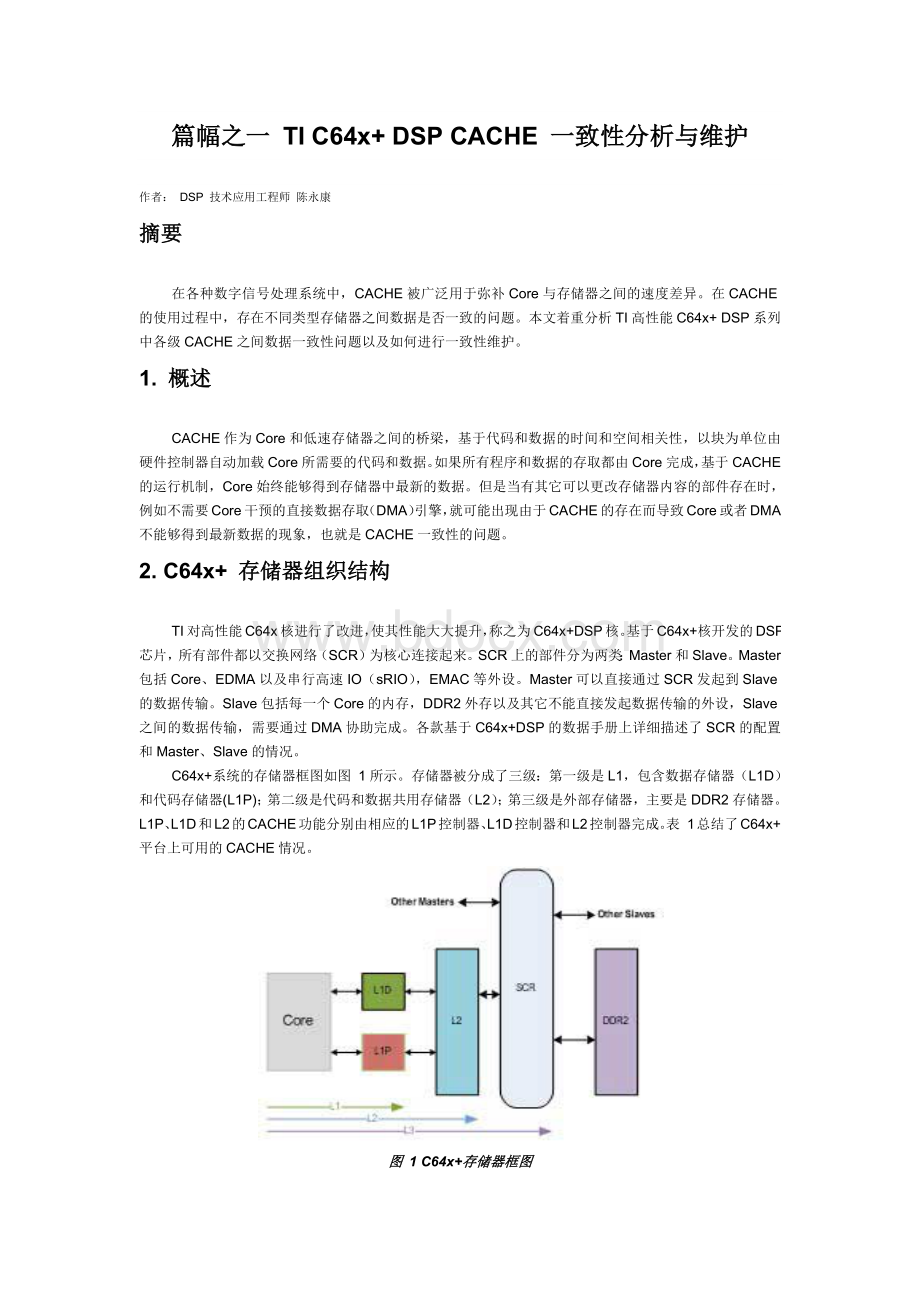

C64x+系统的存储器框图如图1所示。

存储器被分成了三级:

第一级是L1,包含数据存储器(L1D)和代码存储器(L1P);第二级是代码和数据共用存储器(L2);第三级是外部存储器,主要是DDR2存储器。

L1P、L1D和L2的CACHE功能分别由相应的L1P控制器、L1D控制器和L2控制器完成。

表1总结了C64x+平台上可用的CACHE情况。

图1C64x+存储器框图

表1C64x+CACHE特性

类型

大小

Line大小

L1P

代码;直接映射;

最大32K字节

32字节

L1D

数据;2路;读分配

最大32K字节

64字节

L2

代码、数据;4路;读写分配

最大256K字节

128字节

C64x+平台上L1P用来存储或者缓存代码;L1D用来存储或者缓存数据。

L1P和L1D大小都是32K字节,可以分别配置0K、4KB、8KB、16KB或者32KB作为CACHE,其余作为代码或者数据RAM。

作为CACHE的部分,用来缓存L2和DDR2的数据或代码。

作为RAM的部分,可以存储关键的代码或者数据使得Core能够以很高的速度

C64x+平台上L2存储器可用于存储代码和数据。

L2上最大可以分配256K字节CACHE来缓存DDR2中的数据或代码。

L2中其余部分作为RAM存储代码和数据。

图2描述了Core访问存储器内容的操作流程。

在这个访问流程中,Core对于存储器的访问总是先从离Core最近的一级存储器开始,如果命中,Core可以直接得到代码/数据,否则代码/数据会被加载到前几级的CACHE中,从而Core可以得到要处理的代码/数据。

在这个动态访问过程中,各级CACHE中的内容和下一级存储器中的内容可能存在不一致,这种瞬态的不一致不会造成问题。

但是,如果Core或者其它Master不能得到另外一方对存储器内容更新后的内容,就会出现CACHE一致性问题。

图2Core访问存储器流程

3.CACHE一致性问题分析

在任何时刻,Core或者其它Master访问存储器中数据时,由于CACHE的存在造成不能够得到最近更新过的数据,就会出现CACHE一致性问题。

在一个特定的时间范围内,各级CACHE和它的下一级存储器中的内容不一致是正常的。

因为CACHE的作用是在一段时间内将低速存储器中的内容自动搬运到高速的CACHE中重复使用。

当CACHE中的空间被后续的数据占用的时候,才将CACHE中的内容进行失效或者回写的操作。

在失效或者回写之前,CACHE中的内容可能与物理存储器中的内容是不一致的。

这种临时性的不一致是正常的,上述CACHE一致性问题的描述不包含此类正常情况。

CACHE的引入是为了提高Core存取数据的效率,所以出现CACHE一致性问题一定与Core对存储器的访问有关。

Core对存储器的访问分为两类:

1.Core读代码或者数据;

2.Core写代码或者数据。

据此,CACHE的一致性问题分为两个大类:

Core读一致性问题和Core写一致性问题。

在下面两个小节中,分别描述了这两种情况的模型:

3.1Core读一致性模型

图3给出了Core读一致性的模型。

在这个模型中,CACHE一致性问题的存在取决于图中虚线箭头指示的第二步操作能否在Core从CACHE中重新读数据之前完成。

如果不能,则会造成Core读取的数据不是其它Master更新后的数据,而是原来CACHE中的内容,从而导致一致性的问题。

图3Core读一致性模型

L1PCACHE对L2内存或者DDR2外存中的代码进行缓存。

当Core第一次对L2或者DDR2中的代码进行读操作的时候,由于代码不在L1PCACHE中,CAHCE硬件会将L2或者DDR2中的代码读到L1PCACHE中。

Core可以得到最新的代码,不存在一致性的问题。

此后,如果其它Master更新L2或者DDR2中的代码,然后Core再次读取此部分代码时,会发现相应的代码已经存在L1PCACHE中,此时Core会直接从L1PCACHE中读取代码。

由于Core不能得到最新的代码,就出现了Core读一致性的问题。

L1DCore读一致性问题的原理和L1P相同,只是L1D缓存的是L2或者DDR2中的数据。

L2CACHE对DDR2中的代码/数据进行缓存,当Core第一次对DDR2中的代码/数据进行读操作,这时代码/数据不在L2CACHE中,需要进行L2CACHE的加载,Core可以得到最新的代码/数据。

之后,其它Master对DDR2中的代码/数据进行更改,Core重读此部分代码/数据的时候,Core读到的是L2CACHE中的内容而不是DDR2中最新的代码/数据,因此也存在Core读一致性的问题。

3.2Core写一致性模型

图4给出了Core写一致性的模型。

在这个模型中,CACHE一致性问题的存在取决于图中虚线箭头指示的第二步操作能否在其它Master从存储器中读数据之前完成。

如果不能,会造成其它Master从存储器中读到的数据是原来的数据而不是Core更新过的数据,从而导致一致性的问题。

图4Core写一致性模型

当Core对L2或者DDR2中的代码/数据进行写操作的时候,如果代码/数据已经在L1CACHE中,新的代码/数据会被更新到L1CACHE中。

当其它Master从L2或者DDR2中读代码/数据的时候,会直接从L2或者DDR2中读取相应的内容,如果L1CACHE中新的代码/数据未被更新到L2或者DDR2中,则其它Master读取的不是更新后的内容,就会出现Core写一致性的问题。

同样,Core更新过的代码/数据有可能只是缓存在L2CACHE中,其它Master从DDR2中读取的内容不是更新后的内容,同样会出现Core写一致性的问题。

3.3C64x+一致性分析

在C64x+上的CACHE一致性问题,需要根据放置代码/数据的相应位置进行分析。

由于在C64x+平台上,L1P、L1D和L2内存既可以作为CACHE又可以作为存储器使用,因此,在分析一致性问题的时候,需要考虑以下几种情况

Case1.代码在L1P存储器中;

Case2.代码在L2存储器中;

Case3.代码在DDR2存储器中;

Case4.数据在L1D存储器中;

Case5.数据在L2存储器中;

Case6.数据在DDR2存储器中。

对于Case1,由于代码直接在L1P存储器中,不需要进行CACHE,所以不会存在一致性的问题。

对于Case2和Case3,涉及到L1PCACHE,存在代码的更新能否被Core读到的问题。

代码的更新分成两种情况:

一是Core在运行过程中对代码进行修改;二是其它Master对代码的修改。

这两种情况下,都会存在CACHE读一致性问题,需要由软件来维护。

对于Case4,数据直接在L1D存储器中,Core始终能够读到其它Master更新到L1D内存中的内容,Core写过的数据也能够被其它Master直接从L1D内存中读到。

所以不会存在一致性的问题。

对于Case5,数据在L2存储器,按照上面的分析,会存在CACHE读和写一致性的问题。

在C64x+平台上这种情况下的一致性问题会由硬件自动维护。

对于Case6,也会存在CACHE读和写一致性的问题,这种情况需要软件进行CACHE一致性的维护。

4.C64x+CACHE一致性维护操作

出现CACHE一致性问题时,为了保证Core或者其它Master在进行数据操作的时候能够得到最新的数据,需要进行CACHE的一致性维护操作。

CACHE一致性问题维护在设计中,有两种处理方式:

硬件自动维护和应用程序进行维护。

下面具体分析以上几种情况在C64x+平台上如何进行CACHE一致性问题处理:

4.1硬件维护的CACHE一致性

在C64x+平台上,硬件会对Case5的情况自动进行数据一致性维护。

分析需要分为读写两类操作进行,图5和图6分别描述了Core对L2上的数据进行读和写的情况。

图5Core读L2数据的情况

图6Core写L2数据的情况

其它Master要对L2中的内容进行更新操作时,L2控制器会根据被更新数据的地址判断相应的地址是否在L1DCACHE中,如果在L1DCACHE中,硬件会自动将更新的数据拷贝一份到L1DCACHE中。

当Core重新对L2中的这部分数据进行处理的时候,如果要读取的数据已经在L1DCACHE中,Core可以直接从L1DCACHE中得到更新过的数据。

如果要读取的数据不在L1DCACHE中,L1D控制器会自动从L2加载数据,Core也可以得到更新后的数据。

过程如图5中的1和2所示,这样就可以解决一致性的问题。

其它Master要对L2中的内容进行读操作的时候,L2控制器会判断要读取的数据地址是否在L1DCACHE中,对于在L1DCACHE中的数据,硬件会自动从L1DCACHE中读取最新的数据。

对于不在L1DCACHE中的数据,说明L2中的数据已经是最新的数据,可以直接从L2中读取。

通过这样的处理,可以保证其它Master读到Core更新后的数据,从而可以解决一致性的问题。

过程如图6中的1和2所示。

4.2软件维护的CACHE一致性

在C64x+平台上,Case2、Case3和Case6的情况需要软件进行的一致性维护操作以保证Core或者其它Master可以得到最新的数据。

4.2.1C64x+软件一致性维护实现

C64x+平台上由软件控制的一致性维护操作包含三种:

CACHE数据失效、CACHE数据回写和CACHE数据回写并失效。

启动维护操作需要配置相应的基地址和计数寄存器,当计数寄存器中的值变为0时表示操作完成。

TI提供的芯片支持库中也提供了相应的API来完成相应的功能。

各种操作涉及的各级CACHE的一致性操作控制寄存器列在表2中。

·WB:

全局回写寄存器

·INV:

全局失效寄存器

·WBINV:

全局回写并失效寄存器

·IBAR:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 有关 CDSP Cache 操作

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls