开关电源环路设计详细_精品文档.pdf

开关电源环路设计详细_精品文档.pdf

- 文档编号:3216115

- 上传时间:2022-11-20

- 格式:PDF

- 页数:16

- 大小:278.45KB

开关电源环路设计详细_精品文档.pdf

《开关电源环路设计详细_精品文档.pdf》由会员分享,可在线阅读,更多相关《开关电源环路设计详细_精品文档.pdf(16页珍藏版)》请在冰豆网上搜索。

226.4开关电源闭环设计开关电源闭环设计从反馈基本概念知道:

放大器在深度负反馈时,如输入不变,电路参数变化、负载变化或干扰对输出影响减小。

反馈越深,干扰引起的输出误差越小。

但是,深反馈时,反馈环路在某一频率附加相位移如达到180,同时输出信号等于输入信号,就会产生自激振荡。

开关电源不同于一般放大器,放大器加负反馈是为了有足够的通频带,足够的稳定增益,减少干扰和减少线性和非线性失真。

而开关电源,如果要等效为放大器的话,输入信号是基准(参考)电压Uref,一般说来,基准电压是不变的;反馈网络就是取样电路,一般是一个分压器,当输出电压和基准一定时,取样电路分压比(kv)也是固定的(Uo=kvUref)。

开关电源不同于放大器,内部(开关频率)和外部干扰(输入电源和负载变化)非常严重,闭环设计目的不仅要求对以上的内部和外部干扰有很强抑制能力,保证静态精度,而且要有良好的动态响应。

对于恒压输出开关电源,就其反馈拓扑而言,输入信号(基准)相当于放大器的输入电压,分压器是反馈网络,这就是一个电压串联负反馈。

如果恒流输出,就是电流串联负反馈。

如果是恒压输出,对电压取样,闭环稳定输出电压。

因此,首先选择稳定的参考电压,通常为56V或2.5V,要求极小的动态电阻和温度漂移。

其次要求开环增益高,使得反馈为深度反馈,输出电压才不受电源电压和负载(干扰)影响和对开关频率纹波抑制。

一般功率电路、滤波和PWM发生电路增益低,只有采用运放(误差放大器)来获得高增益。

再有,由于输出滤波器有两个极点,最大相移180,如果直接加入运放组成反馈,很容易自激振荡,因此需要相位补偿。

根据不同的电路条件,可以采用Venable三种补偿放大器。

补偿结果既满足稳态要求,又要获得良好的瞬态响应,同时能够抑制低频纹波和对高频分量衰减。

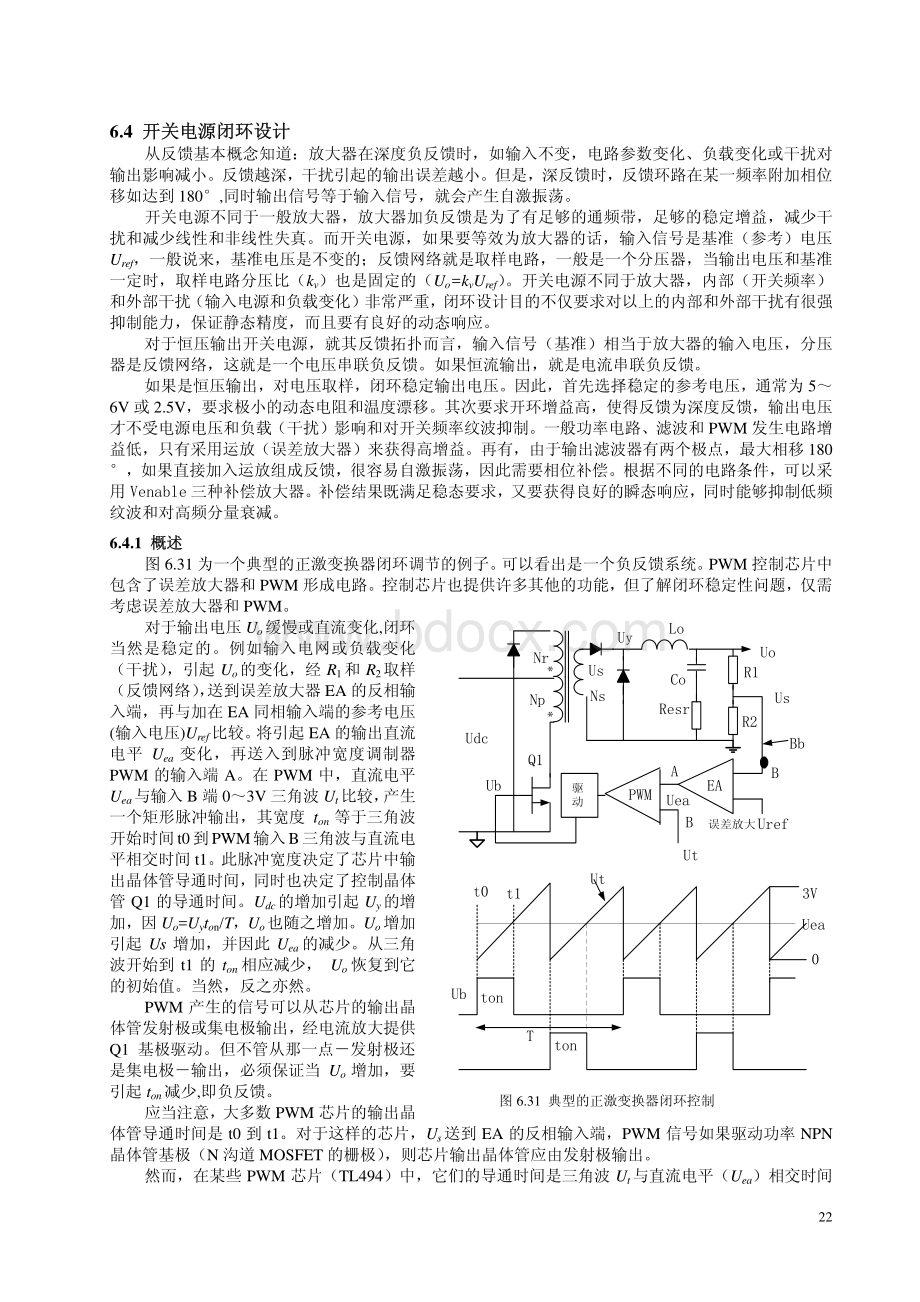

6.4.1概述概述图6.31为一个典型的正激变换器闭环调节的例子。

可以看出是一个负反馈系统。

PWM控制芯片中包含了误差放大器和PWM形成电路。

控制芯片也提供许多其他的功能,但了解闭环稳定性问题,仅需考虑误差放大器和PWM。

对于输出电压Uo缓慢或直流变化,闭环当然是稳定的。

例如输入电网或负载变化(干扰),引起Uo的变化,经R1和R2取样(反馈网络),送到误差放大器EA的反相输入端,再与加在EA同相输入端的参考电压(输入电压)Uref比较。

将引起EA的输出直流电平Uea变化,再送入到脉冲宽度调制器PWM的输入端A。

在PWM中,直流电平Uea与输入B端03V三角波Ut比较,产生一个矩形脉冲输出,其宽度ton等于三角波开始时间t0到PWM输入B三角波与直流电平相交时间t1。

此脉冲宽度决定了芯片中输出晶体管导通时间,同时也决定了控制晶体管Q1的导通时间。

Udc的增加引起Uy的增加,因Uo=Uyton/T,Uo也随之增加。

Uo增加引起Us增加,并因此Uea的减少。

从三角波开始到t1的ton相应减少,Uo恢复到它的初始值。

当然,反之亦然。

PWM产生的信号可以从芯片的输出晶体管发射极或集电极输出,经电流放大提供Q1基极驱动。

但不管从那一点发射极还是集电极输出,必须保证当Uo增加,要引起ton减少,即负反馈。

应当注意,大多数PWM芯片的输出晶体管导通时间是t0到t1。

对于这样的芯片,Us送到EA的反相输入端,PWM信号如果驱动功率NPN晶体管基极(N沟道MOSFET的栅极),则芯片输出晶体管应由发射极输出。

然而,在某些PWM芯片(TL494)中,它们的导通时间是三角波Ut与直流电平(Uea)相交时间图6.31典型的正激变换器闭环控制*PWM驱动EAR1R2ResrCoLoUsNsNrNpQ1UbUdcUrefUtAB误差放大UeaUoUsBb3VUea0Utt0t1UbtontonTUyB23到三角波终止时间t2。

对于这样的芯片,如果驱动NPN晶体管,输出晶体管导通(如果从芯片的输出晶体管发射极输出),这样会随晶体管导通时间增加,使得Uo增加,这是正反馈,而不是负反馈。

因此,TL494一类芯片,Us送到EA的同相输入端,Uo增加使得导通时间减少,就可以采用芯片的输出晶体管的发射极驱动。

图6.31电路是负反馈且低频稳定。

但在环路内,存在低电平噪音电压和含有丰富连续频谱的瞬态电压。

这些分量通过输出Lo,Co滤波器、误差放大器和Uea到Uy的PWM调节器引起增益改变和相移。

在谐波分量中的一个分量,增益和相移可能导致正反馈,而不再是负反馈,在6.2.7节我们已讨论过闭环振荡的机理。

以下就开关电源作加体分析。

6.4.2环路增益环路增益还是来研究图6.31正激变换器。

假定反馈环在B点连接到误差放大器的反相输入端断开成开环。

任何一次谐波分量的噪声从B经过EA放大到Uea,由Uea传递到电压Uy的平均值,和从Uy的平均值通过Lo,Co返回到Bb(正好是先前环路断开点)都有增益变化和相移。

这就是6.2.7讨论的环路增益信号通路。

如果假定某个频率f1的信号在B注入到环路中,回到B的信号的幅值和相位被上面提到回路中的元件改变了。

如果改变后的返回的信号与注入的信号相位精确相同,而且幅值等于注入信号,即满足GH-1。

要是现在将环闭合(B连接到Bb),并且注入信号移开,电路将以频率f1继续振荡。

这个引起开始振荡的f1是噪声频谱中的一个分量。

为达到输出电压(或电流)的静态精度,误差放大器必须有高增益。

高增益就可能引起振荡。

误差放大器以外的传递函数一般无法改变,为避免加入误差放大器以后振荡,一般通过改变误差放大器的频率特性(校正网络),使得环路频率特性以-20dB/dec穿越,并有45相位裕度,以达到闭环的稳定。

以下我们研究误差放大器以外的电路传递函数的频率特性。

1.带有带有LC滤波电路的环路增益滤波电路的环路增益Gf除了反激变换器(输出滤波仅为输出电容)外,这里讨论的所有拓扑都有输出滤波器。

通常滤波器设计时根据脉动电流为平均值(输出电流)的20%选取滤波电感。

根据允许输出电压纹波和脉动电流值以及电容的ESR选取输出滤波电容。

如果电解电容没有ESR(最新产品),只按脉动电流和允许纹波电压选取。

由此获得输出滤波器的谐振频率,特征阻抗,ESR零点频率。

在频率特性一节图6.7示出了LC滤波器在不同负载下的幅频和相频特性。

为简化讨论,假定滤波器为临界阻尼Ro=1.0Zo,带有负载电阻的输出LC滤波器的幅频特性如图6.32(a)中12345所示。

此特性假定输出电容的ESR为零。

在低频时,XcXL,输入信号不衰减,增益为1即0dB。

在f0以上,每十倍频Co阻抗以20dB减少,而Lo阻抗以20dB增加,使得增益变化斜率为40dB/dec。

当然在f0增益不是突然转变为2斜率的。

实际上在f0前增益曲线平滑离开0dB曲线,并在f0后不久渐近趋向40dB/dec斜率。

这里为讨论方便,增益曲线突然转向40dB/dec。

如果使相应于Ro=1.0Zo条件下稳定,那么在其它负载也将稳定。

但应研究电路在轻载(Ro1.0Zo)时的特性,因为在LC滤波器转折频率f=f0增益谐振提升。

滤波电容有ESR的LC滤波器幅频特性如图6.35b的曲线123456。

大多数滤波电容具有ESR。

在f0以上的低频段,容抗远远大于ESR,从Uo看到阻抗仅是容抗起主要作用,斜率仍为-40dB/dec;在更高频时,esrRC1,从输出端看的阻抗只是ESR,在此频率范围,电路变为LR滤波,而不是LC滤波。

即0(dB)Lo0(dB)Lo12fcUo123Uo3-20UinCoRo-20UinCoRo-2-2Resr-404-404fesr-60-60-1556-80102103104105f/Hz102103104105f/Hz(a)(b)图6.32临界阻尼LC滤波器输出电容无ESR(a)和有ESR(b)幅频特性24esresrinoffjRLjUUG+=+=1111&(6-55)式中转折频率fesrResr/(2L)。

在此频率范围,感抗以20dB/dec增加,而ESR保持常数,增益以-20dB/dec斜率下降。

幅频特性由-40dB/dec转为-20dB/dec斜率点为fesr,这里电容阻抗等于ESR。

ESR提供一个零点。

转变是渐近的,但所示的突然转变也足够精确。

2.PWM增益增益图6.32(a)中由误差放大器输出到电感输入电压Uy的平均值UaU的增益是PWM增益,并定义为Gm。

一般电压型控制芯片中误差放大器的输出Uea与内部三角波比较产生PWM信号调整输出电压。

三角波的幅值03V(实际上是0.53V)。

如果芯片控制推挽(桥式、半桥)电路,变压器频率是芯片频率的一半,占空比D随误差放大器输出可以在01之间改变。

如果是正激,只采用一半脉冲,占空度在00.5之间改变。

在图6.34b中,当Uea0,D=ton/T=0,在Uy的宽度为零,UaU也为零。

如果Uea移动到3V,在三角波的峰值,ton/T=D=0.5,Uy的平均值就是UaU(Usp-1)D,其中Usp是变压器次级电压,1为整流二极管压降。

则调制器的直流增益为UaU与Uea的比值3)1(5.0=speaoUmVUUG(6-56)此增益与频率无关。

3.取样增益反馈系数取样增益反馈系数图6.31中还有一个增益衰减,就是R1和R2组成的采样电路。

大多数PWM芯片的误差放大器的参考输入端不可能大于2.5V,因此如果输出电压一旦决定,此增益即为212RRRUUGoss+=(6-57)如果输出5V,采样电阻R1=R2,Us(Uref)与Uo之间的增益为-6dB,即1/2。

4.输出输出LC滤波器加上滤波器加上PWM和采样网络的总增益和采样网络的总增益为了得到环路增益波特图,我们先将输出LC滤波器增益Gf、PWM增益Gm和采样网络增益Gs之和Gt如图6.33所示。

从0Hz(直流)到频率LCf210=的增益是Gm+Gs,这里LC滤波器增益为零。

在f0转折为-40dB/dec斜率,并保持此斜率一直到fesr,这里电容阻抗等于Resr。

在这个频率它转折为斜率-20dB/dec。

由这个曲线可以确定误差放大器的幅频和相频特性以满足稳定环路的两个判据。

6.4.3误差放大器的幅频特性整形误差放大器的幅频特性整形如果将开关电源的闭环作为一个放大器来研究,放大器输入信号为开关电源的参考电压。

从负反馈组态来说是一个电压串联负反馈。

这里误差放大器是一个同相放大器。

从误差放大器的同相端到误差放大器输出、PWM发生、电源输出和取样返回到误差放大是反相输入端,在任何频率在增益下降到0dB时附加相位移小于135。

以下来讨论误差放大器的补偿。

为讨论方便,取样信号加在反相端,放大器输出总是反相,反馈信号返回到反相端附加相移不能超过135,即45相位裕度。

第一步首先建立穿越频率fc0,在此频率总增益为0dB。

然后选择误差放大器的增益,迫使总环路增益在fc0为0dB。

下一步设计误差放大器的增益斜率,以使得总开环增益在fc0以斜率-20dB/dec穿越(图6.18)。

最后,调整幅频特性达到希望的相位裕度。

采样理论指出,为了闭环的稳定,fc0必须小于开关频率的一半。

但必须远远小于开关频率,否则有较大幅值的开关频率纹波。

一般经验取fc0为开关频率的1/41/5。

参考图6.33中除误差放大器以外的环路增益Gt是LC滤波器增益Gf、调节器增益Gm和检测网络增益Gs之和。

假定滤波电容有ESR,在fesr由斜率-40dB/dec转折为-20dB/

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 开关电源 环路 设计 详细 精品 文档

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls