DE2 实验练习解答lab4 countersverilogdigital logic.docx

DE2 实验练习解答lab4 countersverilogdigital logic.docx

- 文档编号:3194216

- 上传时间:2022-11-20

- 格式:DOCX

- 页数:13

- 大小:307.87KB

DE2 实验练习解答lab4 countersverilogdigital logic.docx

《DE2 实验练习解答lab4 countersverilogdigital logic.docx》由会员分享,可在线阅读,更多相关《DE2 实验练习解答lab4 countersverilogdigital logic.docx(13页珍藏版)》请在冰豆网上搜索。

DE2实验练习解答lab4countersverilogdigitallogic

本练习的目的是使用计数器。

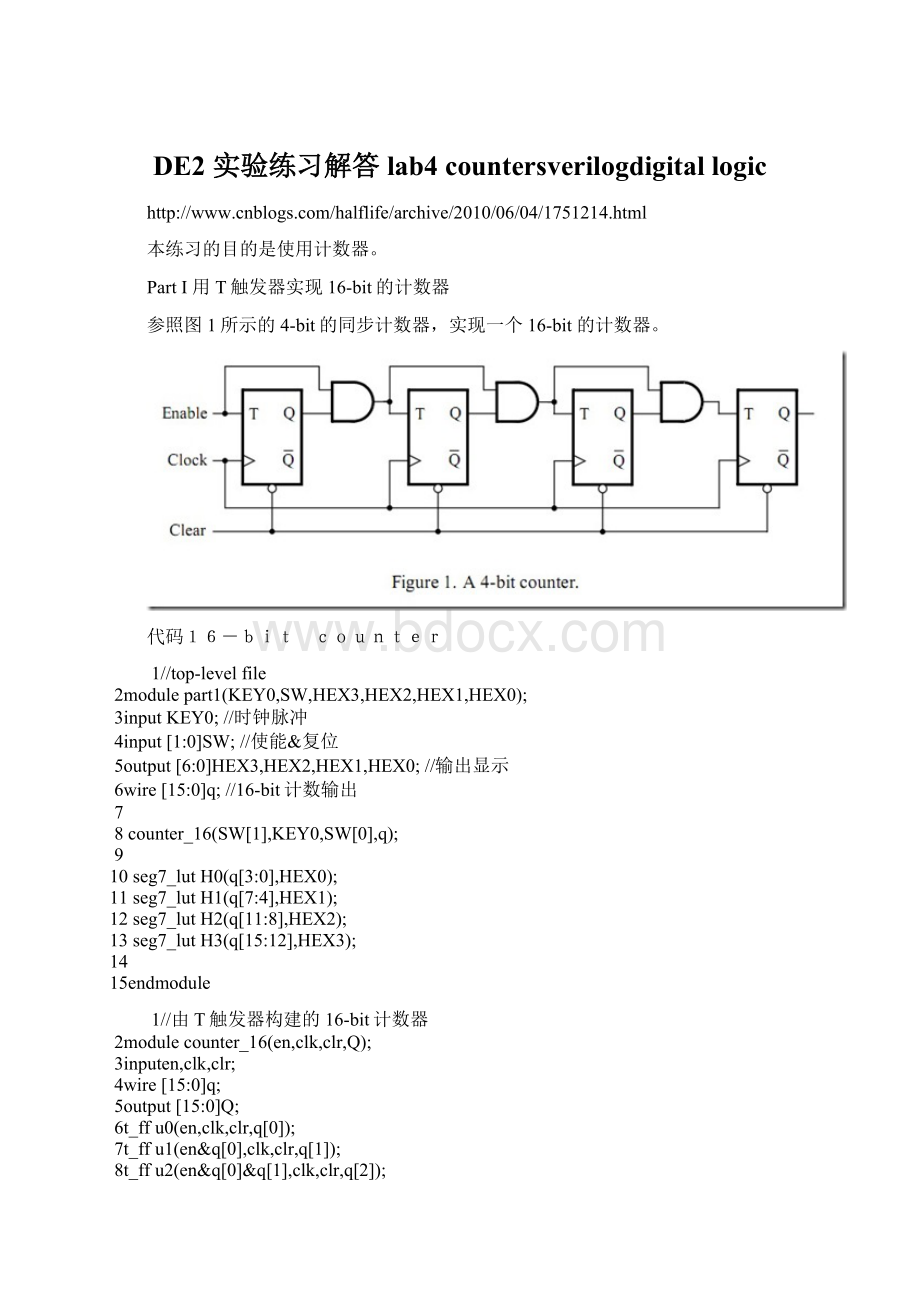

PartI用T触发器实现16-bit的计数器

参照图1所示的4-bit的同步计数器,实现一个16-bit的计数器。

代码16-bit counter

1//top-levelfile

2modulepart1(KEY0,SW,HEX3,HEX2,HEX1,HEX0);

3inputKEY0;//时钟脉冲

4input[1:

0]SW;//使能&复位

5output[6:

0]HEX3,HEX2,HEX1,HEX0;//输出显示

6wire[15:

0]q;//16-bit计数输出

7

8counter_16(SW[1],KEY0,SW[0],q);

9

10seg7_lutH0(q[3:

0],HEX0);

11seg7_lutH1(q[7:

4],HEX1);

12seg7_lutH2(q[11:

8],HEX2);

13seg7_lutH3(q[15:

12],HEX3);

14

15endmodule

1//由T触发器构建的16-bit计数器

2modulecounter_16(en,clk,clr,Q);

3inputen,clk,clr;

4wire[15:

0]q;

5output[15:

0]Q;

6t_ffu0(en,clk,clr,q[0]);

7t_ffu1(en&q[0],clk,clr,q[1]);

8t_ffu2(en&q[0]&q[1],clk,clr,q[2]);

9t_ffu3(en&q[0]&q[1]&q[2],clk,clr,q[3]);

10t_ffu4(en&q[0]&q[1]&q[2]&q[3],clk,clr,q[4]);

11t_ffu5(en&q[0]&q[1]&q[2]&q[3]&q[4],clk,clr,q[5]);

12t_ffu6(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5],clk,clr,q[6]);

13t_ffu7(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6],clk,clr,q[7]);

14t_ffu8(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7],clk,clr,q[8]);

15t_ffu9(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7]&q[8],

16clk,clr,q[9]);

17t_ffu10(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7]&q[8]&q[9],

18clk,clr,q[10]);

19t_ffu11(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7]&q[8]&q[9]&q[10],

20clk,clr,q[11]);

21t_ffu12(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7]&q[8]&q[9]&q[10]&q[11],

22clk,clr,q[12]);

23t_ffu13(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7]&q[8]&q[9]&q[10]&q[11]&q[12],

24clk,clr,q[13]);

25t_ffu14(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7]&q[8]&q[9]&q[10]&q[11]&q[12]&q[13],

26clk,clr,q[14]);

27t_ffu15(en&q[0]&q[1]&q[2]&q[3]&q[4]&q[5]&q[6]&q[7]&q[8]&q[9]&q[10]&q[11]&q[12]&q[13]&q[14],

28clk,clr,q[15]);

29

30assignQ=q;

31

32endmodule

1//Tflipflop

2modulet_ff(t,clk,rst_n,q);

3inputt,clk,rst_n;

4outputregq;

5

6always@(posedgeclk)

7begin

8if(!

rst_n)

9q<=0;

10else

11begin

12if(t==1'b1)

13q<=~q;

14else

15q<=q;

16end

17end

18

19endmodule

图2 Fmax值

图3 占用的LE数量

Part II 用赋值语句实现16-bit计数器

代码

1//counter-16bit

2modulepart2(clk,rst_n,q);

3inputclk,rst_n;

4outputreg[15:

0]q;

5

6always@(posedgeclk)

7begin

8if(!

rst_n)

9q<=1'b0;

10else

11begin

12if(q==65535)

13q<=0;

14else

15q<=q+1;

16end

17end

18

19endmodule

图4 16-bit计数器的RTL视图

图5 Fmax值

图6 16-bit计数器占用的LE

Part III 用LPM实现16-bit计数器

代码

1//Top-levelfile

2modulecounter_lpm(en,clk,clr,q);

3inputen,clk,clr;

4output[15:

0]q;

5

6megcountercounter_16bit(.clock(clk),.cnt_en(en),.sclr(clr),

7.q(q)

8);

9endmodule

1//synopsystranslate_off

2`timescale1ps/1ps

3//synopsystranslate_on

4modulemegcounter(

5clock,

6cnt_en,

7sclr,

8q);

9

10inputclock;

11inputcnt_en;

12inputsclr;

13output[15:

0]q;

14

15wire[15:

0]sub_wire0;

16wire[15:

0]q=sub_wire0[15:

0];

17

18lpm_counterlpm_counter_component(

19.sclr(sclr),

20.clock(clock),

21.cnt_en(cnt_en),

22.q(sub_wire0),

23.aclr(1'b0),

24.aload(1'b0),

25.aset(1'b0),

26.cin(1'b1),

27.clk_en(1'b1),

28.cout(),

29.data({16{1'b0}}),

30.eq(),

31.sload(1'b0),

32.sset(1'b0),

33.updown(1'b1));

34defparam

35lpm_counter_component.lpm_direction="UP",

36lpm_counter_component.lpm_port_updown="PORT_UNUSED",

37lpm_counter_component.lpm_type="LPM_COUNTER",

38lpm_counter_component.lpm_width=16;

39

40

41endmodule

图7 用LPM实现16-bit计数器所占用的LE

Part IV 循环显示0-9

在HEX0上循环显示0-9,每秒刷新一次。

代码

1//top-levelfile

2moduleseg_number(

3output[6:

0]HEX0,

4inputCLOCK_50,

5input[0:

0]KEY

6);

7

8wireclk_1hz;

9reg[3:

0]cnt;

10

11divu0(

12.o_clk(clk_1hz),

13.i_clk(CLOCK_50),

14.rst_n(KEY)

15);

16

17always@(posedgeclk_1hzornegedgeKEY)

18begin

19if(!

KEY)

20cnt<=4'b0;

21else

22begin

23if(cnt==4'd9)

24cnt<=4'b0;

25else

26cnt<=cnt+1'b1;

27end

28end

29

30seg7_lutu1(

31.oseg(HEX0),

32.idig(cnt[3:

0])

33);

34endmodule

35

36//divider

37modulediv(

38outputrego_clk,

39inputrst_n,

40inputi_clk

41);

42

43parameterN=50_000_000;

44parameterM=24_999_999;

45

46reg[25:

0]cnt;

47

48always@(posedgei_clkornegedgerst_n)

49begin

50if(!

rst_n)

51cnt<=26'b0;

52else

53begin

54if(cnt==N-1)

55cnt<=26'b0;

56else

57cnt<=cnt+26'b1;

58end

59end

60always@(posedgei_clkornegedgerst_n)

61begin

62if(!

rst_n)

63o_clk<=0;

64else

65begin

66if(cnt<=M)

67o_clk<=1;

68else

69o_clk<=0;

70end

71end

72

73endmodule

74

75//seg7_lut

76moduleseg7_lut(

77outputreg[6:

0]oseg,

78input[3:

0]idig

79);

80always@(idig)

81begin

82case(idig)

834'h1:

oseg=7'b1111001;//---t---

844'h2:

oseg=7'b0100100;//||

854'h3:

oseg=7'b0110000;//ltrt

864'h4:

oseg=7'b0011001;//||

874'h5:

oseg=7'b0010010;//---m---

884'h6:

oseg=7'b0000010;//||

894'h7:

oseg=7

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- DE2 实验练习解答lab4 countersverilogdigital logic 实验 练习 解答 lab4

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx