5半导体存储器习题解答.pdf

5半导体存储器习题解答.pdf

- 文档编号:3175537

- 上传时间:2022-11-19

- 格式:PDF

- 页数:5

- 大小:512.99KB

5半导体存储器习题解答.pdf

《5半导体存储器习题解答.pdf》由会员分享,可在线阅读,更多相关《5半导体存储器习题解答.pdf(5页珍藏版)》请在冰豆网上搜索。

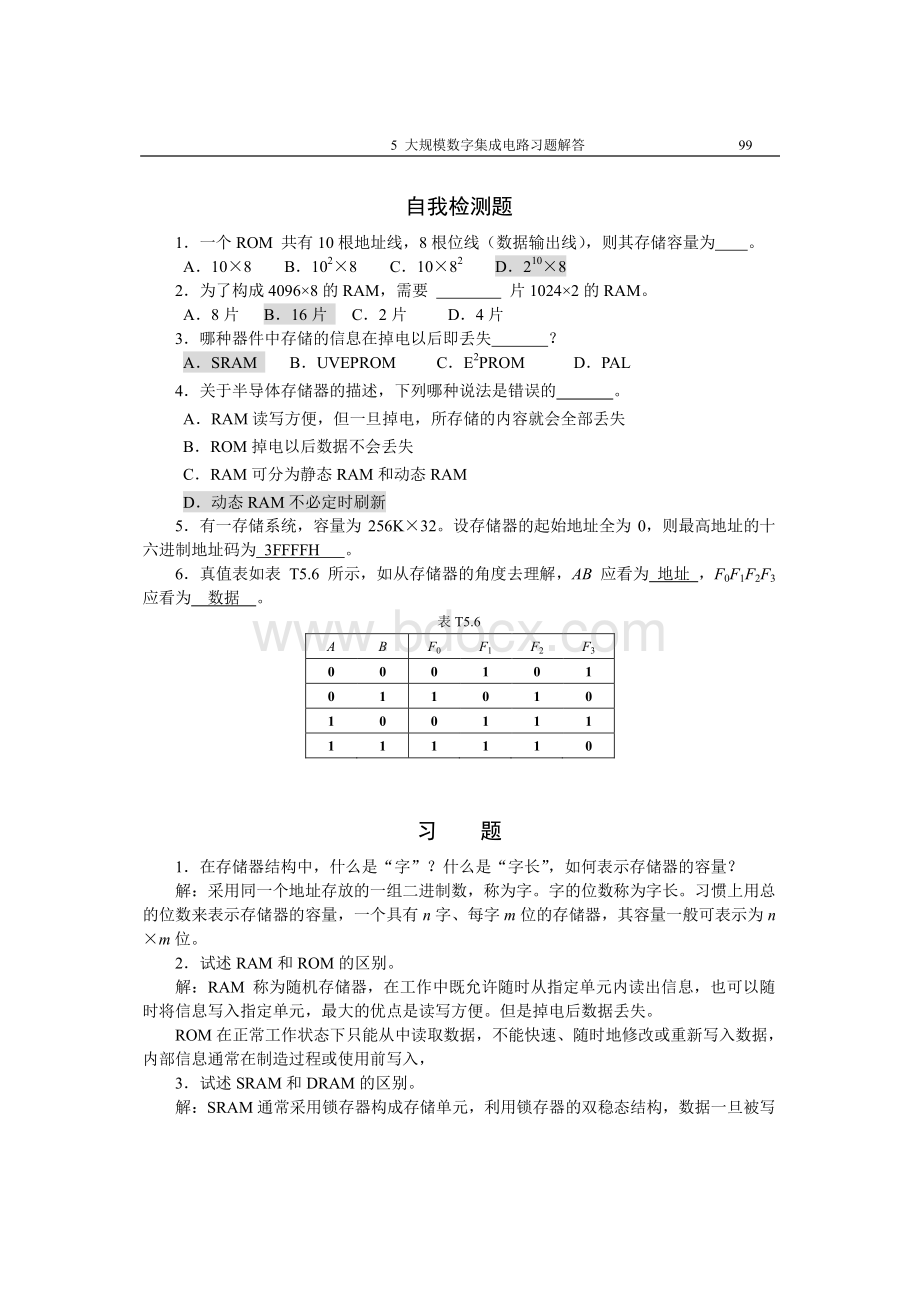

5大规模数字集成电路习题解答99自我检测题1一个ROM共有10根地址线,8根位线(数据输出线),则其存储容量为。

A108B1028C1082D21082为了构成40968的RAM,需要片10242的RAM。

A8片B16片C2片D4片3哪种器件中存储的信息在掉电以后即丢失?

ASRAMBUVEPROMCE2PROMDPAL4关于半导体存储器的描述,下列哪种说法是错误的。

ARAM读写方便,但一旦掉电,所存储的内容就会全部丢失BROM掉电以后数据不会丢失CRAM可分为静态RAM和动态RAMD动态RAM不必定时刷新5有一存储系统,容量为256K32。

设存储器的起始地址全为0,则最高地址的十六进制地址码为3FFFFH。

6真值表如表T5.6所示,如从存储器的角度去理解,AB应看为地址,F0F1F2F3应看为数据。

表T5.6ABF0F1F2F3000101011010100111111110习题1在存储器结构中,什么是“字”?

什么是“字长”,如何表示存储器的容量?

解:

采用同一个地址存放的一组二进制数,称为字。

字的位数称为字长。

习惯上用总的位数来表示存储器的容量,一个具有n字、每字m位的存储器,其容量一般可表示为nm位。

2试述RAM和ROM的区别。

解:

RAM称为随机存储器,在工作中既允许随时从指定单元内读出信息,也可以随时将信息写入指定单元,最大的优点是读写方便。

但是掉电后数据丢失。

ROM在正常工作状态下只能从中读取数据,不能快速、随时地修改或重新写入数据,内部信息通常在制造过程或使用前写入,3试述SRAM和DRAM的区别。

解:

SRAM通常采用锁存器构成存储单元,利用锁存器的双稳态结构,数据一旦被写5大规模数字集成电路习题解答100入就能够稳定地保持下去。

动态存储器则是以电容为存储单元,利用对电容器的充放电来存储信息,例如电容器含有电荷表示状态1,无电荷表示状态0。

根据DRAM的机理,电容内部的电荷需要维持在一定的水平才能保证内部信息的正确性。

因此,DRAM在使用时需要定时地进行信息刷新,不允许由于电容漏电导致数据信息逐渐减弱或消失。

4与SRAM相比,闪烁存储器有何主要优点?

解:

容量大,掉电后数据不会丢失。

5用ROM实现两个4位二进制数相乘,试问:

该ROM需要有多少根地址线?

多少根数据线?

其存储容量为多少?

解:

8根地址线,8根数据线。

其容量为2568。

6现有如图P5.6所示的44位RAM若干片,现要把它们扩展成88位RAM。

(1)试问需要几片44位RAM?

(2)画出扩展后电路图(可用少量门电路)。

44RAMD3D2D1D0A0A1CS图P5.6解:

(1)用44位RAM扩展成88位RAM时,需进行字数和位数扩展,故需要4片44的RAM

(2)扩展后电路如图:

144RAMD3D2D1D0A0A1CS44RAMD3D2D1D0A0A1CS44RAMD3D2D1D0A0A1CS44RAMD3D2D1D0A0A1CSD7D6D5D4A0A1D3D2D1D0A27在微机中,CPU要对存储器进行读写操作,首先要由地址总线给出地址信息,然后发出相应读或写的控制信号,最后才能在数据总线上进行信息交流。

现有2564位的RAM二片,组成一个页面,现需4个页面的存储容量,画出用2564位组成1K8位的RAM框图,并指出各个页面的地址分配。

解:

电路连接图如图所示。

从左到右四个页面的地址为:

000H0FFH,100H1FFH,200H2FFH,300H3FFH。

5大规模数字集成电路习题解答101D7D6D5D4D3D2D1D02564RAMD3D2D1D0A0A7CS2564RAMD3D2D1D0A0A7CS882564RAMD3D2D1D0A0A7CS2564RAMD3D2D1D0A0A7CS882564RAMD3D2D1D0A0A7CS2564RAMD3D2D1D0A0A7CS882564RAMD3D2D1D0A0A7CS2564RAMD3D2D1D0A0A7CS88A0A1EY0Y1Y2A8A9Y3A0A78试用42位容量的ROM实现半加器的逻辑功能,并直接在图P5.8中画出用ROM点阵图实现的半加法器电路。

11或逻辑阵列与逻辑阵列ABSiCi图P5.311或逻辑阵列与逻辑阵列ABiSiC11或逻辑阵列与逻辑阵列ABiSiC5大规模数字集成电路习题解答102解:

由于半加器的输出BABASiABCi所以ROM点阵图如图所示。

9用EPROM实现二进制码与格雷码的相互转换电路,待转换的代码由I3I2I1I0输入,转换后的代码由O3O2O1O0输出。

X为转换方向控制位,当X=0时,实现二进制码到格雷码的转换;当X=1时,实现格雷码到二进制码的转换。

试求:

(1)列出EPROM的地址与内容对应关系真值表;

(2)确定输入变量和输出变量与ROM地址线和数据线对应关系。

解:

真值表为:

XI3I2I1I0O3O2O1O00000000000000100010001000110001100100010001100010101110011001010011101000100011000100111010101011110101111100110010100110110110111010010111110001000000001000100011001000111001100101010001111010101101011001001011101011100011111100111101101011001101111015大规模数字集成电路习题解答103111001000111011001111101011111111010输入变量和输出变量与ROM地址线和数据线对应关系如图所示:

324RAMD3D2D1D0A0A1A3A2XA4I3I2I1I0O3O2O1O0A1A2

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 半导体 存储器 习题 解答

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls