16位定点数原码一位乘法器的设计与实现课程设计报告.docx

16位定点数原码一位乘法器的设计与实现课程设计报告.docx

- 文档编号:3152522

- 上传时间:2022-11-18

- 格式:DOCX

- 页数:18

- 大小:224.06KB

16位定点数原码一位乘法器的设计与实现课程设计报告.docx

《16位定点数原码一位乘法器的设计与实现课程设计报告.docx》由会员分享,可在线阅读,更多相关《16位定点数原码一位乘法器的设计与实现课程设计报告.docx(18页珍藏版)》请在冰豆网上搜索。

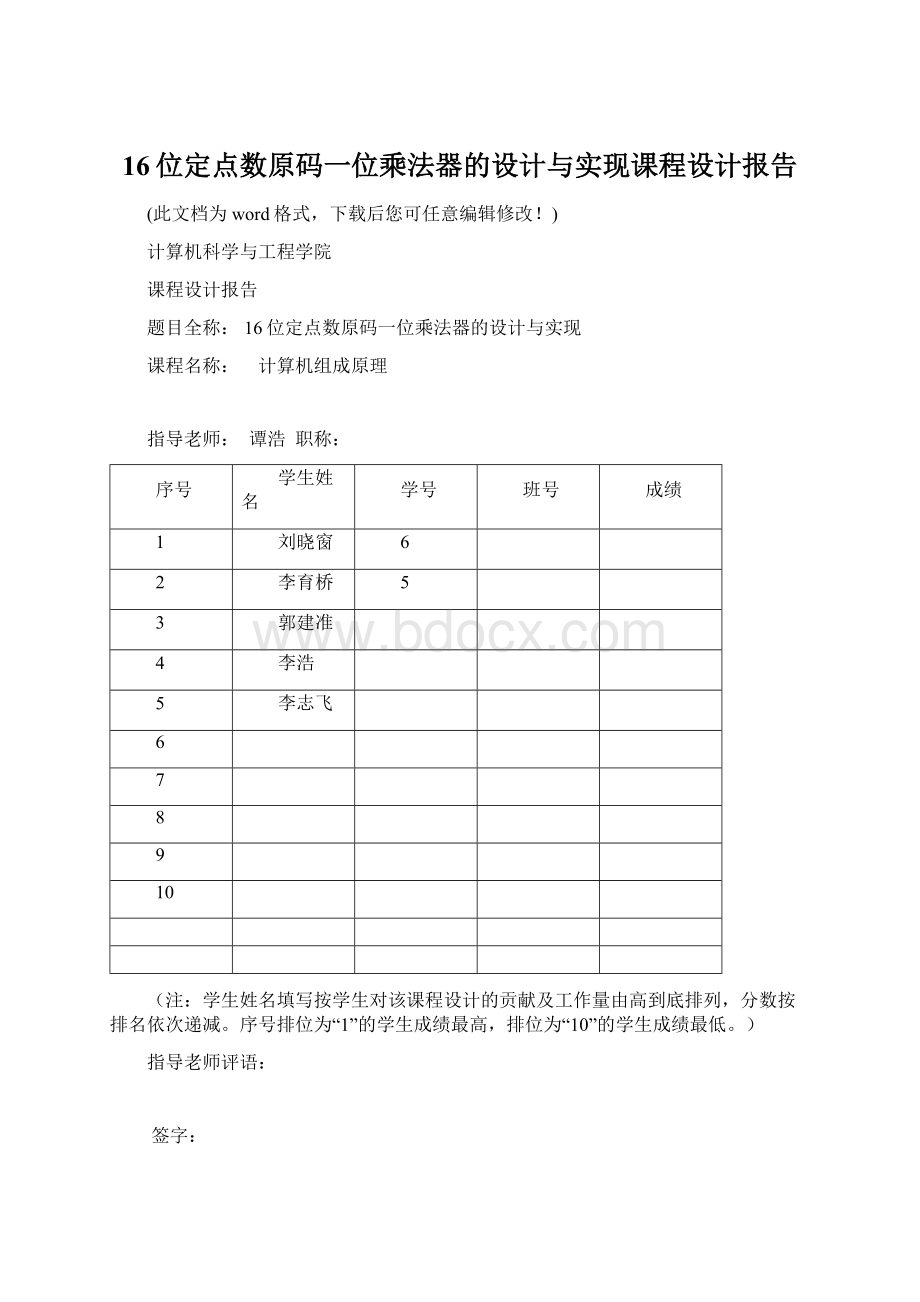

16位定点数原码一位乘法器的设计与实现课程设计报告

(此文档为word格式,下载后您可任意编辑修改!

)

计算机科学与工程学院

课程设计报告

题目全称:

16位定点数原码一位乘法器的设计与实现

课程名称:

计算机组成原理

指导老师:

谭浩职称:

序号

学生姓名

学号

班号

成绩

1

刘晓窗

6

2

李育桥

5

3

郭建准

4

李浩

5

李志飞

6

7

8

9

10

(注:

学生姓名填写按学生对该课程设计的贡献及工作量由高到底排列,分数按排名依次递减。

序号排位为“1”的学生成绩最高,排位为“10”的学生成绩最低。

)

指导老师评语:

签字:

摘要

VerilogHDL语言具有下述描述能力:

设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

本实验用VerilogHDL语言设计了全加器实现的组合乘法器,通过功能仿真,验证了结果。

关键词:

乘法器,Verilog,组合逻辑,全加器

ABSTRACT

Text….

Keywords:

目录

(自动插入目录)

第一章绪论1

1.1选题背景及意义1

1.2国内外研究现状1

1.3主要内容与章节安排1

1.4本章小结1

第二章课程设计的需求分析3

2.1环境需求3

2.2功能需求3

2.3性能需求3

2.3本章小结3

第三章****的设计5

3.1总体设计5

3.2功能模块设计5

3.3本章小结5

第四章****的实现7

4.1开发环境介绍7

4.2主要功能模块的实现7

4.3本章小结7

第五章测试及成果展示9

5.1测试环境9

5.2测试用例和结果9

5.3成果展示9

5.4本章小结9

第六章总结与展望11

参考文献12

第一章绪论

1.1选题背景及意义

随着计算机科学技术的发展,人们获得信息的途径更加多样,获取信息的速度更加快捷。

硬件的发展允许程序员编出很多精彩的使用软件,也使得计算机更加普及。

中央处理器CPU的好坏是影响和制约计算机速度和性能的关键因素。

而加法器是组成CPU的的重要部件,一般运算速度的快慢就取决与每秒执行加法的次数,加法器是算术逻辑单元中的基本逻辑器件。

例如:

为了节省资源,减法器和硬件乘法器都可由加法器来构成。

1.2国内外研究现状

1.3主要内容与章节安排

1.4本章小结

第二章课程设计的需求分析

2.1环境需求

PC、win7、ise7.1、xc3s100e-4vq100芯片、

2.2功能需求

x、y为两个16位定点数,z为32位数,作为输出。

实现16位定点数乘法。

2.3性能需求

2.3本章小结

第三章16位乘法器的设计

3.1总体设计

3.2功能模块设计

3.3本章小结

第四章****的实现

4.1开发环境介绍

4.2主要功能模块的实现

modulemulti16(x,y,clock,z);

input[15:

0]x,y;//定义乘数

inputclock;//定义时钟clock

output[31:

0]z;//定义和的输出z

reg[15:

0]reg_x;//定义寄存器x

reg[15:

0]reg_y;//定义寄存器y

reg[31:

0]reg_z;//定义寄存器z

wire[16:

0]p0,p1,p2,p3,p4,p5,p6,p7,p8,p9,p10,p11,p12,p13,p14,p15;//定义分别用来存储a十六位与b的每一位相与的结果

wire[75:

0]j1,k1;

wire[50:

0]j2,k2;

wire[32:

0]j3,k3;

wire[22:

0]j4,k4;

wire[15:

0]j5,k5;

wire[6:

0]j6,k6;

wire[2:

0]j7,k7;

wire[8:

0]j8,k8;

wire[21:

0]j9,k9;

assignz=reg_z;//将寄存器z的内容赋给输出和z

always@(posedgeclock)//时序逻辑语句块

begin

reg_x<=x;//将加数x的值存到寄存器reg_x中

reg_y<=y;//将被加数y的值存到寄存器reg_y中

reg_z<={j9[21],k9[21],k9[20],k9[19],k9[18],k9[17],k9[16],k9[15],k9[14],k9[13],k9[12],

k9[11],k9[10],k9[9],k9[8],k9[7],k9[6],k9[5],k9[4],k9[3],k9[2],k9[1],k9[0],k8[0],k7[0],

k6[0],k5[0],k4[0],k3[0],k2[0],k1[0],p0[0]};//分别求得的和的每一位赋给reg_z

end

//对a的16位与b的每一位相与

pppp0(reg_x,reg_y[0],p0);

pppp1(reg_x,reg_y[1],p1);

pppp2(reg_x,reg_y[2],p2);

pppp3(reg_x,reg_y[3],p3);

pppp4(reg_x,reg_y[4],p4);

pppp5(reg_x,reg_y[5],p5);

pppp6(reg_x,reg_y[6],p6);

pppp7(reg_x,reg_y[7],p7);

pppp8(reg_x,reg_y[8],p8);

pppp9(reg_x,reg_y[9],p9);

pppp10(reg_x,reg_y[10],p10);

pppp11(reg_x,reg_y[11],p11);

pppp12(reg_x,reg_y[12],p12);

pppp13(reg_x,reg_y[13],p13);

pppp14(reg_x,reg_y[14],p14);

pppp15(reg_x,reg_y[15],p15);

//调用全加器与半加器,通过实例化求得和的每一位与每位的进位信号

halfadderha1(p0[1],p1[0],k1[0],j1[0]);

fulladderfa1(p0[2],p1[1],p2[0],k1[1],j1[1]);

fulladderfa2(p0[3],p1[2],p2[1],k1[2],j1[2]);

fulladderfa3(p0[4],p1[3],p2[2],k1[3],j1[3]);

fulladderfa4(p0[5],p1[4],p2[3],k1[4],j1[4]);

fulladderfa5(p0[6],p1[5],p2[4],k1[5],j1[5]);

fulladderfa6(p0[7],p1[6],p2[5],k1[6],j1[6]);

fulladderfa7(p0[8],p1[7],p2[6],k1[7],j1[7]);

fulladderfa8(p0[9],p1[8],p2[7],k1[8],j1[8]);

fulladderfa9(p0[10],p1[9],p2[8],k1[9],j1[9]);

fulladderfa10(p0[11],p1[10],p2[9],k1[10],j1[10]);

fulladderfa11(p0[12],p1[11],p2[10],k1[11],j1[11]);

fulladderfa12(p0[13],p1[12],p2[11],k1[12],j1[12]);

fulladderfa13(p0[14],p1[13],p2[12],k1[13],j1[13]);

fulladderfa14(p0[15],p1[14],p2[13],k1[14],j1[14]);

fulladderfa15(p1[15],p2[14],p3[13],k1[15],j1[15]);

fulladderfa16(p2[15],p3[14],p4[13],k1[16],j1[16]);

fulladderfa17(p3[15],p4[14],p5[13],k1[17],j1[17]);

fulladderfa18(p4[15],p5[14],p6[13],k1[18],j1[18]);

fulladderfa19(p5[15],p6[14],p7[13],k1[19],j1[19]);

fulladderfa20(p6[15],p7[14],p8[13],k1[20],j1[20]);

fulladderfa21(p7[15],p8[14],p9[13],k1[21],j1[21]);

fulladderfa22(p8[15],p9[14],p10[13],k1[22],j1[22]);

fulladderfa23(p9[15],p10[14],p11[13],k1[23],j1[23]);

fulladderfa24(p10[15],p11[14],p12[13],k1[24],j1[24]);

fulladderfa25(p11[15],p12[14],p13[13],k1[25],j1[25]);

fulladderfa26(p12[15],p13[14],p14[13],k1[26],j1[26]);

fulladderfa27(p13[15],p14[14],p15[13],k1[27],j1[27]);

fulladderfa28(p3[2],p4[1],p5[0],k1[28],j1[28]);

fulladderfa29(p3[3],p4[2],p5[1],k1[29],j1[29]);

fulladderfa30(p3[4],p4[3],p5[2],k1[30],j1[30]);

fulladderfa31(p3[5],p4[4],p5[3],k1[31],j1[31]);

fulladderfa32(p3[6],p4[5],p5[4],k1[32],j1[32]);

fulladderfa33(p3[7],p4[6],p5[5],k1[33],j1[33]);

fulladderfa34(p3[8],p4[7],p5[6],k1[34],j1[34]);

fulladderfa35(p3[9],p4[8],p5[7],k1[35],j1[35]);

fulladderfa36(p3[10],p4[9],p5[8],k1[36],j1[36]);

fulladderfa37(p3[11],p4[10],p5[9],k1[37],j1[37]);

fulladderfa38(p3[12],p4[11],p5[10],k1[38],j1[38]);

fulladderfa39(p4[12],p5[11],p6[10],k1[39],j1[39]);

fulladderfa40(p5[12],p6[11],p7[10],k1[40],j1[40]);

fulladderfa41(p6[12],p7[11],p8[10],k1[41],j1[41]);

fulladderfa42(p7[12],p8[11],p9[10],k1[42],j1[42]);

fulladderfa43(p8[12

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 16 定点 数原码 一位 乘法器 设计 实现 课程设计 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx