EDA期末复习资料.docx

EDA期末复习资料.docx

- 文档编号:30702422

- 上传时间:2023-08-19

- 格式:DOCX

- 页数:38

- 大小:242.38KB

EDA期末复习资料.docx

《EDA期末复习资料.docx》由会员分享,可在线阅读,更多相关《EDA期末复习资料.docx(38页珍藏版)》请在冰豆网上搜索。

EDA期末复习资料

湖南工程学院-贺富朋-EDA期末复习资料

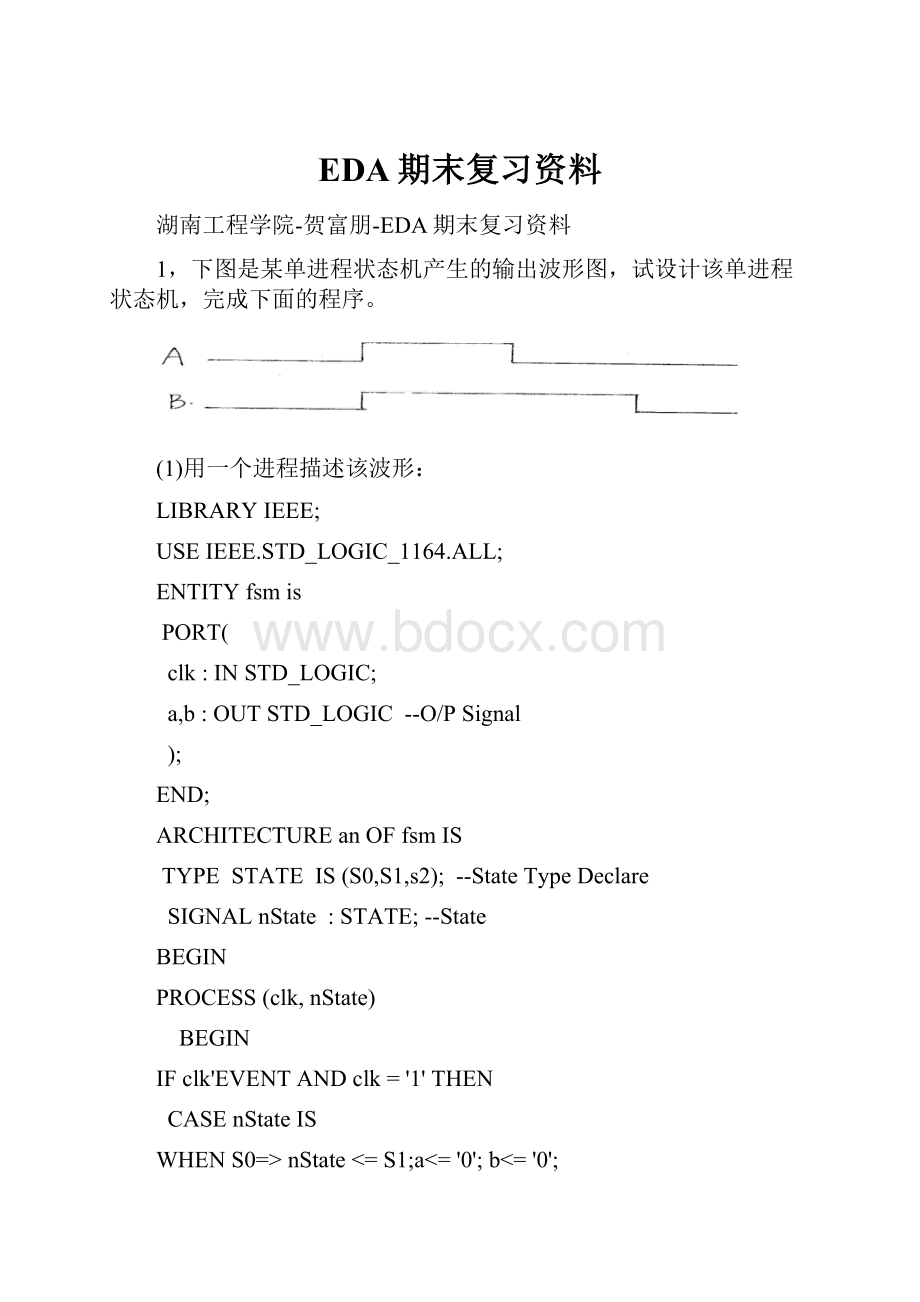

1,下图是某单进程状态机产生的输出波形图,试设计该单进程状态机,完成下面的程序。

(1)用一个进程描述该波形:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYfsmis

PORT(

clk:

INSTD_LOGIC;

a,b:

OUTSTD_LOGIC--O/PSignal

);

END;

ARCHITECTUREanOFfsmIS

TYPESTATEIS(S0,S1,s2);--StateTypeDeclare

SIGNALnState:

STATE;--State

BEGIN

PROCESS(clk,nState)

BEGIN

IFclk'EVENTANDclk='1'THEN

CASEnStateIS

WHENS0=>nState<=S1;a<='0';b<='0';

WHENS1=>nState<=S2;a<='1';b<='1';

WHENS2=>nState<=S0;a<='0';b<='1';

WHENOTHERS=>nState<=S0;a<='0';b<='0';

ENDCASE;

ENDIF;

ENDPROCESS;

ENDan;

(2)用两个进程描述该波形:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYfsmis

PORT(

clk:

INSTD_LOGIC;

a,b:

OUTSTD_LOGIC--O/PSignal

);

END;

ARCHITECTUREanOFfsmIS

TYPESTATEIS(S0,S1,s2);--StateTypeDeclare

SIGNALnState:

STATE;--State

BEGIN

PROCESS(clk,nState)

BEGIN

IFclk'EVENTANDclk='1'THEN

CASEnStateIS

WHENS0=>nState<=S1;

WHENS1=>nState<=S2;

WHENS2=>nState<=S0;

WHENOTHERS=>nState<=S0;

ENDCASE;

ENDIF;

ENDPROCESS;

PROCESS(CLK,nSTATE)

BEGIN

IFclk'EVENTANDclk='1'THEN

CASEnSTATEIS

WHENS0=>a<='0';b<='0';

WHENS1=>a<='1';b<='1';

WHENS2=>a<='0';b<='1';

WHENOTHERS=>a<='0';b<='0';

ENDCASE;

ENDIF;

ENDPROCESS;

ENDan;

2,现有频率为8000Hz的时钟信号CLK,试设计一个程序同时产生500Hz,250Hz,125Hz三个低频时钟信号。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcntis

PORT(

clk:

INSTD_LOGIC;

Q3,Q4,Q5:

OUTSTD_LOGIC--O/PSignal

);

END;

ARCHITECTUREbhvOFcntIS

SIGNALQ1:

STD_LOGIC_VECTOR(5DOWNTO0);

BEGIN

PROCESS(clk)

BEGIN

IFclk'EVENTANDclk='1'

THENQ1<=Q1+1;

ENDIF;

ENDPROCESS;

Q3<=Q1(3);Q4<=Q1(4);Q5<=Q1(5);

ENDbhv;

3.

其实体是程序是:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC

);

END;

(1)用一个进程描述该电路:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC

);

END;

ARCHITECTUREbhvOFDFF3IS

SIGNALA,B:

STD_LOGIC;

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'

THEN

A<=D1;

B<=A;

Q1<=B;

ENDIF;

ENDPROCESS;

END;

(2)用三个进程描述该电路

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC

);

END;

ARCHITECTUREbhvOFDFF3IS

SIGNALA,B:

STD_LOGIC;

BEGIN

PROCESS(CLK,D1)

BEGIN

IFCLK'EVENTANDCLK='1'

THEN

A<=D1;

ENDIF;

ENDPROCESS;

PROCESS(CLK,A)

BEGIN

IFCLK'EVENTANDCLK='1'

THEN

B<=A;

ENDIF;

ENDPROCESS;

PROCESS(CLK,B)

BEGIN

IFCLK'EVENTANDCLK='1'

THEN

Q1<=B;

ENDIF;

ENDPROCESS;

END;

(3)用元件例化语句描述该电路:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYHANIS

PORT(CLK_IN,D_IN:

INSTD_LOGIC;

Q_OUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREf_dff3OFHANIS

COMPONENTDFF3

PORT(CLK,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALA,B:

STD_LOGIC;

BEGIN

U1:

DFF3PORTMAP(CLK=>CLK_IN,D=>D_IN,Q=>A);

U2:

DFF3PORTMAP(CLK=>CLK_IN,D=>A,Q=>B);

U3:

DFF3PORTMAP(CLK=>CLK_IN,D=>B,Q=>Q_OUT);

ENDf_dff3;

(4)用生成语句描述该电路:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF2IS

PORT(CLK1,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

END;

ARCHITECTUREONEOFDFF2IS

SIGNALQ2:

STD_LOGIC;

BEGIN

PROCESS(CLK1,Q2)BEGIN

IFCLK1'EVENTANDCLK1='1'

THENQ2<=D;

ENDIF;

ENDPROCESS;

Q<=Q2;

ENDONE;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC);

ENDDFF3;

ARCHITECTUREbhvOFDFF3IS

COMPONENTDFF2

PORT(CLK1,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALtemp:

STD_LOGIC_VECTOR(0TO3);

BEGIN

temp(0)<=D1;

M:

FORiIN0TO2GENERATE

U:

DFF2PORTMAP(CLK1=>CLK,D=>temp(i),Q=>TEMP(i+1));

Q1<=temp(3);

ENDGENERATE;

ENDbhv;

4.如题图所示由触发器组成的顶层电路,完成下面的程序。

(1)用一个进程描述该电路;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYshejiIS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC);

END;

ARCHITECTUREbhvOFshejiIS

SIGNALB:

STD_LOGIC;

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THENB<=notD1;

Q1<=B;

ENDIF;

ENDPROCESS;

ENDbhv;

(2)用两个进程描述该电路;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYPROIS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC);

END;

ARCHITECTUREBHVOFPROIS

SIGNALB:

STD_LOGIC;

BEGIN

PROCESS(CLK,D1)BEGIN

IFCLK'EVENTANDCLK='1'THENB<=NOTD1;

ENDIF;

ENDPROCESS;

PROCESS(CLK,B)BEGIN

IFCLK'EVENTANDCLK='1'THENQ1<=B;

ENDIF;

ENDPROCESS;

ENDBHV;

(3)用元件例化语句描述该电路。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF2IS

PORT(CLK1,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

END;

ARCHITECTUREONEOFDFF2IS

SIGNALQ2:

STD_LOGIC;

BEGIN

PROCESS(CLK1,Q2)BEGIN

IFCLK1'EVENTANDCLK1='1'

THENQ2<=D;

ENDIF;

ENDPROCESS;

Q<=Q2;

ENDONE;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYPLANIS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC);

END;

ARCHITECTUREBHVOFPLANIS

COMPONENTDFF2IS

PORT(CLK1,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALa:

STD_LOGIC;

BEGIN

U1:

DFF2PORTMAP(CLK1=>CLK,D=>NOTD1,Q=>a);

U2:

DFF2PORTMAP(CLK1=>CLK,D=>a,Q=>Q1);

ENDBHV;

(4)该电路延时多少时钟周期?

(2个时钟周期)。

(5)用生成语句描述该电路。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

END;

ARCHITECTUREbhvOFDFF3IS

SIGNALQ1:

STD_LOGIC;

BEGIN

PROCESS(CLK,Q1)

BEGIN

IFCLK'EVENTANDCLK='1'

THENQ1<=D;

ENDIF;

ENDPROCESS;

Q<=Q1;

ENDbhv;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYd_ffIS

GENERIC(n:

INTEGER:

=2);

PORT(CLK_IN,D_IN:

INSTD_LOGIC;

Q_OUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREHANOFd_ffIS

COMPONENTDFF3

PORT(CLK,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALS:

STD_LOGIC_VECTOR(0TOn);

BEGIN

S(0)<=NOTD_IN;

q_1:

FORiIN0TOn-1GENERATE

DFF_3:

DFF3PORTMAP(CLK_IN,S(i),S(i+1));

ENDGENERATE;

Q_OUT<=S

(2);

ENDHAN;

5.LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC);

END;

ARCHITECTUREbhvOFDFF3IS

SIGNALB:

STD_LOGIC;

BEGIN

PROCESS(CLK)BEGIN

IFCLK'EVENTANDCLK='1'THEN

B<=D1;

Q1<=B;

ENDIF;

ENDPROCESS;

END;

试分析上述程序实现的功能,画出对应的RTL图。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

END;

ARCHITECTUREbhvOFDFF3IS

SIGNALQ1:

STD_LOGIC;

BEGIN

PROCESS(CLK,Q1)

BEGIN

IFCLK'EVENTANDCLK='1'

THENQ1<=D;

ENDIF;

ENDPROCESS;

Q<=Q1;

ENDbhv;

6.已知时钟信号周期为10ms,设计一个延时40ms的时序电路。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF3IS

PORT(CLK,D1:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC);

END;

ARCHITECTUREbhvOFDFF3IS

SIGNALA,B,C:

STD_LOGIC;

BEGIN

PROCESS(CLK)BEGIN

IFCLK'EVENTANDCLK='1'THEN

A<=D1;

B<=A;

C<=B;

Q1<=C;

ENDIF;

ENDPROCESS;

END;

7.LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSeg7_Dspis

PORT(CP:

INSTD_LOGIC;

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDSeg7_Dsp;

ARCHITECTUREaOFtestIS

BEGIN

variableQ:

STD_LOGIC_VECTOR(24DOWNTO0);

PROCESS(CP)

Begin

IFCP'EventANDCP='1'then

Q<=Q+1;

ENDIF;

ENDPROCESS;

OUTY<=Q(20DOWNTO17);

Enda;

根据上面的程序解答如下问题:

(1)分析语句USEIEEE.STD_LOGIC_UNSIGNED.ALL;的必要性;

【课本87页】

(2)找出程序中的两处错误并修改。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSeg7_Dspis

PORT(CP:

INSTD_LOGIC;

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDSeg7_Dsp;

ARCHITECTUREaOFSeg7_DspIS

SIGNALQ:

STD_LOGIC_VECTOR(24DOWNTO0);

BEGIN

PROCESS(CP)

Begin

IFCP'EventANDCP='1'then

Q<=Q+1;

ENDIF;

ENDPROCESS;

OUTY<=Q(20DOWNTO17);

Enda;

(3)已知时钟cp的频率为3.93MHz,计算输出信号outy的频率。

【频率由低位确定】

8.在“八位数码扫描显示电路设计”的实验中,

(1)复述你的实验过程;

(2)假如实验台有两个时钟源:

168Hz和268Hz,为达到同时显示的效果,选择哪一个?

为什么?

(1)新建一个文件夹,打开QuartusII,选择File

New命令,输入源程序,选择File

SaveAs命令,使得文件存盘,创建工程并设置相关参数之后,全程编译。

选择File

New命令,在New窗口选择VectorWaveformFile选项进行时序仿真。

选择Assignments

AssignmentEditor命令进行引脚锁定,在工程管理窗口选择Tool

Programmer命令然后设置编辑器,下载进行硬件测试。

(2)8位为:

8x24=192>168,所以选择268Hz

9.五位加法器采用二级流水线【

八位加法器采用二级流水线】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

ENTITYCNT5IS

PORT(A,B:

INSTD_LOGIC_VECTOR(4DOWNTO0);

CLK,CIN:

INSTD_LOGIC;

COUT:

OUTSTD_LOGIC;

SUM:

OUTSTD_LOGIC_VECTOR(4DOWNTO0));

ENDCNT5;

ARCHITECTURErt1OFCNT5IS

SIGNALAB3:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALS:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(CLK)BEGIN

IF(RISING_EDGE(CLK))

THENAB3<=('0'&A(1DOWNTO0))+('0'&B(1DOWNTO0))+CIN;

SUM(1DOWNTO0)<=AB3(1DOWNTO0);

ENDIF;

ENDPROCESS;

PROCESS(CLK)BEGIN

IF(RISING_EDGE(CLK))

THENS<=('0'&A(4DOWNTO2))+('0'&B(4DOWNTO2))+AB3

(2);

ENDIF;

ENDPROCESS;

COUT<=S(3);SUM(4DOWNTO2)<=S(2DOWNTO0);

ENDrt1;

10.根据汉字,写出对应的MIF文件。

DEPTH=32;

WIDTH=8;

ADDRESS_RADIX=HEX;

DATA_RADIX=HEX;

CONTENT

BEGIN

0000:

0x00;

…

…

…

001F:

0x00;

END;

11

(1)用元件例化语句描述该电路;

(2)用生成语句描述该电路;

(3)分析该电路的功能;

(4)如何将改电路改为八进制计数器?

12,找好处,找出父母亲的十个好处和三个难处?

1.以下关于适配描述错误的是B(P14)

A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件

B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列

C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真

D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供

2.以下关于CASE语句描述中错误的是A

A.CASE语句执行中可以不必选中所列条件名的一条

B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHENOTHERS=><顺序语句>”

C.CASE语句中的选择值只能出现一次

D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 期末 复习资料

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx