数字电子电路仿真.docx

数字电子电路仿真.docx

- 文档编号:30450982

- 上传时间:2023-08-15

- 格式:DOCX

- 页数:35

- 大小:1.76MB

数字电子电路仿真.docx

《数字电子电路仿真.docx》由会员分享,可在线阅读,更多相关《数字电子电路仿真.docx(35页珍藏版)》请在冰豆网上搜索。

数字电子电路仿真

第八章数字电子电路仿真

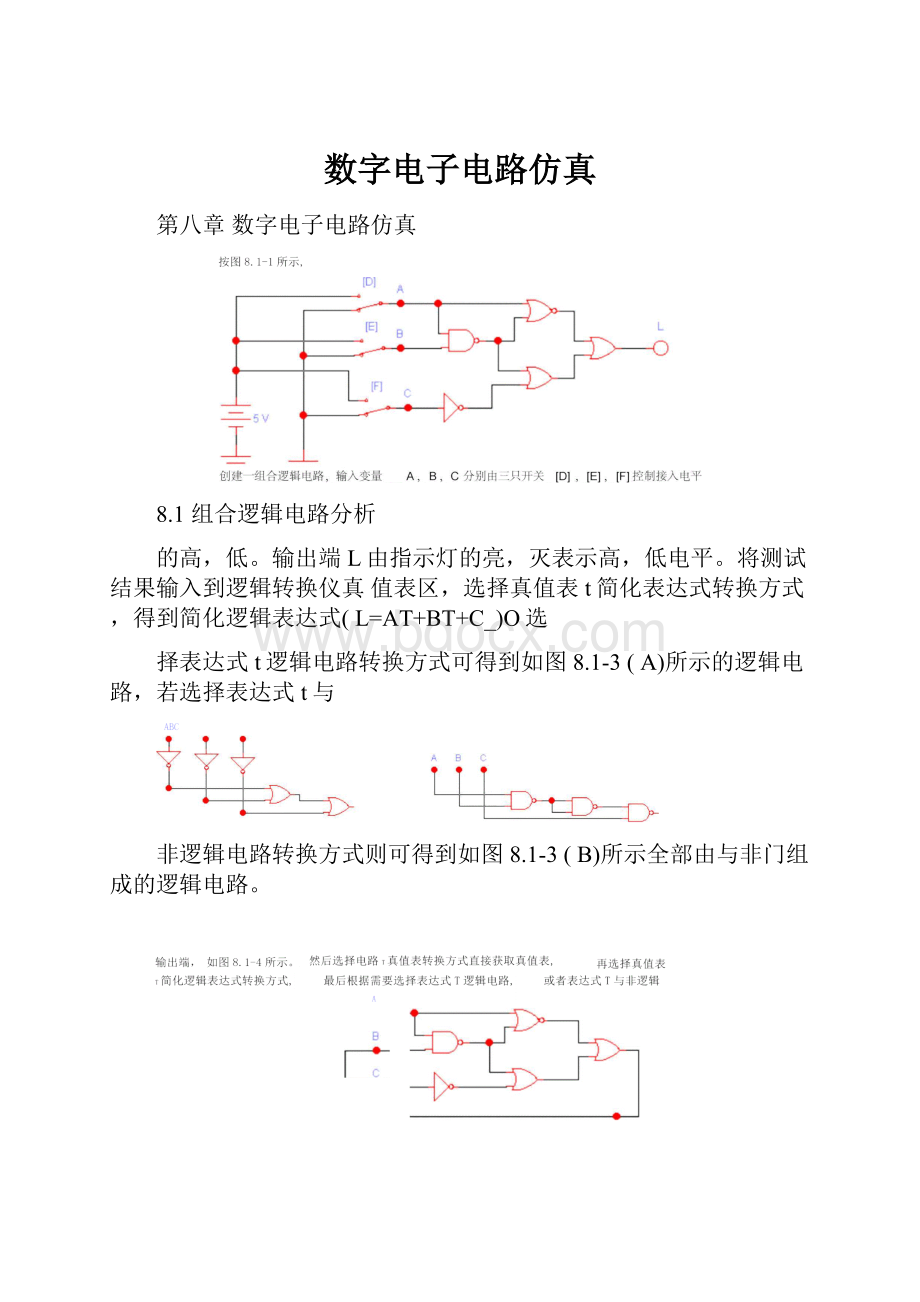

8.1组合逻辑电路分析

的高,低。

输出端L由指示灯的亮,灭表示高,低电平。

将测试结果输入到逻辑转换仪真值表区,选择真值表t简化表达式转换方式,得到简化逻辑表达式(L=AT+BT+C_)O选

择表达式t逻辑电路转换方式可得到如图8.1-3(A)所示的逻辑电路,若选择表达式t与

非逻辑电路转换方式则可得到如图8.1-3(B)所示全部由与非门组成的逻辑电路。

要获取给定组合逻辑电路的真值表,除了可以用上述直接测试的方法以外,还可以将创建好的逻辑电路输入端连接至逻辑转换仪的输入端,将电路的输出端连接至逻辑转换仪的

电路获得简化的逻辑电路。

8.2组合逻辑电路设计

一般组合逻辑电路设计过程可归纳为:

分析给定问题列出真值表,由真值表求得简化的

逻辑表达式,再根据表达式画出逻辑电路。

这一过程可借助逻辑转换仪完成。

例:

试设计一个路灯控制逻辑电路,要求在四个不同的地方都能独立的控制路灯的亮灭。

解:

设该逻辑电路四个输入变量为:

AB,C,D,分别由[E],[F],[G],[H]四个开关控制,接入高电平(+5V作为逻辑“1”,接入低电平(“地”)作为逻辑“0”。

逻辑电路输出端L接一指示灯模拟所控制的路灯,输出高电平(逻辑“1”)时指示灯亮,输出低电平(逻辑“0”)时指示灯灭。

(1)打开逻辑转换仪面板,在真值表区电击A,B,C,D四个逻辑变量建立一个四变量真值表,根据逻辑控制要求在真值表区输出变量列中填入相应逻辑值

(2)点击逻辑转换仪面板上“真值表t简化逻辑表达式”按钮,求得简化的逻辑表达式。

(3)点击逻辑转换仪面板上“表达示t电路”按钮,获得逻辑电路如图8.2-2(虚线以下部分)所示。

(4)逻辑功能测试:

在通过逻辑转换仪获得的逻辑电路四个输入端接入四个开关,用来选择“+5V)或“地”,输出端L接指示灯,如图8.2-2虚线以上部分所示。

按上述方式选择不同的开关状态组合,观察指示灯的亮灭可对真值表的状态逐一验证。

8.3组合逻辑常见功能测试

通过对逻辑部件的功能测试,有助于加深对该部件逻辑功能的理解,为熟悉应用该部件打下基础,同时进一不熟悉有关测试一起的使用方法。

例i全加器逻辑功能测试:

(1)打开EWB的主界面,从数字器件库中调出全加器,再从仪器库中调出逻辑转换

仪,将全加器的输入端A,B,C1分别与逻辑转换仪输入端A,B,C相连,将全加器的输出端刀与CO通过选择开关S与逻辑转换仪输出端相连,得全加器测

OOOOOCOO◎

试电路如图8.3-1所示。

(2)点击(选中)全加器,再点击帮助按钮(?

),得到全加器的功能表。

(3)通过选择开关S将全加和(刀)端连至逻辑转换仪输出端,双击逻辑转换仪图标,

展开逻辑转换仪面板,单击逻辑电路t真值表按钮可获得全加和真值表,单击真

值表t简化表达式按钮可获得简化的逻辑表达式。

(4)通过选择开关S将全加器进位输出端CO与逻辑转换仪输出端相连,展开逻辑转换仪面板,单击逻辑电路t真值表按钮可获得全加进为真值表,单击真值表t简化表达式按钮可获得简化的逻辑表达式。

例2多路数据选择器功能测试

(1)在EWB主界面中打开数字器件库,选择八选一数据选择器74151,其功能表

(略),逻辑符号参见图8.3-6。

功能表中C,B,A为通道地址选择。

G—为使能端,低电平有效。

Y为数据输出端,W为反相数据输出端。

(2)由仪器库中调出字信号发生器和逻辑分析仪,将数据选择器的八个输入通道

(DO〜D7)分别与字信号发生器的八个输出段和逻辑分析仪的八个输入端项链。

将数据选择器的数据输出端(Y)和反相数据输出端(W分别连到逻辑分析仪的两个输入端。

将通道地址输入端(C,B,A)分别通过三个开关([C],[B],[A])选择高,低电平,实现通道地址编码。

测试电路连接如图8.3-6所示。

在字信号编辑区内写入两位不同的

1KHZ

(3)设置字信号发生器。

展开字信号发生器面板,十六进制数。

选择字信号发生器的工作频率为

(4)多路数据选择器功能测试。

通过改变开关[C],[B],[A]的连接方式,选择多路

数据选择器的一路输入通道(图8.3-6选择了DO通道)。

展开逻辑分析仪面板,

按下启动开关,逻辑分析仪面板上将展现出多路数据选择器的工作波形。

按下暂

停按钮,可仔细观察各波形之间的逻辑关系。

可连续改变通道地址观察输出与输

入通道之间的选择关系。

8.4递增集成计数器的应用

在EWB主界面下打开数字器件库,选择集成计数器74160,其电路符号见图8.4-3所示。

1.74160基本功能测试

74160为一具有清零与置数功能的十进制递增计数器,由显示器件库中选择带译码器的七段显示数码管与计数器输出端相连,在信号源中选择方波电压(频率1KHZ,占空比

50%,幅值5V)作为计数器的时钟脉冲源,将脉冲源及计数器输出端连接至逻辑分析仪输入端便于观察波形,所连电路如图8.4-3所示。

在EW吐界面内建立图8.4-3所示电路后,可按功能表要求,在清零(CLR与置数端

(LOAD)分别接入相应电平可测试清零与置数功能。

闭合仿真电源开关,双击逻辑分析仪

图标可观测到计数器工作波形。

由上到下依次为时钟脉冲(CLK),QAQBQCQD和进位

控制脉冲(RCO波形。

两个读数指针之间为一个计数周期的工作波形。

2.用“反馈清零”法组成任意进制递增计数器

在实际工作中,经常需要组成非十进制(N进制)递增计数器,欲组成N进制递增计数器,只要将计数器第N状态中输出为“1”的Q端,经与非门“与非”后控制清零端(CLR即可(因为计数器74160清零端低电平有效)。

例如:

我们将74160输出端QA和QD通过与非门控制计数器的清零端,即可将十进制递增计数器74160改造成九进制递增计数器,改造后的电路如图8.4-6所示。

两读数指针之间为一个九进制计数周期工作波形。

显然,通过选择计数器不同输出端作为反馈端,利用一片74160可组成10以内任意进

制递增计数器。

8.5集成可逆计数器的应用

在EWB主界面下打开数字器件库,选取十进制可逆集成计数器74190,其电路符号见图8.5-2。

1.74190功能测试

74190为一具有置数功能的十进制可逆计数器,由显示器件库中选择带译码器的七段显

示数码管与计数器输出端相连,将脉冲源及计数器输出端连接至逻辑分析仪输入端便于观察波形,所连电路如图8.5-2所示。

通过敲击

K键,控制开关S将减/加(D/U)计数控制端接高电平或低电平,实现十进制递减或递增计数体制的转换。

按功能表要求,可对置数,递增,递减计数进行测试。

图8.5-2为十进制可逆计数器递

减计数工作方式。

闭合仿真电源开关,双击逻辑分析仪图标可观测到计数器工作波形。

由上

到下依次为时钟脉冲(CLK),QAQBQCQD和借位控制脉冲(RCO波形。

敲击K键,使减/加(D/U)控制端通过开关接地,使74190工作在十进制递增计数工作状态。

通过逻辑分析仪显示74190十进制递增计数器工作波形。

2.集成计数器的级连

集成计数器的级连可采用同步或异步两种方式,可根据借位或进位信号以及控制端的特

征而定。

用两片74190采用同步级连方式构成的100进制递减计数器如图8.58-5所示

。

两片74190(C1,C2)分别连接成十进制计数方式,因为个位计数器(C2)的借位信号(RCO

只在“0”状态时输出低电平,将其连接到十位计数器(C1)的计数容许端(CTEN低电平

有效),这样,只有在低位计数器输出的借位信号有效(低电平)时,才允许高电位计数器计数,从而实现了同步级连。

因为集成计数器74190是在时钟脉冲上跳沿触发,因此,我们

可以利用低位计数器的借位输出脉冲直接作高位计数器的触发脉冲。

高低位计数器组成异步

级连方式。

图8.5-6所示66进制递减计数器就是采用异步级连方式。

3.用“反馈置数”方式组成零为无效状态的任意进制递减计数器

选用两片74190分别连接成十进制递减工作方式,将个位计数器的借位信号(RCO连接

到十位计数器的脉冲输入端(CLK组成异步计数方式。

将两片计数器(C1,C2)的RCO端

通过或门控制两片计数器的置数控制端(LOAD,将两片计数器的置数输入端(D,C,B,A)

根据进制要求作适当连接,该减法计数器在“00”状态的瞬间完成置数(可以在100以内任

意选择)。

因此,利用两片74190可组成零状态为无效状态的100以内的任意进制递减计数

器。

图8.5-6为一零为无效状态的66进制递减计数器。

4.用“反馈置数”方式组成零为有效状态的任意进制递减计数器

对十进制递减计数器而言,“0”状态之后,一定是状态“9”,我们可以利用QD和QA相“与”后,完成任意进制置数。

即利用“9”状态出现的瞬间之特征(QD=QA=1,借助置

数控制端LOAD和置数输入端A,B,C,D,将“9”置换为任意进制数“N”。

图8.5-7为一采用异步级连方式的零为有效状态的66进制递减计数器。

图8.4-5是“利用反馈清零”法组成的零有效九进制递增计数器,利用“反馈置数”法

同样也可以组成零为无效状态的任意进制递增计数器,对74190而言,令其工作在递增计数

方式下,同样也可以利用“反馈置数”法组成零状态有效或无效的任意进制递增计数器。

8.6555定时器的应用

1.555定时器及其组成的多谐振荡器

555定时器是一种将模拟功能与逻辑功能巧妙结合在一起的中规模集成电路,其功能灵活,使用范围广,只要外部配上2,3个阻容元件,就可以构成单稳,多谐或施密特电

路。

该电路在定时,检测,控制,报警等方面得到广泛应用。

图8.6-1是利用555定时器构成的多谐振荡器。

Me

电路中左右两片555定时器分别构成两个振荡频率不同的多谐振荡器。

因为左边振荡器的充

放电时间常数远大于右边振荡器的充放电时间常数,因此左振荡器的振荡周期远大于右振荡

器,将左振荡器输出连接到右振荡器的复位端,左振荡器输出高电平时,右振荡器产生高频

振荡,输出低电平时停振,从而构成波群发生器。

3.555定时器组成报警电路

在EWE主界面下打开混合集成电路库,选择两片555定时器并配以适当外围元件组成图8.6-5所示电路,

0.2kOhm

其基本结构与上述波群发生器类似,不同点是将左振荡器的输出接到右振荡器的控制电压输

入端,利用左振荡器的高,低电平控制右振荡器产生两个不同频率的振荡,可推动扬声器产

生报警音响效果。

利用555定时器组成报警电路还有多种方案,例如:

可将左振荡器电容上的三角波电压接至右振荡器的控制电压输入端,使右振荡器产生变频振荡,产生报警效果。

8.7JK触发起及其应用

1.JK触发器功能测试

在数字器件库中取一低电平触发,低电平置位和复位的JK触发器搭成图8.7-1所示的测

试电路。

闭合仿真电源开关,双击逻辑

分析仪图标,展开逻辑分析仪面板,选择合适的时基,得到JK触发器工作电压波形图。

波

形图直观的反映了Q端与时钟脉冲之间的2分频关系,Q'与Q端之间的非逻辑关系,以及时钟脉冲下跳沿与Q和Q'翻转的对应关系。

还可以单独接入高,低电平,观察置位和复位功能。

2.利用JK触发器构成分频器

利用4个JK触发器按二进制同步计数器级连方式进行连接,得图8.7-3所示的十六分频器(四位二进制同步递增计数器)

将时钟脉冲(CLK)及四个触发器的Q端(Q0,Q1,Q2,Q3)自上而下,依次接入逻辑分析仪。

得到工作(时序)波形,显示出触发器输出端Q旷Q3与时钟脉冲之间分别为2,4,8,

16分频关系。

8.8D/A转换器

1.D/A转换电路原理分析

该

电路为R—2RT型D/A转换电路,开关D3,D2,D1,D0分别由关键字D,C,B,A控制接“0”或接“1”。

无论开关接“0”(地)还是接“1”(虚地),电阻网络各支路电流分配关系不变。

Vref为输入基准电压,因为由基准电压VREF端输入的等效电阻为R,因此输入电流

lref=Vref/R,由此进一步分析不难获得输出电压与输入基准电压和各开关量之间的关系式为:

VO=-Vref/16*(D3*8+D2*4+D1*2+D0*1)。

显然:

当D3,D2,D1,D0=0001时,VO=-VREF/16为D/A转换器的分辨率。

当D3,D2,D1,D0=1111时,VO=-15*VREF/16为D/A转换器的满度值。

以上所述,均可通过改变开关位置,观测电流表和电压表显示数值而得到验证。

2.集成D/A转换电路测试

图8.8-2为一集成D/A转换器测试电路

DO〜D7:

八位二进制数码输入,通过开关A〜H选择输入高电平(+VCC或低电平(地)

VO电压输出端。

VREF输入基准电压。

D/A转换器输出电压表达式:

VO=VrefXD/256=10VXD/256其中:

D为输入二进制数码所对应的十进制数。

例:

图8.8-2中输入二进制码为:

10011001,转换成十进制数为:

D=128+16+8+仁153

因此:

VO=10V<153/256=5.977V,与电路实测结果一致。

8.9A/D转换器

图8.9-1为一A/D转换测试电路,

MSALSB

LS-0UF

[別1kOhm/60%

VIMD2

WBF-D4

5DCD5

IDEoa

EGG

其中:

VIN:

模拟电压输入端。

DO〜D7:

二进制数码输入DUAN4

Vref+:

上基准电压输入端。

Vref-:

下基准电压输入端。

SOC:

数据转换启动端(高电平启动)。

OE:

三态输出控制端。

EOC:

转换周期结束指示端(输出正脉冲)。

在图8.9-1所示电路中:

基准电压Vref=5V。

输入模拟电压由电位器R提供,大小由R调节,由电压表指示。

输入模拟电压与输出数字量的关系式:

Vin=(输出数字量所对应的十进制数)X

Vref/256。

输出二进制数:

Bin=VinX256/Vref。

输出二进制数由带译码器的7段LED显示数码管

以两位十六进制数形式显示。

在图8.9-1所示电路中输出数字量理论计算值:

BIN=2VX256/5V=102.4(十进制数)。

数码管显示实际值:

0110010=64+32+4+2=102(十进制数)。

两者基本相符。

8.10锁相环

锁相环是数字频率合成的核心部件,锁相式频率合成器能给出长期和短期稳定度都比较高的输出频率信号,信道树木多,体积小。

利用分频技术可以产生小于或等于基准频率的各种参考频率信号,通用计数器可以作为分频器,若在前面加上高速前级脉冲计数器则整个电路作为高速分频器使用,分频系数N越大,分频后的噪声越小。

锁相环一般由环路滤波器,压控振荡器,数字分频器和鉴相器构成。

其主要参数包括:

鉴相器转换增益,压控振荡器(VCO转换增益,压控振荡器自由振荡频率和输出电压幅值

S

图8.10-1是一个锁相环简单测试电路,敲击A健使开关S分别为环路滤波器输入端(FI)选择10V和5V两档输入电压,用示波器的VA通道监视压控振荡器输出电压(VO),VB通道监视环路滤波器输出电压(FC)。

若在环路滤波器输入端施加连续变化的模拟电压,则压控振荡器将输出连续变频电压。

读者可自行设计相关测试电路。

第九章电子电路系统仿真

本章主要介绍小型电子电路系统的设计与仿真,用好EWB勺子电路功能,将使系统分析过程大大简化。

9.1多波形函数发生器

1.方波一三角波发生器

利用集成运算放大器构成的多波形函数发生器电路如图9.1-1所示,其中AR2组成迟滞

比较器,AR3组成积分器,通过正反馈环路使电路产生振荡,便可在AR2输出端(VO1产

生方波输出。

该方波经AR3积分后,在其输出端(V02)产生三角波输出。

在图9.1-1中给定参数条件下,用示波器测得V01(VA)和V02(VB)的电压波形。

敲击W键,调节可变电阻器R11,可改变积分器的充放电时间常数,从而改变三角波和方波电压周期。

2.锯齿波一窄脉冲发生器

若敲击K键,将开关S1闭合,则导引二极管D3和电阻R16并联,使积分器在两个方向上的积分时间常数产生较大差异,使三角波电压下降边时间大大缩短,从而将三角波变为锯

齿波,而方波则由于正负半周严重不对称,而成为窄脉冲。

读者可改变参数通过示波器自行

观测波形变化。

3.方波一正弦波发生器

在图9.1-1中,集成运放AR1组成带通滤波器,其功能是将输入方波电压经过带通滤波转换为特定频率的正弦波电压输出。

我们先单独对AR1组成带通滤波器进行交流频率分析,分析电路如图9.1-3所示,

C3

022uF

选择EW盼析菜

单中的交流频率分析项,在交流频率分析参数设置对话框中,设置扫描起始和终止频率为1HZ和1MHZ扫描形式为十进制,纵向尺度为线性,输出端为节点3。

电击仿真按钮后得到

频率响应曲线。

将带通滤波器输入端接至方波发生器输出端可变电阻R10的抽头处(见图9.1-1),将

示波器VA接方波发生器输出VO1,VB接正弦波输出端VO3闭合仿真电源开关,打开示波器面板,测得方波及方波经带通滤波后转换之正弦波。

敲击R键,调节可变电阻R10,可调节带通滤波器输入方波电压的幅值,进而调节正弦波电压的幅值。

9.2单电源互补对称功率放大器(OTL

一单电源互补对称功放电路如图9.2-1所示,

因为电源电压(V1)为15V,因此,静态时可调整R9或R6使Q1射极直流电位为7.5V(如

电压表M1所指示)。

电路的交流电压放大倍数:

可通过测量负载电阻(R7)两端的电压有效值换算得到。

9.3双电源互补对称功率放大器(OCL

电路的交流电压放大倍数:

体管Q13或Q14的饱和压降。

取大输出功率:

D1Vomax

lomax—瓦r’5

-。

同样,读者可通过测量负载电阻(R25)两端的电压有效值,换算出输出功率。

9.4数字钟

数字钟电路是一个典型的数字电路系统,其由时,分,秒计数器以及校时和显示电路组成下面介绍利用集成十进制递增计数器(74160)和带译码器的七段显示数码管组成的数字钟电路.计数器74160和七段显示数码管的功能及使用方法在8.4节已有叙述.

1.利用两片74160组成60进制递增计数器

利用两片74160组成的同步60进制递增计数器如图9.4-1所示,

其中个位计数器(C1)接成十进制形式。

十位计数器(C2)选择QC与QB做反馈端,经

与非门输出控制清零端(CLR',接成六进制计数形式。

个位与十位计数器之间采用同步级

连方式,将个位计数器的进位输出控制端(RCO)接至十位计数器容许端(ENT),完成个

位对十位计数器的进位控制。

将个位计数器的RCO端和十位计数器的QC、QA端经与们由

CO端输出,作进位输出控制信号。

当计数器状态为59时,CO端输出高电平,在同步级联

方式下,容许高位计数器计数。

选择信号源库中的1HZ方波信号作为计数器的测试时钟源。

因为秒与分计数均由60进制递增计数器来完成,为在构成数字钟系统时使电路得到简

化,我们将图9.4-1虚线框内建立部分用子电路表示。

具体操作过程如下:

在EWB主界面内建立图9.4-1所示60进制计数器,闭合仿真电源,经过功能测试,确

保计数器工作正常。

选中虚线框内所示部分电路(Circuit)菜单中的创建子电路(Creat

Subcircuit)项,主界面内出现子电路设置对话框,在对话框内添入电路名称(60C)后,选择在电路中置换(ReplaceinCircuit)项,得用子电路表示的60进制递增计数器如图9.4-3

2、用两片74160组成24/12进制递增计数器

GrtlD

图944所示电路是由两片74160组成的能实现12和24进制转换的同步递增计数器。

图中个位与十位计数器均接成十进制计数形式,采用同步级连方式。

选择十位计数器的输出端

QB和个位计数器的输出端QC通过与非门NAND2控制两片计数器的清零端(CLR',利用状态24反馈清零,可实现24进制递增计数。

若选择十位计数器的输出端QA与个位计数

器的输出端QB经过与非门NAND1输出,控制两片计数器的清零端(CLR',利用状态12反馈清零,可实现12进制递增计数。

敲击Q键,使开关K选择与非门NAND2输出或NAND1输出可实现24和12进制递增计数器的转换。

该计数器可利用作数字钟的时计数器。

为简化数字钟电路,我们将图9.4-4所示的24/12进制计数器虚线框内电路转换为子电路,

转换方法与上述60进制计数器相同。

用子电路表的24/12进制同步计数器如图9.4-5所示。

3.

数字钟系统的组成

在数字钟电路中,由两个计数器实现小时计数。

秒、分、时计数器之间采用同步级连方式。

开关K控制小时的24进制和12进制计数

方式选择。

为简化电路,直接选用信号源库中的方波秒脉冲作数字钟的秒脉冲信号,读者可

自行设计独立的秒脉冲源,例如;可利用555多谐振荡器产生的秒脉冲,或者采用石英晶体

振荡器经分频器产生秒脉冲。

还可以在小时显示的基础上,增加上、下午或日期显示以及整

点报时等,这里不再赘述。

敲击S和F键,可控制开关S和F将秒脉冲直接引入时、分计数器,实现校时。

.口.

冋

对于图9.4-6所示数字钟电路,若要进一步简化电路还可以利用子电路嵌套功能将虚

线框内电路转换为更高一级的子电路,我们将子电路命名为CLOCK,用高一级子电路表示

的数字钟电路如图9.4-7所示。

后在设计用到数字钟作单元电路的系统时可直接引用该电路,使系统得到简化。

9.5交通信号灯自动定时控制系统

交通信号灯自动定时控制系统用中小规模数字集成电路实现非常方便,而且便于在

EWB内进行仿真实验。

设系统工作的不十字路口由主、支两条道构成,四路口均设红、黄、绿三色信号灯和用于计时的两位由数码管显示的十进制计数器,其示意图由图9.5-1所示,

□匚I

主干遺

UU

ooo

红黃绿

支干這

□□r

UU

ooo

红黄缘

图95-1I-越口则信号系袪示意圉

系统设计与仿真过程如下。

1.系统功能要求

(1)主、支干道交替通行,通行时间均可在0~99秒内任意设定。

(2)每次绿灯换红灯前,黄灯先亮较短时间(也可在0~99秒内任意设定),用以等待十字路口内滞留车通过。

(3)主支干道通行时间和黄灯的时间均由同一计数器按减计数方式计数(零状态为无效态)

(4)在减计数器回零瞬间完成十字路口通行状态的转换(换灯)。

(5)计数器的状态由显示器件库中的带译码七段

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 电子电路 仿真

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《贝的故事》教案4.docx

《贝的故事》教案4.docx