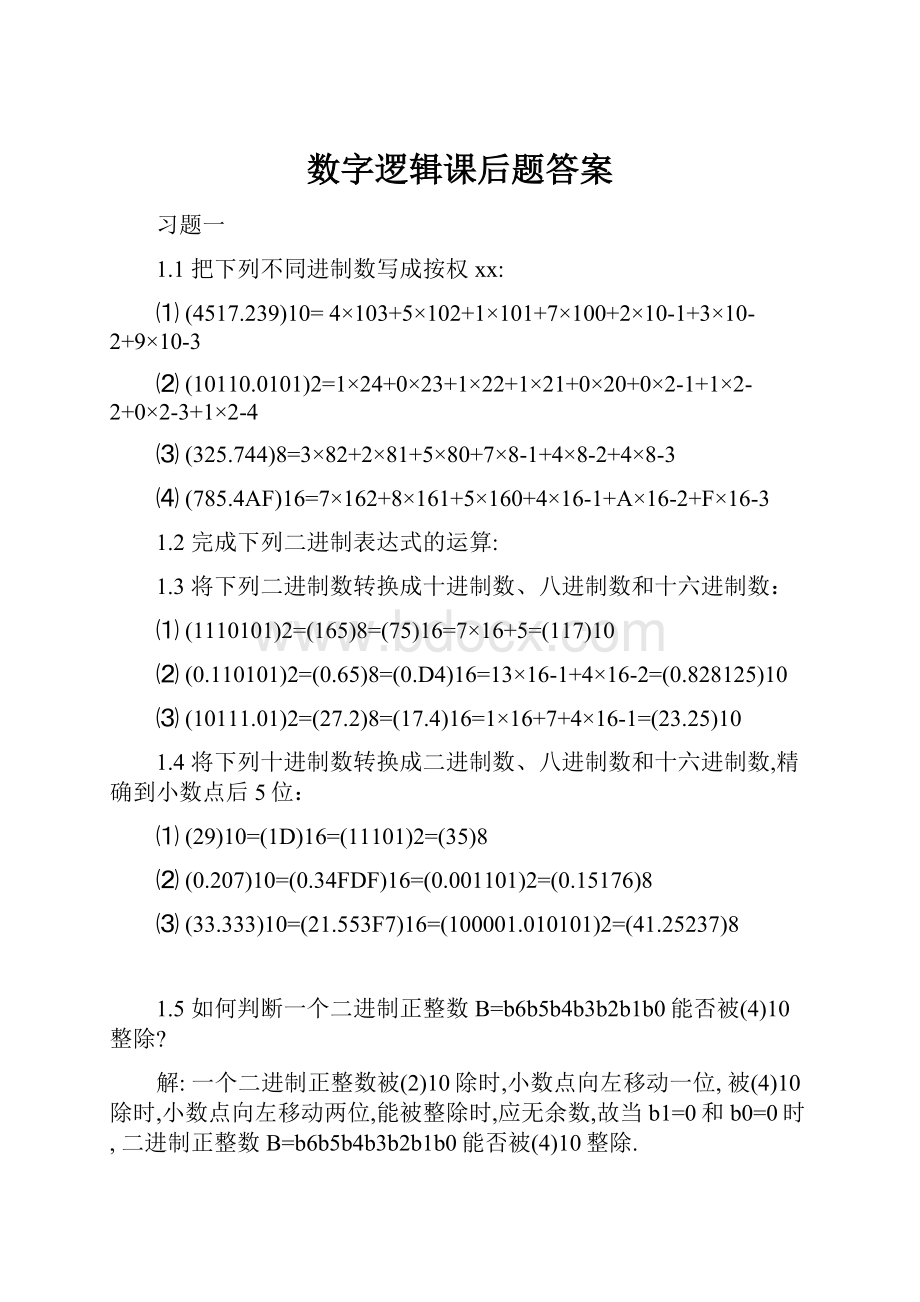

数字逻辑课后题答案.docx

数字逻辑课后题答案.docx

- 文档编号:30257819

- 上传时间:2023-08-13

- 格式:DOCX

- 页数:24

- 大小:203.55KB

数字逻辑课后题答案.docx

《数字逻辑课后题答案.docx》由会员分享,可在线阅读,更多相关《数字逻辑课后题答案.docx(24页珍藏版)》请在冰豆网上搜索。

数字逻辑课后题答案

习题一

1.1把下列不同进制数写成按权xx:

⑴(4517.239)10=4×103+5×102+1×101+7×100+2×10-1+3×10-2+9×10-3

⑵(10110.0101)2=1×24+0×23+1×22+1×21+0×20+0×2-1+1×2-2+0×2-3+1×2-4

⑶(325.744)8=3×82+2×81+5×80+7×8-1+4×8-2+4×8-3

⑷(785.4AF)16=7×162+8×161+5×160+4×16-1+A×16-2+F×16-3

1.2完成下列二进制表达式的运算:

1.3将下列二进制数转换成十进制数、八进制数和十六进制数:

⑴(1110101)2=(165)8=(75)16=7×16+5=(117)10

⑵(0.110101)2=(0.65)8=(0.D4)16=13×16-1+4×16-2=(0.828125)10

⑶(10111.01)2=(27.2)8=(17.4)16=1×16+7+4×16-1=(23.25)10

1.4将下列十进制数转换成二进制数、八进制数和十六进制数,精确到小数点后5位:

⑴(29)10=(1D)16=(11101)2=(35)8

⑵(0.207)10=(0.34FDF)16=(0.001101)2=(0.15176)8

⑶(33.333)10=(21.553F7)16=(100001.010101)2=(41.25237)8

1.5如何判断一个二进制正整数B=b6b5b4b3b2b1b0能否被(4)10整除?

解:

一个二进制正整数被

(2)10除时,小数点向左移动一位,被(4)10除时,小数点向左移动两位,能被整除时,应无余数,故当b1=0和b0=0时,二进制正整数B=b6b5b4b3b2b1b0能否被(4)10整除.

1.6写出下列各数的原码、反码和补码:

⑴0.1011

[0.1011]原=0.1011;[0.1011]反=0.1011;[0.1011]补=0.1011

⑵0.0000

[0.000]原=0.0000;[0.0000]反=0.0000;[0.0000]补=0.0000

⑶-10110

[-10110]原=110110;[-10110]反=101001;[-10110]补=101010

1.7已知[N]补=1.0110,求[N]原,[N]反和N.

解:

由[N]补=1.0110得:

[N]反=[N]补-1=1.0101,[N]原=1.1010,N=-0.1010

1.8用原码、反码和补码完成如下运算:

⑴0000101-0011010

[0000101-0011010]原=10010101;

∴0000101-0011010=-0010101。

[0000101-0011010]反=[0000101]反+[-0011010]反=00000101+11100101=11101010

∴0000101-0011010=-0010101

[0000101-0011010]补=[0000101]补+[-0011010]补=00000101+11100110=11101011

∴0000101-0011010=-0010101

⑵0.010110-0.100110

[0.010110-0.100110]原=1.010000;

∴0.010110-0.100110=-0.010000。

[0.010110-0.100110]反=[0.010110]反+[-0.100110]反=0.010110+1.011001=1.101111

∴0.010110-0.100110=-0.010000;

[0.010110-0.100110]补=[0.010110]补+[-0.100110]补=0.010110+1.011010=1.110000

∴0.010110-0.100110=-0.010000

1.9分别用“对9的补数”和“对10的补数”完成下列十进制数的运算:

⑴ 2550-123

[2550-123]9补=[2550]9补+[-123]9补=02550+99876=02427

∴2550-123=2427

[2550-123]10补=[2550]10补+[-123]10补=02550+99877=02427

∴2550-123=2427

⑵537-846

[537-846]9补=[537]9补+[-846]9补=0537+9153=9690

∴537-846=-309

[537-846]10补=[537]10补+[-846]10补=0537+9154=9691

∴537-846=-309

1.10将下列8421BCD码转换成二进制数和十进制数:

⑴(0110,1000,0011)8421BCD=(1010101011)2=(683)10

⑵(0100,0101.1001)8421BCD=(101101.11100110)2=(45.9)10

1.11试用8421BCD码、余3码、和xx码分别表示下列各数:

⑴(578)10=(0101,0111,1000)8421BCD=(1000,1010,1011)余3码=(1001000010)2=(1101100011)Gray

⑵(1100110)2=(1010101)Gray=(102)10=(0001,0000,0010)8421BCD=(0100,0011,0101)余3码

习题二

2.1分别指出变量(A,B,C,D)在何种取值组合时,下列函数值为1。

如下真值表中共有6种

如下真值表中共有8种

如下真值表中除0011、1011、1111外共有13种:

2.2用逻辑代数公理、定理和规则证明下列表达式:

⑴

证明:

左边==右边

∴原等式成立.

⑵

证明:

左边==右边

∴原等式成立.

⑶

证明:

左边=

==右边

∴原等式成立.

⑷

证明:

右边==左边

∴原等式成立.

⑸

证明:

左边==右边

∴原等式成立.

2.3用真值表检验下列表达式:

⑴

⑵

2.4求下列函数的反函数和对偶函数:

⑴

⑵

⑶

2.5回答下列问题:

⑴已知X+Y=X+Z,那么,Y=Z。

正确吗?

为什么?

答:

正确。

因为X+Y=X+Z,故有对偶等式XY=XZ。

所以

Y=Y+XY=Y+XZ=(X+Y)(Y+Z)=(X+Y)(Y+Z)

Z=Z+XZ=Z+XY=(X+Z)(Y+Z)=(X+Y)(Y+Z)

故Y=Z。

⑵已知XY=XZ,那么,Y=Z。

正确吗?

为什么?

答:

正确。

因为XY=XZ的对偶等式是X+Y=X+Z,又因为

Y=Y+XY=Y+XZ=(X+Y)(Y+Z)=(X+Y)(Y+Z)

Z=Z+XZ=Z+XY=(X+Z)(Y+Z)=(X+Y)(Y+Z)

故Y=Z。

⑶已知X+Y=X+Z,且XY=XZ,那么,Y=Z。

正确吗?

为什么?

答:

正确。

因为X+Y=X+Z,且XY=XZ,所以

Y=Y+XY=Y+XZ=(X+Y)(Y+Z)=(X+Z)(Y+Z)=Z+XY=Z+XZ=Z

⑷已知X+Y=XZ,那么,Y=Z。

正确吗?

为什么?

答:

正确。

因为X+Y=XZ,所以有相等的对偶式XY=X+Z。

Y=Y+XY=Y+(X+Z)=X+Y+Z

Z=Z+XZ=Z+(X+Y)=X+Y+Z

故Y=Z。

2.6用代数化简法化简下列函数:

⑴

⑵

⑶

2.7将下列函数表示成“最小xx和”形式和“最大xx积”形式:

⑴=∑m(0,4,5,6,7)=∏M(1,2,3)(如下xx1)

⑵=∑m(4,5,6,7,12,13,14,15)

=∏M(0,1,2,3,8,9,10,11)(如下xx2)

⑶=∑m(0,1,2,3,4)

=∏M(5,6,7,8,9,10,11,12,13,14,15)(如下xx3)

2.8用xx化简下列函数,并写出最简“与-或”表达式和最简“或-与”表达式:

⑴=

⑵=或=

=

⑶==

2.9用xx判断函数和有何关系。

=

=

可见,

2.10xx如下图所示,回答下面两个问题:

⑴若,当取何值时能得到取简的“与-或”表达式。

从以上两个xx可以看出,当=1时,能得到取简的“与-或”表达式。

⑵和各取何值时能得到取简的“与-或”表达式。

从以上两个xx可以看出,当=1和=1时,

能得到取简的“与-或”表达式。

2.11用xx化简包含无关取小项的函数和多输出函数。

⑴∑m(0,2,7,13,15)+∑d(1,3,4,5,6,8,10)

∴

⑵

∴

习题三

3.1将下列函数简化,并用“与非”门和“或非”门画出逻辑电路。

⑴∑m(0,2,3,7)==

⑵∏M(3,6)=∑m(0,1,2,4,5,7)==

=

⑶==

=

⑷==

=

3.2将下列函数简化,并用“与或非”门画出逻辑电路。

⑴=

⑵∑m(1,2,6,7,8,9,10,13,14,15)=

3.3分析下图3.48所示逻辑电路图,并求出简化逻辑电路。

解:

如上图所示,在各个门的输出端标上输出函数符号。

则

=A(B⊙C)+C(A⊙B)

真值表和简化逻辑电路图如下,逻辑功能为:

依照输入变量ABC的顺序,若A或C为1,其余两个信号相同,则电路输出为1,否则输出为0。

3.4当输入变量取何值时,图3.49中各逻辑电路图等效。

解:

∵

∴当和的取值相同(即都取0或1)时,这三个逻辑电路图等效。

3.5假定代表一个两位二进制正整数,用“与非”门设计满足如下要求的逻辑电路:

⑴;(Y也用二进制数表示)

因为一个两位二进制正整数的平方的二进制数最多有四位,故输入端用A、B两个变量,输出端用Y3、Y2、Y1、Y0四个变量。

⑴真值表:

⑵真值表:

∴Y3=AB,Y2=,Y1=0,Y0=+AB=B,逻辑电路为:

⑵,(Y也用二进制数表示)

因为一个两位二进制正整数的立方的二进制数最多有五位,故输入端用A、B两个变量,输出端用Y4、Y3、Y2、Y1、Y0五个变量。

可列出真值表⑵

∴Y4=AB,Y3=,Y2=0,Y1=AB,Y0=+AB=B,逻辑电路如上图。

3.6设计一个一位十进制数(8421BCD码)乘以5的组合逻辑电路,电路的输出为十进制数(8421BCD码)。

实现该逻辑功能的逻辑电路图是否不需要任何逻辑门?

解:

因为一个一位十进制数(8421BCD码)乘以5所得的的十进制数(8421BCD码)最多有八位,故输入端用A、B、C、D四个变量,输出端用Y7、Y6、Y5、Y4、Y3、Y2、Y1、Y0八个变量。

真值表:

用xx化简:

Y7=0,Y6=A,Y5=B,Y4=C,Y3=0,Y2=D,Y1=0,Y0=D。

逻辑电路如下图所示,在化简时由于利用了无关项,本逻辑电路不需要任何逻辑门。

3.7设计一个能接收两位二进制Y=y1y0,X=x1x0,并有输出Z=z1z2的逻辑电路,当Y=X时,Z=11,当Y>X时,Z=10,当Y 用“与非”门实现该逻辑电路。 解: 根据题目要求的功能,可列出真值表如下: 用xx化简: z1=+ z2=+ ∴转化为“与非与非”式为: 逻辑电路为: 3.8设计一个检测电路,检测四位二进制码xx1的个数是否为奇数,若为偶数个1,则输出为1,否则为0。 解: 用A、B、C、D代表输入的四个二进制码,F为输出变量,依题意可得真值表: xx不能化简: 用“与非”门实现的逻辑电路为: 用异或门实现的电路为 3.9判断下列函数是否存在冒险,并消除可能出现的冒险。 ⑴ ⑵ ⑶ 解: ⑴不存在冒险; ⑵存在冒险,消除冒险的办法是添加一冗余项BD; 即: ⑶也存在冒险,消除冒险的办法也是添加一冗余因子项. 即: . 习题四 4.1图4.55所示为一个同步时序逻辑电路,试写出该电路的激励函数和输出函数表达式。 解: 输出函数: ; ;; 激励函数: ; ; ; 。 4.2已知状态表如表4.45所示,作出相应的状态图。 解: 状态图为: 4.3已知状态图如图4.56所示,作出相应的状态表。 解: 相应的状态表为: 4.4图4.57所示状态图表示一个同步时序逻辑电路处于其中某一个未知状态,。 为了确定这个初始状态,可加入一个输入序列,并观察输出序列。 如果输入序列和相应的输出序列为00/0、01/1、00/0、10/0、11/1,试确定该同步时序电路的初始状态。 解: 为分析问题的方便,下面写出状态表: 当输入序列和相应的输出序列为00/0时,A、B、C、D都符合条件,但当序列为01/1时要转为B态或C态,就排除了A、D态;下一个序列为00/0时,B、C保持原态,接着序列为10/0时,B态转为A态,C态转为D态,但当最后一个序列为11/1时,只有D态才有可能输出1,这就排除了B态。 故确定该同步时序电路的初始状态为C态。 即C(初态)→(00/0)→C→(01/1)→C→(00/0)→C→(10/0)→D→(11/1)→C 4.5分析图4.58所示同步电路,作出状态图和状态表,并说明该电路的逻辑功能。 解: 激励方程: ;;;; 输出方程: 。 ∴各触发器的状态方程为: ==; ==0; 由图可见,该电路的逻辑功能为: 在时钟脉冲作用下,输入任意序列x均使电路返回00状态。 4.6图4.59为一个串行xx逻辑框图,试作出其状态图和状态表。 解: 状态图和状态表为: 4.7作1010序列检测器的状态图,已知输入、输出序列为输入: 001010010101010110输出: 000001000010101000 解: 1010序列检测器的状态图如右。 4.8设计一个代码检测器,电路串行输入余3码,当输入非法数字时电路输出为0,否则输出为1,试作出状态图。 解: 余3码的非法数字有六个,即0000,0001,0010,1101,1110,1111。 故其原始状态图为: 4.9简化表4.46所示的完全确定状态表。 解: 表4.46所示的完全确定状态表的隐含表为: 考察给定的状态表,比较状态C和F。 不论输入x是1还是0,它们所产生的输出都相同。 当x=0时,所建立的次态也相同;但当x=1时,它们的次态不相同: N(C,1)=A N(F,1)=D 于是状态C,F能否合并,取决于状态A,D能否合并。 对于状态A和D。 不论输入x是1还是0,它们所产生的输出都分别相同。 当x=1时,它们的次态为现态的交错,但当x=0时,它们的次态却不相同: N(A,0)=EN(D,0)=B 因此,状态A,D能否合并,取决于状态B,E能否合并。 对于状态B和E。 不论输入x是1还是0,它们所产生的输出都分别相同。 但当x=0时,它们的次态不同: N(B,0)=AN(E,0)=D 当x=1时,它们所建立的次态也不相同: N(B,1)=FN(E,1)=C 可以发现: 状态CF、AD和BE能否各自合并,出现如上循环关系: 显然,由于这个循环中的各对状态,在不同的现输入下所产生的输出是分别相同的,因而从循环中的某一状态时出发,都能保证所有的输入序列下所产生的输出序列都相同。 所以,循环中各对状态分别可以合并。 令 A={A,D},B={B,E}C={C,F} 代入原始状态表中简化后,再令D、E代替G、H,可得最小化状态表。 4.10简化表4.47所示的不完全确定状态表。 解: 由给定的不完全确定状态表画出隐含表,可以得出全部相容状态对有五个,为: (A,B)、(C,D)、(C,E)、(A,D)、(B,C), 从这五个相容状态对可以看出它们本身就是最大相容类。 作出闭覆盖表寻找最小闭覆盖。 从闭覆盖表可以得出两种最小化方案及对应的最小化状态表: 从这两个方案可以看出,方案一相容类数目最少,是最佳方案。 4.11按照状态分配基本原则,将表4.48所示的状态表转换成二进制状态表。 解: 给定的状态表中共有A、B、C、D四个状态,其中B态和C态是可以合并的最大相容类,可看成一个状态,如B态。 则根据状态分配原则1),A和B应分配相邻代码;根据状态分配原则2),A和B,B和D应分配相邻代码;根据状态分配原则3),A和B、B和D应分配相邻代码,根据状态分配原则4),状态B的代码应分配为00。 从分配二进制代码的xx得代码分配结果: B为00;A为01;D为10。 C为11是不会出现的状态,可作无关项处理。 于是可得二进制状态表。 4.12若分别用J-K、T和D触发器作同步时序电路的存储电路,试根据表4.49所示的二进制状态表设计同步时序电路,并进行比较。 解: 下面画出了分别用J-K、T和D触发器作同步时序电路的存储电路时的激励函数和输出函数xx: ∴各触发器的激励函数和输出函数的表达式如下: ;;;; ;; ; == 各逻辑电路为: 由此可见,使用JK触发器线路较为简单,门电路较少,成本较低。 4.13设计一个能对两个二进制数X=x1,x2,┅,xn和Y=y1,y2,┅,yn进行比较的同步时序电路,其中,X,Y串行地输入到电路的x,y输入端。 比较从x1,y1开始,依次进行到xn,yn。 电路有两个输出Zx和Zy,若比较结果X>Y,则Zx为1,Zy为0;若X<Y,则Zy为1,Zx为0;若X=Y,则Zx和Zy都为1。 要求用尽可能少的状态数作出状态图和状态表,并作尽可能的逻辑门和触发器来实现。 解: 两个数进行比较时,先比较高位,然后比较低位。 若xi=yi=0或1,两个输出Zx和Zy=1,还应比较低一位,若还相等,则两个输出不变。 ,若所有的位的数都相等,最后输出Zx和Zy=1,表示比较结果X=Y。 比较过程中若出现某一位数不等,则比较结束。 xi>yi时输出Zx=1,Zy=0,比较结果X>Y;xi<yi时输出Zx=0,Zy=1,比较结果X<Y。 因题意要求要求用尽可能少的状态数作出状态图和状态表,并作尽可能的逻辑门和触发器来实现,故采用Moore型电路,用两个D触发器,这两个触发器的输出就是电路的输出,其中y2表示Zy,y1表示Zx。 用A、B、C三个状态分别表示X=Y、X<Y、X>Y。 令A=11,B=01,C=10,得二进制状态表。 .采用D触发器,经xx化简得激励方程: ; 所设计的同步时序逻辑电路为: 习题四5 5-1: (1)列出电路的激励函数和输出函数表达式: (2)作状态真值表: 输入 现态 激励函数 次态 CP Q1Q2Q3 J1K1CP1 J2K2CP2 J3K3CP3 Q1(n+1)Q2(n+1Q3(n+1)) 1 000 111 110 010 100 1 001 111 010 010 101 1 010 111 110 110 110 1 011 111 010 010 111 1 100 111 011 011 010 1 101 111 022 011 000 1 110 111 111 111 001 1 111 111 011 011 000 (3)作状态图表如下: (4)功能描述: 由状态图可知,此电路为一带自启动能力的六进制计数器。 习题六 6.1用两个四位二进制并行xx实现两位十进制数8421BCD码到余3码的转换.。 6.2用两块四位数值比较器蕊片实现两个七位二进制数的比较.。 6.3用三输入八输出译码器和必要的逻辑门实现下列逻辑函数表达式: ; 解: = =; =yz+y+z++xyz+xy = =xy+xyz++z = 逻辑电路如上: 6.4用四路选择器设计下列组合逻辑电路: ⑴全加器; ⑵三变量多数表决电路。 6.5用四位二进制同步可逆计数器和必要的逻辑门构成模12加法计数器。 6.6用两块双向移位寄存器蕊片实现模8计数器。 6.7用ROM设计一个三位二进制平方器。 6.8用PLA实现四位二进制并行xx。 解: 根据P195图6.2四位并行xx逻辑电路,可得各输出函表达式: +++, A1B1+A1C0+B1C0,; 设1P1=;1P2=;1P3=;1P4=;1P5=A1B1; 1P6=A1C0;1P7=B1C0;1P8=;1P9=;1P10=; =+++, A2B2+A2C1+B2C1;; 设2P1=;2P2=;2P3=;2P4=;2P5=A2B2; 2P6=A2C1;2P7=B2C1;2P8=;2P9=;2P10=; =+++, A3B3+A3C2+B3C2;; 设3P1=;3P2=;3P3=;3P4=;3P5=A3B3; 3P6=A3C2;3P7=B3C2;3P8=;3P9=;3P10=; =+++,A4B4+A4C3+B4C3; 设4P1=;4P2=;4P3=;4P4=; 4P5=A4B4;4P6=A4C3;4P7=B4C3; 6.9用PLA实现图6.33所示的时序逻辑电路。 解: D触发器激励函数表达式为: ; 输出函数表达式为: Z= 设P1=;P2=;P3=,则根据激励函数和输出函数表达式,可画出用PLA实现的时序逻辑电路。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 逻辑 课后 答案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx