ic610安装及版图后仿.docx

ic610安装及版图后仿.docx

- 文档编号:30211469

- 上传时间:2023-08-07

- 格式:DOCX

- 页数:23

- 大小:2.45MB

ic610安装及版图后仿.docx

《ic610安装及版图后仿.docx》由会员分享,可在线阅读,更多相关《ic610安装及版图后仿.docx(23页珍藏版)》请在冰豆网上搜索。

ic610安装及版图后仿

(1)首先将安装包解压缩出来。

~/soft/IC610_lnx86.Base/

(注明,~表示你的home目录)

(2)终端中,进入CDROM1,输入./SETUP.SH(也可以直接双击)

(3)提示输入我们所要安装的目录。

我们输入~/ic610

(4)问我们是否安装过installscape,选择n

(5)然后问是否需要installscape,选择y

(6)选择installscape安装目录,输入~/installscape

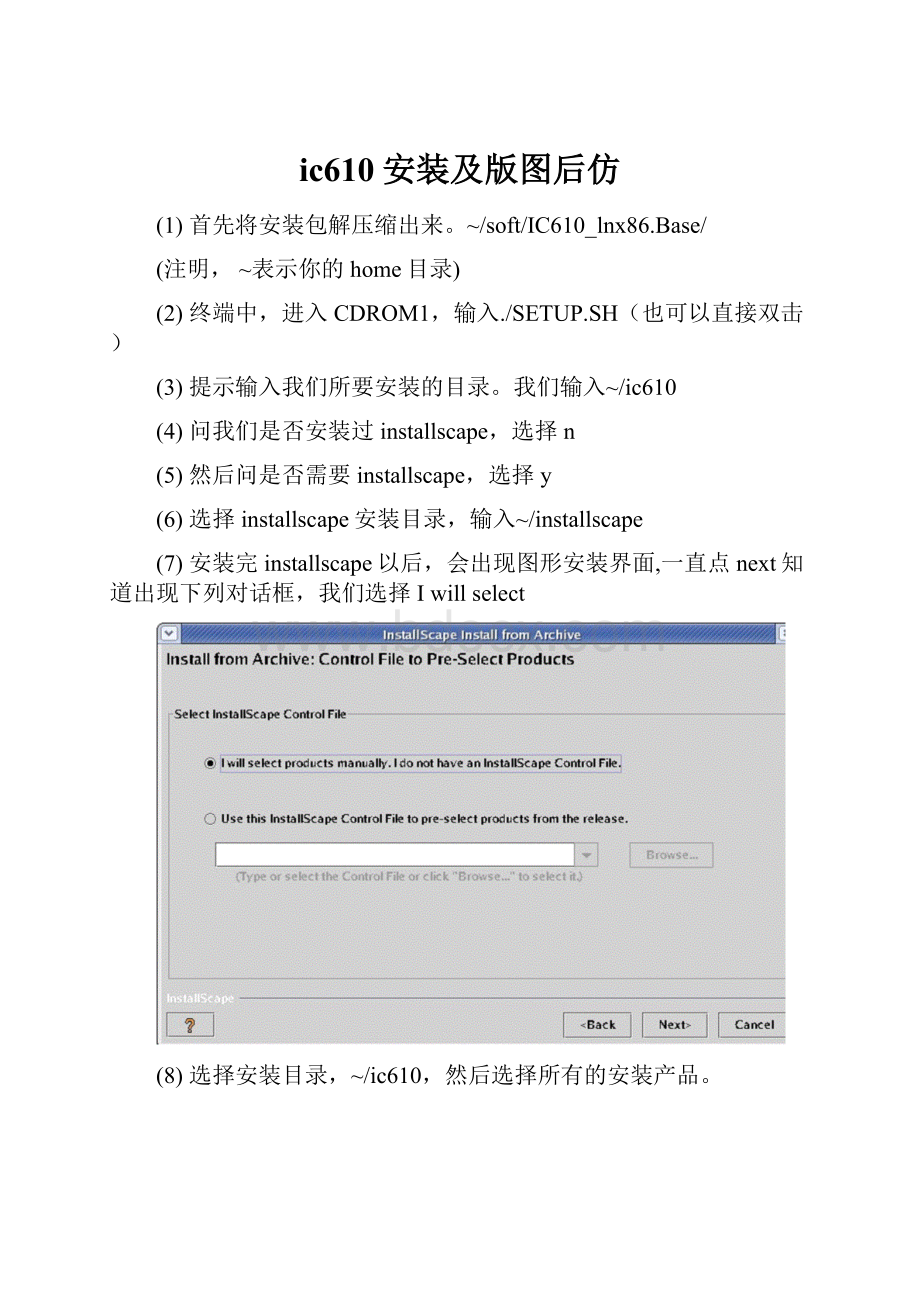

(7)安装完installscape以后,会出现图形安装界面,一直点next知道出现下列对话框,我们选择Iwillselect

(8)选择安装目录,~/ic610,然后选择所有的安装产品。

(9)中间会出现一些选择,按提示即可

2.安装后配置

(1)终端进入~/installscape/iscape/bin。

(2)输入./iscape.sh再次进入安装界面。

(3)选择configure。

(4)选择需要配置的目录,即ic610的安装路径。

(5)全部选择

(6)然后next,期间会有很多选择

选择一:

PreparelibrariesforAMSdesign

1)AddanIUSinstallationdirectorytopath

2)Quit

选择二:

Proceedingwithconfigurationoflfvhdcomp

synergyusersmustinstallthislibraries:

installValidandsimprimitives?

(

y

installXLlibrariesandgateprimitives(

y

选择三:

enterthetopinsrallationdirectory

[/home/cadence/ic610]->直接回车

选择四:

editthelicensefileorthestartupscriptnow?

选择五:

configuretheclientsfile

选择六:

editlocalhost.localdomain’sbootscript?

选择完以上内容,会出现配置OA的选项,这一步很重要,因为ic610需要OA库的支持。

然后输入OA的安装目录:

选择好后,回车,OA就会安装到/home/cadence/ic610/OA目录下。

(7)讲license.txt放入/home/cadence/ic610/share/license目录下,启用license的时候如果端口被占用,可以修改端口名,比如7777改成7778。

(8)环境变量配置,在.cshrc文件中,加入以下变量:

aliaslmli"/home/cadence/ic610/tools/bin/lmgrd-c/home/cadence/ic610/share/license/license.txt"

setenvOA_HOME/home/cadence/ic610/OA

setenvCDS_ROOT/home/cadence/ic610

setenvCDS_HOME/home/cadence/ic610

setenvMMSIM_ROOT/home/cadence/mmsim61

setenvCDS_LIC_FILE7779@localhost

setenvLM_LICENSE_FILE$CDS_ROOT/share/license/license.txt

setenvCDS_Netlisting_ModeAnalog

setenvPATH"$MMSIM_ROOT/tools/bin:

$MMSIM_ROOT/tools/spectre/bin:

$CDS_ROOT/tools/bin:

$CDS_ROOT/tools/dfII/bin:

$PATH"

setenvPATH"/home/cadence/hspice200509/hspice/linux:

$PATH"

setenvAVANTD_LICENSE_FILE/home/cadence/hspice200509/hspice/hspice.dat

setenvMOZILLA_HOME/usr/bin/netscape

(9)启动license:

终端中运行lmli,即可启动license,或者设置开机启动

在/etc/rc.d目录中,用vi命令打开rc.local文件(打开前使用超级用户,终端中su),然后按i,即可编辑rc.local文件,在里面加入/home/cadence/ic610/tools/bin/lmgrd-c/home/cadence/ic610/share/license/license.txt,保存。

以后每次开机都会加载此license。

(10)启动ic610。

终端中icfb&,即进入ic610

3.库的添加

(1)新建一个文件夹,比如ic_lib,将NCSU-FreePDK45-1.3.tar.gz解压到ic_lib下,解压后出现FreePDK45文件夹,里面含有ncsu_basekit,osu_soc两个单元库。

(2)在.cshrc中加入库的路径变量如下:

setenvPDK_DIR/home/cadence/ic_lib/FreePDK45

(3)新建一个工作目录,如design.并将/home/cadence/ic_lib/FreePDK45/ncsu_basekit/cdssetup下所有的文件拷到design下。

并把cdsinit和cdsenv文件改名为.cdsinit和.cdsenv(即前面加点)这样就可以在画版图的时候使用快捷键。

(4)在design的cds.lib中加入必要的库:

如下所示

DEFINEsample/home/cadence/ic610/tools/dfII/samples/cdslib/sample

INCLUDE/home/cadence/ic610/share/cdssetup/cds.lib

4.电路图绘制和前仿

(1)启动ic610,在CIW窗口中进行file->New->Library即进入建库目录,我们这里以一个反相器为例,库名输入INV。

(2)选择attachtoanexistingtechnologlibrary,下一个窗口,选择:

"NCSU_TechLib_FreePDK45".

(2)建好后,在库列表中会多出一个INV库,这就是我们要进行设计的地方。

(3)新建单元File->New->CellView,cell中填入INV,即我们要画的反相器电路。

(5)反相器电路绘制。

在NCSU_Devices_FreePDK45的库中选择PMOS_VTL和NMOS_VTL,在analoglib库中选择其他单元,具体选择如下表所示:

1.加入PMOS(NCSU_Devices_FreePDK45库),宽为180n,长为50n。

2.加入NMOS(NCSU_Devices_FreePDK45),宽为90n,长为50n。

3.然后在模拟库中添加其他常用单元(analoglib)

在analoglib中选择vdc单元,在dcvoltage中填入1.1。

然后放置到电路图编辑界面。

接下来再选择analoglib库,选择vpulse模型,需输入的值如下:

最后加入PIN,和cap。

Cap的值设为1fF.

(6)最后的电路图如下:

(7)对以上电路图进行前仿真

1.菜单栏中选择Launch->ADEL.得到仿真界面.

2.仿真界面中,Setup->Simulator/Directory/Host,选择hspiceD

3.选择仿真模型,Setup->modlelibraries,选择$PDK_DIR/ncsu_basekit/models/hspice/hspice_nom.include这个模型

4.选择仿真时间analysis->choose

(5)选择输出信号outputs->tobeplotted->selectonschematic。

我们在电路图中选好输入和输出(点线为输出电压,点节点为输出电流)

(7)运行仿真。

5.45nm版图的绘制及版图后仿

(1)先绘制好反相器的电路图:

(2)创建版图视窗。

File->New->CellView.Type选择“layout”单元名为“INV”。

按OK即进入版图编辑界面。

(3)绘图前设置,options->display显示层次设置从0到32,比如20,其他默认即可。

(4)PMOS的绘制

PMOS的绘制需要用到的layers为:

pwell,active,nimplant,poly,metal1,via。

1.先画poly,宽为50nm,选取lsw中的poly,然后用快捷键r,绘制一个长为300nm,宽为50nm的poly,因为此实验主要是为了后仿,所以长度可以长些,但是宽度必须为50nm,这是工艺尺寸,此刻要用到尺子,快捷键为k。

2.画nwell和active,如图所示,在poly外围画nwell,然后在内部画一个宽度为180nm的active,并在同样的位置同样的大小将nimplant画进去。

进行drc检查,无错,有错的话,根据错误内容及时更正。

运行DRC,calibre->runDRC,运行结果发现有错,错误提示poly超出active的最小距离为0.05,说明poly画短了,拉长后(长于0.05),发现错误被排除了。

3.同样的方法画NMOS,画完以后运行DRC。

DRC检查显示nwell到pwell的最小距离应该为225nm

我们把nwell的距离和pwell的距离设置为0.23,再运行DRC,发现错误被排除

4.添加via,即p有源区和金属连接点,在菜单栏中选择,create->via,在选择界面中,选择M1_P,然后放置到pactive的两边。

选择M1_N放到nactive的两边。

5.连接poly,PMOS和NOMS

6.添加NTAP和PTAP。

create->via,选择NTAP和PTAP,并和有源区连接起来。

7.添加PIN.先选择一个M1_PLOY,作为输入IN和栅极的连接,连接好后,选择create->pin,或者快捷键ctrl+p,出现PIN的编辑界面,终端名字写IN,然后选择displaypinname,再选择displaypinnameoption,弹出另外一个对话框,在height中,我们填写0.05,再textoption中,选择metal1(注意添加之前,要在lsw中选择metal1),同样的方法添加OUT。

8.添加label后,drc通过后的电路图

6.使用calibre对版图抽取,并输出网表,然后hspice后仿

(1)lvs,在版图界面中,calibre->RunLVS,出现lvs设置界面,我们将进行一下设置:

rules:

calibre的lvs规则文件,文件所在位置为$PDK_DIR/ncsu_basekit/techfile/calibre/calibreLVS.rul

input:

其他默认,主要在netlist的format选项中,选择exportformschematicviewer

(2)运行后lvs出错,报告文件为如下,说明有电路断开了,仔细看版图,发现ptap的well和和nmos的well未连接,我们把他连接以后,再运行lvs,可以看到lvs通过了。

(3)寄生参数抽取。

calibre->RunPEX

打开pex界面以后,我们要进行如下设置:

1.Rules:

$PDK_DIR/ncsu_basekit/techfile/calibre/calibrexRC.rul

2.Inputs:

其他默认,只要在netlist选择中,format类型为spice,最重要的是要选中

“exportfromschematicviewer“

3.Outputs:

抽取类型为晶体管级,即transisitor

在netlist中,format选择HSPICE

在reports中,勾选“generatePEXreport”和“viewreportafterPEXfinishes”

4.点击runPEX抽取的网表如下:

同时产生的还有INVlist.pex和INVlist.INV.pxi两个文件。

里面包含了电路抽取出来的所有电容和电阻,我们可以看到,即使这非常简单的电路,也会导致众多的电阻和电容,这些参数可以使电路仿真达到最高的精确度。

之后我们可以将此3个文件,利用hspice进行后仿真

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- ic610 安装 版图

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx