数字电路部分一组合逻辑电路王翰卓.docx

数字电路部分一组合逻辑电路王翰卓.docx

- 文档编号:29999102

- 上传时间:2023-08-04

- 格式:DOCX

- 页数:15

- 大小:228.19KB

数字电路部分一组合逻辑电路王翰卓.docx

《数字电路部分一组合逻辑电路王翰卓.docx》由会员分享,可在线阅读,更多相关《数字电路部分一组合逻辑电路王翰卓.docx(15页珍藏版)》请在冰豆网上搜索。

数字电路部分一组合逻辑电路王翰卓

第二部分数字电路

第六章组合逻辑电路

6.1逻辑门电路

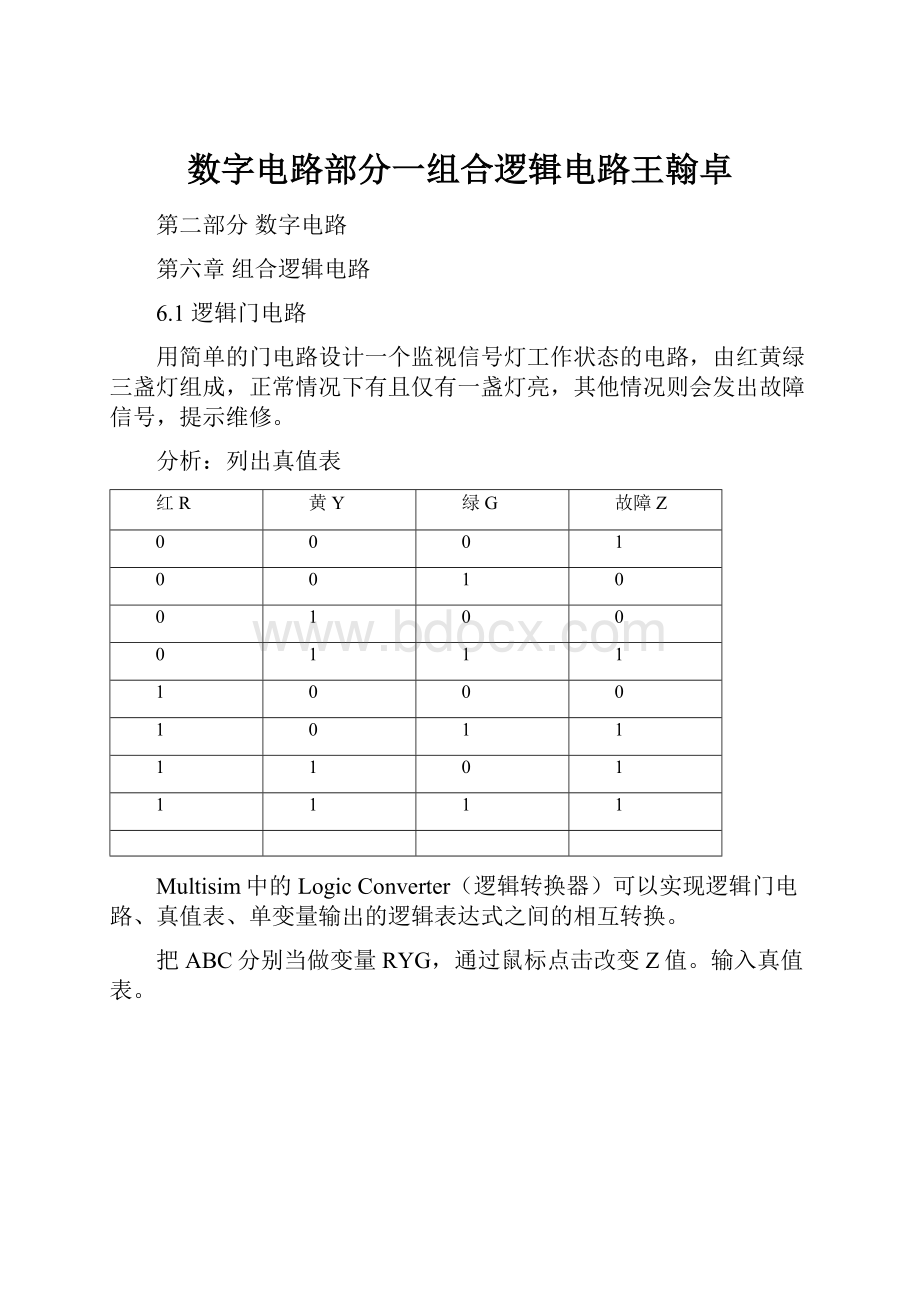

用简单的门电路设计一个监视信号灯工作状态的电路,由红黄绿三盏灯组成,正常情况下有且仅有一盏灯亮,其他情况则会发出故障信号,提示维修。

分析:

列出真值表

红R

黄Y

绿G

故障Z

0

0

0

1

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

Multisim中的LogicConverter(逻辑转换器)可以实现逻辑门电路、真值表、单变量输出的逻辑表达式之间的相互转换。

把ABC分别当做变量RYG,通过鼠标点击改变Z值。

输入真值表。

点击右侧的Conversions,得到函数表达式和最简表达式,最终转化出逻辑电路-

6.2编码器

6.2.1利用74HC148设计16-4线优先编码器

分析:

根据芯片的特点,s’=0时电路正常工作,此时如无编码请求Ys’=0,有编码请求YEx’=0。

由两片芯片来完成设计,s’=0的芯片编码优先级别高于另一芯片,为I8’-I15’,另一片为I0’-I7’。

每片芯片内部由I7’到I0’优先级逐渐降低。

第一片的Ys’与第二片的s’连接,编码结果以二进制形式输出,因为芯片不工作时输出端Ai输出为1,故两片对应的输出端以与非门连接进行输出作为低三位,第四位由Yex表示。

为了解Multisim的芯片端口标号,在芯片属性窗口单击Info(信息),查看端口功能-

电路连接图如图-

电路使用WordGenerater(数字信号发生器)作为输入信号,R端子为输出信号准备好标志信号,T端子为外触发信号输入端。

通过调节Display改变右端32位输出信号的格式,编辑右端视窗改变输出信号,通过右键设置起点(SetCursor)和终点(SetFinalPosition)。

在Control区选择输出方式,Cycle(循环)、Burst(始于起,止于终)、Step(点击后输出)。

如图设置由I0’到I15’依次编码。

观察到逻辑指示灯的闪烁。

6.2.2设计32-5线优先编码器

应用四片74HC148组装电路,基本方法如同16-4线优先编码器。

电路图如下,最右侧为最高位芯片,Gs1-Gs4四个变量在同一时刻只有一个为1,低三位的处理办法同上例,高二位由Gs1-Gs4四个变量产生。

真值表如下:

Gs1

Gs2

Gs3

Gs4

D5第五位

D4第四位

1

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

1

0

0

0

0

1

1

1

D5=(G3’G4’)’D4=(G2’G4’)’用两个与非门实现。

下图的仿真验证,26和17同时申请编码,根据优先编码的级别,对26编码,结果-11010。

6.3译码器

6.3.15-32线译码器

用3-8线译码器74LS138构建5-32线译码器。

分析:

需要4片74LS138来构建5-32线译码器,先将每一片的G1’和G2’置零,CBA用来作为输入需要译码的二进制数字的低三位,高二位则通过控制每一片的G1来达到设计要求。

同样在每一次译码只能有一片芯片可以工作。

译码数字的D4D5与每片的G1对应的真值表为-

D5

D4

G11

G21

G31

G41

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

1

1

0

0

0

1

G11=D5’D4’G21=D5’D4G31=D5D4’G41=D5D4

6.3.2最小项译码器的应用

用4-16线译码器74HC154设计一个能进行一位二进制数全加和全减运算的组合逻辑电路,当M=0时进行A+B,M=1时进行A-B。

S为本位的值,CI为来自下一级的进位或借位,CO为向上一级的进位或借位。

列出真值表-

M

A

B

CI

CO

S

M

A

B

CI

CO

S

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

1

1

0

0

1

1

1

0

0

1

0

0

1

1

0

1

0

1

1

0

0

1

1

1

0

1

0

1

1

1

0

0

1

0

0

0

1

1

1

0

0

0

1

0

1

0

1

1

0

1

1

0

1

0

0

0

1

1

0

1

0

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

,

根据最小项译码器的特点Di=mi’,再利用与非门实现最小项相与的形式,Y=(mi’mj’mk’……)’=mi+mj+mk+……

依此连接电路-

通过WordGenerator产生输入信号,按Burst方式遍历所有的输入类型-

在虚拟仪表栏中选择LogicAnalyzer,读取逻辑图-

6.3.3显示译码器4511BD

4511BD可将BCD码转化为7段显示码,LT’为灯测试输入,LT’=0,显示8,BI’为灭灯输入,EL’=0时正常显示,EL’由0跳变成1后,保持当前的显示不变。

在由4511BD接入显示器时,根据数码管的参数,前向导通电压为1.66V,开门电流为5mA,中间加入限流电阻R=(5-1.66)V/5mA=668

,所接电阻应略小于此阻值。

6.4数据选择器

应用双四选一的数据选择器74LS153来完成6.3.2中的问题。

先将上例的卡诺图进行化简-

S=AB’CI’+A’B’CI+ABC+A’BCI’CO=BCI+ACIM’+ABM’+A’MCI+A’BM

根据两式的特点,选择AB作为地址输入端,式子进一步转化为-

S=A’B’(CI)+A’B(CI’)+AB’(CI’)+AB(CI)CO=A’B’(CM)+A’B(M+C)+AB’(M’C)+AB(M’+C)

将Y1作为S端,Y2作为CO端,相应连接各个地址的输入。

在WordGenerator中设定STEP循环模式,依次可以验证不同输入时S和CO的输出。

6.5加法器

用74LS238及相关门电路设计两个四位二进制数的加减法器,两数之和小于15,没有来自上一级的进位或借位。

当M=0时,执行a3a2a1a0+b3b2b1b0;M=1时执行a3a2a1a0-b3b2b1b0,输出都为补码。

分析:

M=1时,对b3b2b1b0求补码后再与a3a2a1a0相加,可先对b3b2b1b0求反码,在加上1来实现。

故M=0时,Bi=bi,进位CI=0;M=1时,Bi=bi’,进位CI=1。

可以用Bi=bi

M,CI=M。

M=0时,因两数之和小于15,CO=0,结果比为正,S=0;M=1时,若CO=1,与b3b2b1b0的符号位1相加,结果应为0,S=0。

若CO=0,结果应为1,S=1。

综上,S可以表示为S=M

CO。

连线后,下图的电路可以交互的进行上述运算。

6.6数值比较器

用两片74LS85设计两个五位二进制数的比较器。

分析:

先进行低四位的比较,再进行第五位的比较。

第四位芯片的AGTB(A>B)AEQB(A=B)ALTB(A 再将第一个芯片的输出结果接到第二片相应的输入上。 第二片的高三位接1或0。 下图为仿真的比较结果。 6.7组合逻辑电路的竞争冒险现象 在组合逻辑电路,门电路的两个输入同时向相反的逻辑方向跳变的现象称为竞争,由于竞争而在电路输出端产生尖峰脉冲的现象称为竞争-冒险。 由于输入信号传输到输出端的路径和时间不同,就会产生不应该有的尖峰脉冲。 下图输出Y=BC+AC’在A=B=1时输出本应为1,但因为C和C’到达的路径不同,会产生如图所示的尖峰脉冲。 在改进电路中加入了冗余项AB,Y=AC’+BC+AB。 可以克服此缺点。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 部分 一组 逻辑电路 王翰卓

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx