正弦发生器模块方案.docx

正弦发生器模块方案.docx

- 文档编号:29752440

- 上传时间:2023-07-26

- 格式:DOCX

- 页数:29

- 大小:855.98KB

正弦发生器模块方案.docx

《正弦发生器模块方案.docx》由会员分享,可在线阅读,更多相关《正弦发生器模块方案.docx(29页珍藏版)》请在冰豆网上搜索。

正弦发生器模块方案

SinCtrlAlteraDSPBuilderProductSignalTapII

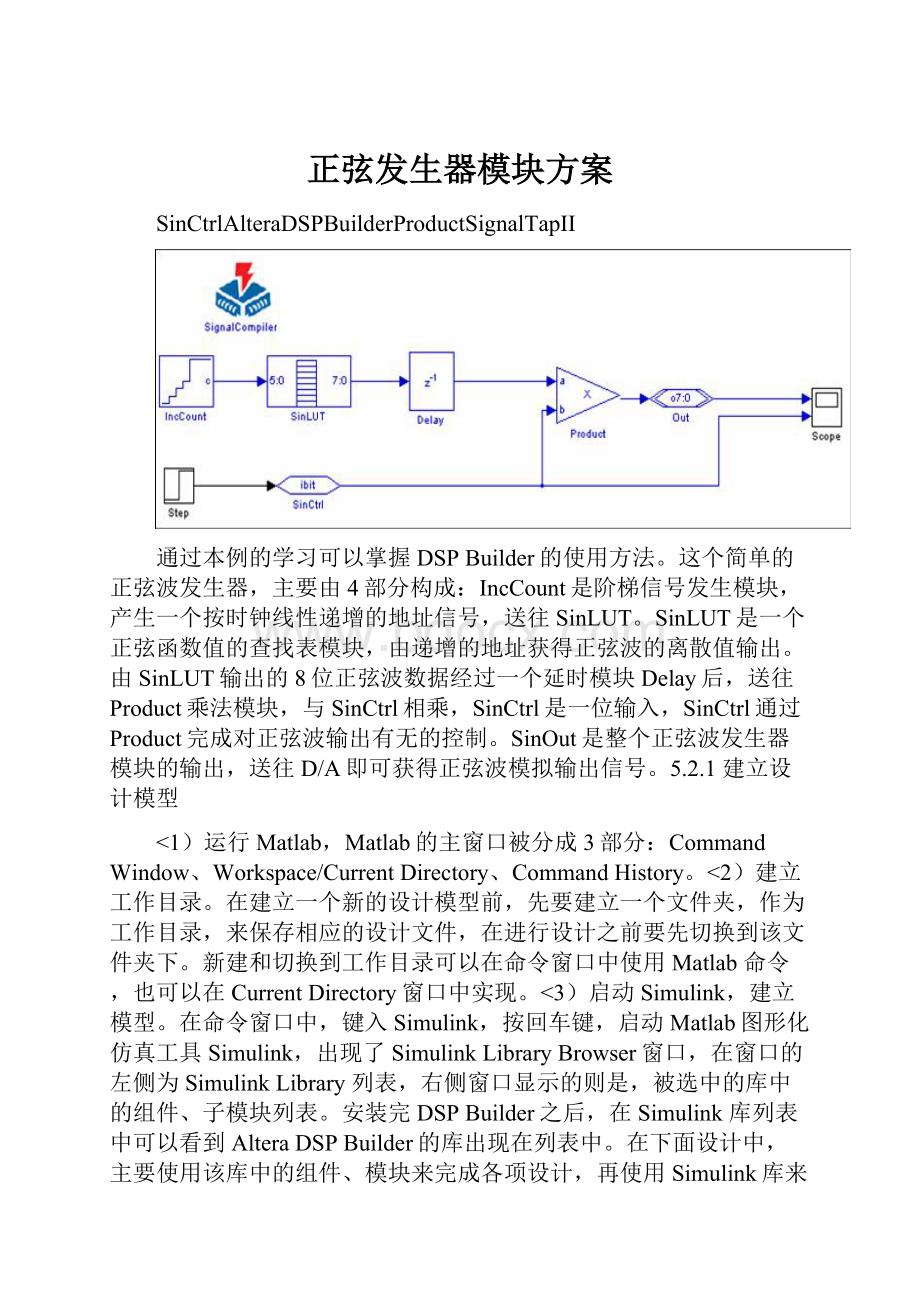

通过本例的学习可以掌握DSPBuilder的使用方法。

这个简单的正弦波发生器,主要由4部分构成:

IncCount是阶梯信号发生模块,产生一个按时钟线性递增的地址信号,送往SinLUT。

SinLUT是一个正弦函数值的查找表模块,由递增的地址获得正弦波的离散值输出。

由SinLUT输出的8位正弦波数据经过一个延时模块Delay后,送往Product乘法模块,与SinCtrl相乘,SinCtrl是一位输入,SinCtrl通过Product完成对正弦波输出有无的控制。

SinOut是整个正弦波发生器模块的输出,送往D/A即可获得正弦波模拟输出信号。

5.2.1建立设计模型

<1)运行Matlab,Matlab的主窗口被分成3部分:

CommandWindow、Workspace/CurrentDirectory、CommandHistory。

<2)建立工作目录。

在建立一个新的设计模型前,先要建立一个文件夹,作为工作目录,来保存相应的设计文件,在进行设计之前要先切换到该文件夹下。

新建和切换到工作目录可以在命令窗口中使用Matlab命令,也可以在CurrentDirectory窗口中实现。

<3)启动Simulink,建立模型。

在命令窗口中,键入Simulink,按回车键,启动Matlab图形化仿真工具Simulink,出现了SimulinkLibraryBrowser窗口,在窗口的左侧为SimulinkLibrary列表,右侧窗口显示的则是,被选中的库中的组件、子模块列表。

安装完DSPBuilder之后,在Simulink库列表中可以看到AlteraDSPBuilder的库出现在列表中。

在下面设计中,主要使用该库中的组件、模块来完成各项设计,再使用Simulink库来完成模型的仿真和验证。

选择File菜单,然后单击new,在弹出的子菜单中选择Model,出现了一个未命名的模型窗口。

<4)放置SignalCompiler。

单击Simulink库列表中的AlteraDSP,单击Altlab项,使之展开。

选中右侧窗口中的SignalCompiler组件,按住鼠标左键拖放到新模型窗口中。

也可以单击右键,选择Addto‘untitled’,这里’untitled’是指我们新建的未命名的模型文件。

在选中SignalCompiler模块后,在Simulink窗口中的提示栏里会显示对应模块的说明,简单的功能介绍。

可以看到SignalCompiler的介绍为“ConvertsModelFilestoVHDLfiles.”即为进行模型文件mdl到VHDL文件的转换,所以SignalCompiler是进行任何DSP系统设计必须要添加的模块。

选中SignalCompiler选中Helpforthe‘SignalCompiler’block。

可以了解怎样使用SignalCompiler的具体信息。

也可以按照此方法获得其它的模块相应的帮助信息。

<5)添加IncrementDecrement模块。

IncrementDecrement模块是DSPBuilder库中Arithmetic子库中的模块。

选中AlteraDSPBuilder中的Arithmetic子库,然后在其中选择IncrementDecrement模块。

然后按照添加SignalCompiler的方法将IncrementDecrement添加到模型文件中。

<7)添加正弦查找表。

在AlteraDSPBuilder库的Gate&Control子库中找到查找表模块LUT,把LUT拖放到新建模型窗口,将LUT模块的名字修改为“SinLUT”。

双击SInLUT模块,打开模块参数设置对话框“BlockParameters:

SinLUT”。

把输出位宽设为8;查找表地址设为6;总线数据类型BusType选择为有符号整数SignedInteger;在MatlabArray编辑框中输入计算查找表内容的计算式。

在这里使用sin函数,sin函数的调用格式为:

sin<[起始值:

步进值:

结束值])

SinLUT是一个输入地址为6位,输出值位宽为8位的正弦查找表模块,且输入地址总线为有符号数,所以设置起始值为0,结束值为2,步进值为,计算式可写成:

127*sin([0:

2*pi/2^6:

2*pi]>其中pi就是常数,这是Matlab中的语法。

上式的数值变化范围是-127~+127,恰好是8位二进制数可以表示的最大值,所以8位的输出值位宽可以表示上式所描述的正弦波形。

如果将SinLUT模块的总线数据类型设置为无符号整数UnsignedInteger,且输出位宽改为10,若想得到完成满度的波形输出,应将表达式改为:

511*sin([0:

2*pi/2^6:

2*pi]>+512选中”UseLPM” LibraryofParameterizedModules参数化模块),如果选中”UseLPM”的话,QuartusII将利用目标器件中的嵌入式RAM来构成SinLUT,即将生成的正弦波数据放在嵌入式RAM构成的ROM中,这样可以节省大量的逻辑资源,否则SinLUT只能用芯片中的LCs来构成。 选中”RegisterAddress”,选中此选项会生成输入地址总线,如果目标器件是Straitix或者Cyclone,并且选中了LPM选项,用户必须选中”RegisterAddress”选项。 <8)添加Delay模块。 在AlteraDSPBuilder库中,选中Storage子库下的Delay模块,拖放到新建模型窗口。 Delay模块可以实现延时的功能,在这里可以使用其默认参数设置。 在Delay模块的参数设置的对话框中,参数Depth是描述信号延时深度的参数。 当Depth为1,模块传输函数为1/Z,通过Delay模块的信号被延时一个时钟周期;当Depth为整数n时,其传输函数为1/Zn,通过Delay模块的信号将被延时n个时钟周期。 Delay模块在硬件上采用寄存器来实现,所以Delay模块被放在Storage子库中。 ClockPhaseSelection参数主要是控制采样的。 当设置为1表示Delay模块总处于使能状态,所用的数据都通过Delay模块。 如果设置为10则每隔一个脉冲处于使能状态,那么每隔一个的数据才能通过Delay模块。 如设置为0100,表示Delay模块在每4个时钟中第二个时钟是处于使能,那么每4个数据只有第二个数据可以通过。 <9)添加断口SinCtrl。 在AlteraDSPBuilder库中选择IO&BUS子库,找到AltBus模块,拖放到新建模型窗口中。 修改AltBus模块的名字为SinCtrl。 SinCtrl是一个1位输入端口。 双击SinCtrl模块,打开模块参数设置对话窗口。 设置SInCtrl的BusType为”SingleBit”,NodeType参数为”InputPort”。 <10)添加Product<乘法)模块。 在AlteraDSPBuilder库中选择Arithmetic子库,找到Product模块。 将之拖放到新建模型窗口中去,这里Product有两个输入一个是经过Delay的SinLUT输出,另一个是一位端口SinCtrl,Product实现了SinCtrl对SinLUT查找表输出的控制。 双击Product模块,打开Product模块参数设置对话框。 其中Pipeline<流水线)参数指定该乘法器模块使用几级流水线,即乘积延时几个时钟周期后输出,选中”UseLPM”,表示使用参数化的模块库来实现,选择”UseDedicatedCircuitry”表示可以使用FPGA中的专用模块来实现.(11>添加输出端口Out。 在AlteraDSPBuilder库中,选择IO&BUS子库,找到AltBus模块,拖放到信件模型窗口中,修改AltBus模块的名字为Out。 Out是一个8位输出端口,接到FPGA的输出引脚,与片外的8位D/A转换器相接,D/A转换模块将数字信号转化成模拟信号。 双击Out模块,打开参数设置对话框,设置Out的BusType为”SignedInteger”,NodeType参数为”OutputPort”,然后单击Apply,然后修改”Numberofbits”为8。 。 Saturate选项如果被选中,则当输出大于要表达的值的最大正值或负值,则输出被强制为最大的正值或负值。 若此选项未被选中,则最高位MSB被截断。 此选项对输入端口和常数节点类型是无效的。 <12)保存设计文件。 放置完Out模块,把新建模型中的DSPBuilder模块连接起来,这样就完成了一个正弦波发生器的DSPBuilder模型设计。 在进行仿真验证和SignalCompiler编译之前,先把设计保存起来。 单击File菜单,选择Save操作,取名并保存。 本例中,新建模型取名Sinout,生成模型文件Sinout.mdl。 模型保存之后,先要对模型进行仿真验证,如通过验证,则使用SignalCompiler进行编译将mdl文件转换为VHDL文件。 5.2.2Simulink模型仿真 Matlab的Simulink环境具有强大的图形化仿真验证的功能。 用DSPBuilder模块设计好的模型,可以在simulink中进行算法级、系统级仿真验证。 对一个模型进行仿真需要施加合适的激励,在特定的观察点添加必须的观察模块。 1.加入Step模块本例中,先加入一个step<阶跃模块),来实现模拟SinCtrl的按键使能操作。 在simulink的simulink基本库中,选择Source子库,把其中的Step模块拖放到Sinout模型窗口中去,并将其与SinCtrl的输入端口相连。 注意: 凡是来自AlteraDSPBuilder库以外的模块,SignalCompiler都不能将其转换成硬件描述语言的模块。 2.添加波形观察模块在Simulink中选择Simulink库,展开Simulink库,选中其中的Sinks子库,把Scope<示波器)模块拖放到SinOut模型窗口中去。 双击该模块,打开的是一个Scope窗口。 如图5-11所示,图中只有一个信号的波形观察窗口,若希望可以多观察记录信号,可以通过添加多个Scope模块的方法来实现,也可以通过修改Scope的参数来实现Scope模块中的观察窗口数。 3.Scope模块参数设置用鼠标单击Scope模块窗口上侧工具栏的第二个按钮: Parameters,弹出参数设置对话框,以进行参数设置。 在Scope参数设置对话框中有两个设置页: General和DataHistory。 在General页中,改变Numberofaxes为2。 在单击OK按钮后,可以看到Scope窗口出现了两个波形观察窗。 每个观察窗可以独立地观察信号波形。 同时Scope模块也多了一个输入端,将SinCtrl的信号接到这一新增的输入端,作为参考信号。 4.设置仿真激励先设置模型的仿真激励。 在SinOut模型中,只有一个输入端口SinCtrl,需要设置与之相连的Step模块。 双击Step模块,在弹出的Step模块参数设置对话框中设置对其输入端口SinCtrl施加的激励。 各参数值的含义如下: 阶跃时刻 Step模块的输出在该时刻发生阶跃,默认值为1,单位为秒。 初始值 在阶跃时刻的之前的Step模块的输出值,默认值为0。 终值 在阶跃时刻之后Step模块的输出值,默认值为1。 采样时刻 Step模块输出的采样频率。 设置Steptime为30,则在30秒时该模块会发生输出值的阶跃。 初始值设为0,那么在30秒时刻之前,不输出正弦波;终值设为1。 Sampletime设为0,设为0的话,在大的和小的时间间隔都进行采样,设成0的模块被称作连续采样;设成1的话,则只在大的时间间隔上采样。 选中底部的两项选择: “Interpretvectorparametersas1-D”和“Enablezerocrossingdetection”在SInOut模型窗口中,单击Simulation菜单,在下拉菜单中选择Simulationparameters。 将弹出SinOut模型的仿真参数设置对话框: ”ConfigurationParameters: SinOut/configuration”。 仿真参数设置对话框共有7个选项页: Solver、DataImport/Export、Optimization、Diagnostics、HardwareImplementation、ModelReferencing、Real-TimeWorkshop。 其中”Solver”页中完成仿真时的基本时间设置、计算器和解算器 5.启动仿真在SinOut模型窗口中,选恶Simulation菜单下的Start项,开始仿真。 仿真结束后,双击Scope模块,打开Scope观察窗。 出现如图5-15所示的仿真结果。 可以看到SinOut受到了SinCtrl的控制。 6.设计成无符号数据输出由示波器的波形可以看到,输出的正弦波是有符号的数据,在127间变化,但一般的D/A器件的输入数据都是无符号的正数。 因此为了能在硬件系统上D/A的输出也能观察到此波形,必须对此输出做一些改进,以便输出无符号数。 最简单的方法就是将输出波形向上平移127即可,SinLut的BusType设置为”UnsignedInteger”,SinLut的波形数据公式改为: 127*sin([0: 2*pi/(2^6>: 2*pi]>+128。 然后将输出端口Out的BusType改为”Unsignedinteger”类型。 修改完成之后,进行仿真,可以看到输出的波形都在0以上。 5.2.3使用SignalCompiler进行从算法到硬件实现 在Matlab中完成仿真验证后,就要把设计转换到硬件上加以实现。 通过DSPBuilder可以获得针对特定FPGA芯片的HDL代码。 1.分析模型双击SinOut模型中的”SignalCompiler”图标启动DSPBuilder,出现如下的窗口: 单击”Analyze”按钮,SignalCompiler将会对模型进行分析,检查模型有无错误。 如果设计存在错误,将会停止分析过程,并在Matlab软件的命令窗口中给出相关信息。 如果设计不存在错误,则在分析结束后打开”SignalCompiler”窗口。 Simulink具有强大的错误定位能力,对许多错误可以在simulink模型中直接定位,用不同的颜色来标示有错误的模块。 如果SignalCompiler分析当前的DSP模型有错误时,必须修改正确才能继续下面的设计流程。 2.设置SignalCompiler在SignalCompiler窗口中,要进行一些必要的设置。 SignalCompiler窗口大致上可以分为3个功能部分: 左上为工程设置选项——ProjectSettingOptions;右上为硬件的编译流程——HardwareCompilation;下方为信息框——Messages。 SingalCompiler的设置集中在工程设置选项部分。 在Device下拉选择框中选择目标器件的系列。 这里只能选择器件的系列,不能指定具体的器件型号,这需要由QuartusII自动决定使用该器件系列中的某一个具体型号的器件,或在手动流程中由用户指定。 在Synthesis<综合)下拉选择框中,可以选择综合器,共有3个选项: Mentor的LeonardoSpectrum综合器;Synplicity的Synplify综合器;Altera的QuartusII,QuartusII是FPGA/CPLD的集成开发环境,其内含综合功能。 在Optimization<优化)下拉选择框,指明在综合、适配过程中的优化策略,是优先对面积 工程设置选项部分的下部是一些选项页,包括下面的内容: MainClock: 系统主时钟的周期的设置;Reset: 系统复位信号的设置;SignalTapII: 嵌入式逻辑分析仪的设置;Testbench: 仿真测试文件生成的选择;SOPCinfo: SOPC相关设置。 MainClock的缺省值为20ns,即对应50MHz的频率。 如果要使用第三方的仿真软件<如ModelSim)则在Testbench页中,选中”GenerateStimuliforVHDLTestbench.”,生成第三方VHDL仿真软件的激励测试文件。 如若不然不要选择此选项,选择此选项的话,simulink运行会比没选中此选项的情况下慢很多。 3.把模型文件Mdl转化成VHDL文件完成上面的设置之后,信息窗口会提示用户进行Mdl文件到VHDL文件的转换操作。 点击1.ConvertMDLtoVHDL的图标,执行mdl模型文件到VHDL文件的转换。 转换完成后,Message框中会出现如下的提示>Generatedtoplevelfile‘Sinout.vhd’>CompletedMDLtoVHDLconversion>See‘Sinout_DspBuilder_Report.html’reportfileforadditionalinformation以上提示说明了: 产生了Sinout.vhd的顶层文件,完成了mdl文件到VHDL文件的转换,更多的信息,参看Sinout_DspBuilder_Report.htm文件,点击ReportFile按钮即可。 4.综合单击步骤2的图标,执行综合过程,这里选择的综合工具是QuartusII,综合后生成AtomNetlist<网表)文件,以供第三步适配过程使用。 综合过程完成之后,信息框中会给出此工程的一些信息: 如器件的系列,使用的逻辑宏单元的数目、触发器的数目、引脚数、RAM容量等。 详细的信息也是参照上面提到的工程报告文件。 5.QuartusII适配单击步骤3的图标,调用QuartusII完成编译适配过程,生成编程文件: pof文件和sof文件。 单击Report按钮,查看详细的报告信息。 以上的三个步骤可以分开单步执行,也可以点击’executesteps1,2and3”,一步执行。 6.编程完成了以上三步操作之后,programdevice的图标由不可用编程可用<由灰变亮),连接好硬件便可以进行下载了。 但在下在之前,还要做一些必要的仿真和测试: 使用ModelSim进行RTL级仿真,使用QuartusII进行时序仿真,进行硬件测试等。 5.2.4使用ModelSim进行RTL级仿真 在Simulink中已经对模型进行过仿真验证,但是是属于系统级的验证,并没有对生成的VHDL代码进行过仿真。 事实上,由Mdl文件转化而来的VHDL描述是RTL级的,而在simulink中的模型仿真是算法级的,转换后的代码实现可能与mdl模型描述的情况不完全相符。 这就需要针对生成的RTL级VHDL代码进行功能仿真。 当在SignalCompiler设置窗口中的Testbench页中选中”GenerateStimuliforVHDLTestbench”,DSPBuilder在mdl转换到VHDL的过程中会生成对HDL仿真器ModelSim的测试文件。 ModelSim是MentorGraphics的子公司ModelTechnology的产品,ModelSim是业界最优秀的HDL语言仿真器,具有快速的仿真性能和最先进的调试能力,支持众多的ASIC和FPGA厂家库,是作FPGA、ASIC设计的RTL级和门级电路仿真的首选。 是唯一的单内核支持VHDL和Verilog混合仿真的仿真器,全面支持VHDL和Verilog语言的IEEE标准,以及IEEEVITAL1076.4-95标准,支持C语言功能调用,支持C模型、基于SWIFT的SmartModel逻辑模型和硬件模型的仿真。 它具有丰富而又易用的图形用户界面,提供最友好的调试环境,为加快调试提供强有力的手段。 仿真方法: 启动ModelSim软件,选择Tools菜单下的ExecuteMacro…,在打开的文件选择对话框中切换到SinOut模型SinOut.mdl文件所在的目录,选择tb_SinOut.tcl,ModelSim执行tb_SinOut.tcl,开启仿真,随后会自动打开wave窗口,显示仿真结果。 但是显示的结果是以数字形式显示的,与simulink中的仿真结果没有可比性。 为了能够进行对比,要改变输出波形的显示方式。 选中”tb_sinout/outu”,单击右键,在弹出菜单中选择properties…,出现waveproperties窗口,缺省显示的View页面。 在对话框中将Radix项的内容设为”Unsigned”。 然后点击Format页,在Format页中将Format设成Analog,Height设成100,Scale设成0.4,然后点击OK。 5.2.5使用QuartusII进行时序仿真 ModelSim软件只能实现对设计电路的功能仿真,其仿真结果没有反映电路的硬件的真实情况。 为了使我们的设计与真实的电路更加接近,进行设计的时序仿真是非常必要的。 SignalCompiler已经生成了用于quartusII进行时序仿真的激励文件sinout.vec和相关仿真文件,如sinout_quartus.tcl,可以很容易地在quartusII中实现时序仿真,在quartusII进行时序仿真的步骤如下: 启动quartusII集成开发环境,执行File菜单的OpenProject…的操作,在弹出的OpenProject的对话框中,选择Sinout模型所在的目录,打开该目录,打开DSPBuilder为QuartusII建立的设计工程——Sinout,并在工程中打开VHDL顶层设计文件sinout.vhd。 在SignalCompiler中的编译过程中,我们已经指定了器件为CycloneII系列了,但是在QuartusII中进行时序仿真时,需要指定器件的具体型号。 执行Assignments菜单的Device…命令,为本设计选择目标芯片EP2C35F672C8。 然后执行Processing菜单的StartCompilation命令对sinout.vhd顶层文件进行编译。 编译结束后,执行Processing菜单的StartSimulation命令,启动时序仿真。 在仿真过程结束之后,出现quartusII仿真波形界面,显示仿真结果。 通过观察仿真波形来检查设计的工程是否满足时序要求。 也可以运行TimeQuestTimingAnalyzer,生成时序分析报告,来获取时序仿真的数据。 5.2.6硬件实现与测试 经过RTL级和时序仿真之后,还要将设计下载到芯片中进行实现和测试。 进行硬件测试时,需要使用开发平台上的DAC器件将正弦波信号发生器所输出的数字信号转换为模拟信号,然后将模拟信号接到示波器上。 要使用DAC器件,需要将平台上的拨码开关的MODUL_SEL1设置成“ON”状态,将MODUL_SEL2和MODUL_SEL3设置成“OFF”状态。 开发平台上的DAC模块由一个并行8位DAC器件和一个并行DAC电压基准源组成,并行8位DAC器件采用AnalogDevice公司的AD7302芯片,工作电压为2.7伏到5.5伏,功耗小适合于电池驱动应用,具有高速寄

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 正弦 发生器 模块 方案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx