PCIExpress总线的接口电路设计.docx

PCIExpress总线的接口电路设计.docx

- 文档编号:2968826

- 上传时间:2022-11-16

- 格式:DOCX

- 页数:12

- 大小:289.27KB

PCIExpress总线的接口电路设计.docx

《PCIExpress总线的接口电路设计.docx》由会员分享,可在线阅读,更多相关《PCIExpress总线的接口电路设计.docx(12页珍藏版)》请在冰豆网上搜索。

PCIExpress总线的接口电路设计

PCI-Express总线的接口电路设计

王福泽(天津工业大学)

一、课题背景

计算机I/O技术在高性能计算发展中始终是一个关键技术。

其技术特性决定了计算机I/O的处理能力,进而决定了计算机的整体性能以及应用环境。

从根本上来说,无论现在还是将来,I/O技术都将制约着计算机技术的应用与发展,尤其在高端计算领域。

近年来随着高端计算市场的日益活跃,高性能I/O技术之争也愈演愈烈。

当计算机运算处理能力与总线数据传输速度的矛盾日益突出时,新的总线技术便应运而生。

在过去的十几年间,PCI(PeripheralcomponentInterconnect)总线是成功的,它的平行总线执行机制现在看来依然具有很高的先进性,但其带宽却早已露出疲态。

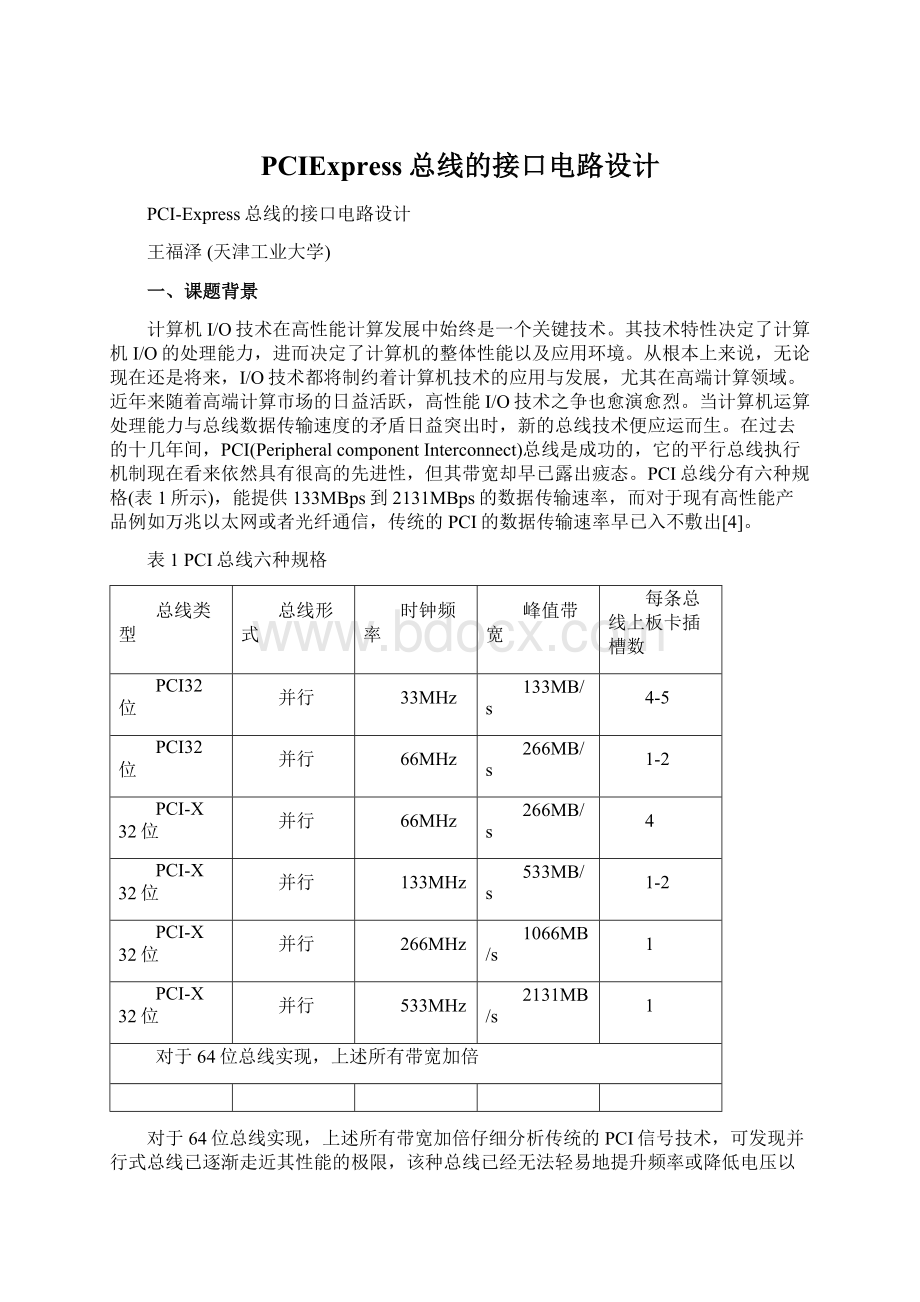

PCI总线分有六种规格(表1所示),能提供133MBps到2131MBps的数据传输速率,而对于现有高性能产品例如万兆以太网或者光纤通信,传统的PCI的数据传输速率早已入不敷出[4]。

表1PCI总线六种规格

总线类型

总线形式

时钟频率

峰值带宽

每条总线上板卡插槽数

PCI32位

并行

33MHz

133MB/s

4-5

PCI32位

并行

66MHz

266MB/s

1-2

PCI-X32位

并行

66MHz

266MB/s

4

PCI-X32位

并行

133MHz

533MB/s

1-2

PCI-X32位

并行

266MHz

1066MB/s

1

PCI-X32位

并行

533MHz

2131MB/s

1

对于64位总线实现,上述所有带宽加倍

对于64位总线实现,上述所有带宽加倍仔细分析传统的PCI信号技术,可发现并行式总线已逐渐走近其性能的极限,该种总线已经无法轻易地提升频率或降低电压以提高数据传输率:

其时钟和数据的同步传输方式受到信号偏移及PCB布局的限制。

高速串行总线的提出,成功的解决了这些问题,其代表应用就是PCIExpress。

PCIExpress采用的串行方式,并且真正使用“电压差分传输”即是两条信号线,以相互间的电压差作为逻辑“0”,“1”的表示,以此方式传输可以将传输频率作极高的提升,使信号容易读取,噪声影响降低。

由于是差分传输,所以每两条信号线才能单向传送1比特,即一根信号线为正、另一根信号线为负,发送互为反相的信号,每一个“1比特”的两条信号线称为一个差分对。

按PCIExpress技术规范规定,一个差分对的传输速率为2.5Gbps。

实际使用中,则要使用两个差分对作为一个条链路,分别用做发送和接收。

因为有了这样的机制,使得数据带宽是可以弹性调配的。

根据相关标准PCI-Express总线能够以xl/x2/x4/x8/x12/x16/x32进行传输(如表2所示),可提供5Gbps到160Gbps的传输带宽。

当系统内某一通道需要更高频宽时,可以机动调度多个链路给该通道,让其传输频宽提升,以适应一时激增的数据传输需求[1]。

表2PCI-Express多链路传输速率表

PCIExpress链路宽度

X1

X2

X4

X8

X12

X16

X32

传输带宽(Gb/s)

5.0

10.0

20.0

40.0

60.0

80.0

160.0

有效带宽(Gb/s)

4.0

8.0

16.0

32.0

48.0

64.0

128.0

8b/10b编码使实际有效数据带宽损失20%,每链路包含一对发送/接收模块,每模块单项传输带宽2.5Gb/s

除了传输方式的改变外,PCIExpress还有一个更有意义的改变,即连接方式的改变。

PCIExpress采用点对点连接方式,较PCI的共享总线方式是一个重要的进步。

对于PCI的共享总线方式,PCI总线上在某一时刻只能有一个设备进行通信,一旦PCI总线上挂接的设备增多,每个设备的实际传输速率就会下降,性能也得不到保证。

而PCIExpress则采用一种较为先进的连接方式,以点对点的方式处理通信,每个设备在要求传输数据时建立独立的传输通道,对于其它设备这个信道是封闭的,这种操作方式保证了通道的专有性,避免其它设备的干扰,使信号的质量和可靠性增加。

由于是点对点的关系,也很好的保证了其扩展性。

由于PCI-Express只是扩展总线,与操作系统无关,也可保证其与原有PCI的兼容性,给用户的升级带来了方便。

下图为PCI-Express的拓扑结构。

图1PCI-Express系统拓扑结构

PCIExpress不但具有高性能的传输速率,而且其通用性也有重要的意义。

由于其通用的模式,不仅可用于北南桥和其它设备的连接,也可以延伸到芯片组间的连接,甚至也可以用于连接图形芯片。

这样整个计算机的I/O系统将重新统一起来,将更进一步的简化计算机系统,使其具有更强的通用性。

从目前己经显现的特点看,PCIExpress一改传统PCI的并行总线架构,因此比其它I/O技术有着更为领先的带宽优势,随着时间的推移有逐步取代PCI和PCI-X的趋势。

PCIExpress被广泛地认为是一项革命性的总线技术,其重要性可以满足不同使用者的需求。

随着未来持续增加的带宽需求,PCIExpress具有广泛的应用前景[2]。

二、基于FPGA的PCI-Express接口具体设计方案

本设计将采用Xilinx公司最新的Virtex5LXT设计平台,使用了两个用于实现PCIExpress功能的集成端点模块,其中一个模块(主控模块)具有配置另一个模块(从属模块)的功能。

数据可以在这两个集成端点模块之间双向(即在全双工模式下)流动。

该设计的用户接口是通过本地链路(LL)接口提供的。

该设计能够在x1、x2、x4和x8通道配置下操作[3]。

设计功能如下:

•用户接口的本地链路成帧接口

♦64位数据总线宽度与3位提醒总线

♦包化接口,带用于标记包的帧起始(SOF)和帧结束(EOF)

•传输和接收方向用户接口的包中断特性

•帧错误检测支持

•多通道配置支持:

x1、x2、x4和x8

•每通道1.62Gb/s或更高的吞吐量

•自动初始化、恢复与通道维护,对用户应用是透明的

•Virtex-5LXT器件中的集成端点模块

1.XilinxIP核及其应用说明

该设计的完整框图如图3所示。

两个端点可以直接通信,其中一个模块(主控模块)具有配置另一个模块(从属模块)的功能,数据可以在两个集成端点模块之间双向流动,用户接口由本地接口提供。

图3基于PCI-Express的点到点连接结构框图

其中主控端可以在本地自行配置,另一端作为从属端,由主控端通过PCI-Express链路进行配置。

进行配置后,该设计便已经准备好可以在全双工模式下进行数据传输操作了。

设计的用户接口符合本地链路协议的要求。

在传输期间,用户提供的本地链路帧在前往集成端点模块进行传输之前,会先被转换成传输层包(TLP)。

在接收期间,来自集成端点模块的TLP会被转换正本地链路帧,而数据以及其他控制信号将通过本地链路接口传送给用户,因此,PCI-Express会分为三个架构模块:

配置IP(configIP)、ContextIP传输和ContextIP接收。

配置IP模块

配置IP模块负责在本地配置主控端,并通过PCIExpress协议链路配置从属端。

配置完成后,会触发LINK_READY,以表明链路已准备好可以进行数据传输了。

配置期间,将在主控端和从属端设置最大有效载荷大小。

配置IP会根据选择的用户设计选项设置集成端点模块的最大有效载荷大小(MPS),如果是设计选项1,则设置为512字节,如果是设计选项2,则设置为1024字节。

ContextIP传输模块

ContextIP传输模块采用存储转发技术原理,通过协议链路以存储器写TLP的形式传输用户帧。

存储器写TLP标头中的TAG区段未经过定义,可以包含任何值,因此可用于存储帧起始、帧结束、帧中断等标记,这些标记有助于在收到结束信号时重建本地链路帧。

传输器逻辑可将从用户处传来的数据存储在FIFO中。

FIFO的容量等于为选定设计选项设置的MPS。

长度计数器会对有效载荷的长度进行计数,有效载荷的长度用于建立TLP标头中的长度区段。

计数器在达到最高计数值(MPS=512时为511,MPS=1024时为1023)后会归零。

帧的长度会存储在长度缓冲器内。

Context传输框图如下图所示:

图4Context传输框图

Virtex-5器件中的内置FIFO用于进行存储。

如果数据传输之间的链路断开(LINK_UP信号变为低),则当前存储在缓冲器内的所有数据都将丢失。

由于必须重新进行配置,因此可以将数据传输之间的链路断开视为复位。

如果用户帧大小小于在集成端点模块中设置的MPS,整个帧将作为单个TLP进行传输,。

ContextIP接收

该模块(如图5)可接收来自传输层接收接口的TLP,然后提取其中的有效载荷。

从TLP的TAG区段提取的标记位将被写入到接收端FIFO的数据奇偶位输入区段。

提取的数据以及相应的本地链路成帧信号会被发送给接收端的用户[6]。

图5ContextIP接收框图

2.PCI-Express端点IP核说明

Xilinx提供的EndpointBlockPlusforPCIe解决方案适用于Virtex™-5LXT/SXTFPGA架构,是一种可靠的高带宽可缩放串行互连构建模块。

其顶层功能模块如图6所示,从中可以看出,核接口分为系统(SYS)接口、PCI-Express(PCI-EXP)接口、配置(CFG)接口以及事务(TRN)接口。

图6顶层功能模块和接口

核使用数据包在各模块之间交换信息。

数据包在事务层和数据链路层形成,用来承载从发送元件到接收元件的信息。

传输的数据包中包括在各层处理数据包所需的必要信息。

在接收端,各层接收元件处理输入的数据包,剥取相关信息,然后将数据包传送到下一层。

于是,接收到的数据包从其物理层表现形式转换为数据链路层表现形式和事务层表现形式。

EndpointBlockPlusforPCIe核包括顶层信号接口,这些接口按接收方向、发送方向和双向共用信号分组。

下面主要对各个接口进行分别介绍。

系统(SYS)接口

系统(SYS)接口信号由系统复位信号sys_reset_n和系统时钟信号sys_clk组成,如下表所示:

表3系统接口信号

功能

信号名称

方向

描述

系统复位

Sys_reset_n

输入

异步低有效信号。

系统时钟

Sys_clk

输入

参考时钟:

100MHz或250MHz。

系统复位信号是异步低有效输入信号。

sys_reset_n的有效置位致使整个核(包括RocketI/OGTP和RocketI/OGTX收发器)硬复位。

复位信号发出后,核尝试进行链路初始化并恢复到正常工作状态。

在典型的端点应用中,通常存在应连接到sys_reset_n的边带复位信号。

系统输入时钟的频率必须是100MHz或250MHz,在CoreGenerator的GUI中选定。

PCI-Express系统的时钟控制方式有两种:

其一就是使用同步实在哦好难过控制,其中所有器件共用一个时钟源,另一种是使用非同步始终控制,其中各器件使用自己的时钟源[7]。

PCI-Express接口

PCIExpress(PCI_EXP)接口信号由按多个通道组织的收发差分信号对组成。

每个PCIExpress通道由一对发送差分信号{pci_exp_txp、pci_exp_txn}和一对接收差分信号

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- PCIExpress 总线 接口 电路设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx