VHDL源代码计数器.docx

VHDL源代码计数器.docx

- 文档编号:29496174

- 上传时间:2023-07-24

- 格式:DOCX

- 页数:17

- 大小:14.86KB

VHDL源代码计数器.docx

《VHDL源代码计数器.docx》由会员分享,可在线阅读,更多相关《VHDL源代码计数器.docx(17页珍藏版)》请在冰豆网上搜索。

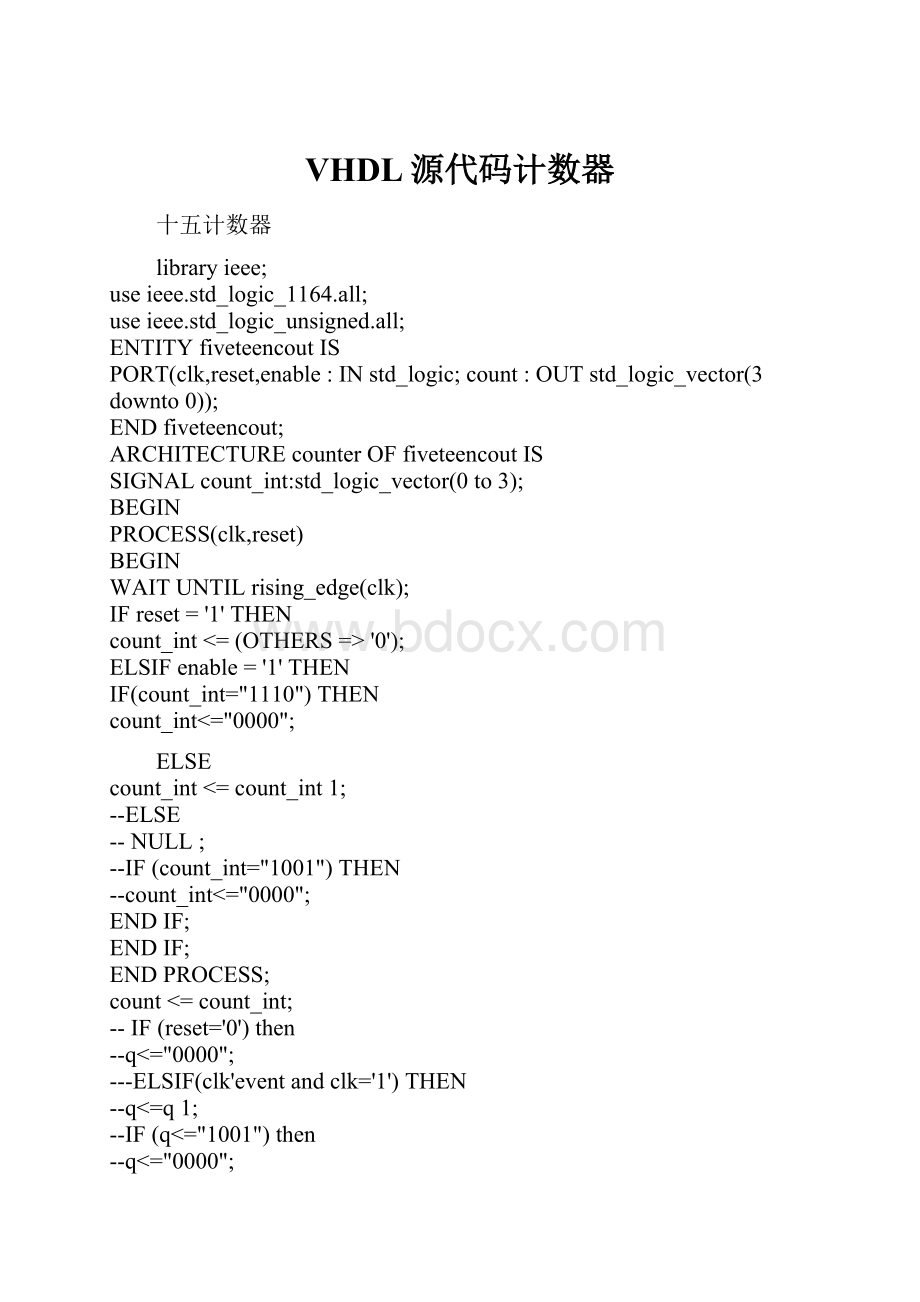

VHDL源代码计数器

十五计数器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYfiveteencoutIS

PORT(clk,reset,enable:

INstd_logic;count:

OUTstd_logic_vector(3downto0));

ENDfiveteencout;

ARCHITECTUREcounterOFfiveteencoutIS

SIGNALcount_int:

std_logic_vector(0to3);

BEGIN

PROCESS(clk,reset)

BEGIN

WAITUNTILrising_edge(clk);

IFreset='1'THEN

count_int<=(OTHERS=>'0');

ELSIFenable='1'THEN

IF(count_int="1110")THEN

count_int<="0000";

ELSE

count_int<=count_int1;

--ELSE

--NULL;

--IF(count_int="1001")THEN

--count_int<="0000";

ENDIF;

ENDIF;

ENDPROCESS;

count<=count_int;

--IF(reset='0')then

--q<="0000";

---ELSIF(clk'eventandclk='1')THEN

--q<=q1;

--IF(q<="1001")then

--q<="0000";

---ENDIF;

--IF(reset<='1')THEN

--q<="00";

--ELSIF

--waituntil(clk'eventandclk='1');

--WAITUNTIL(clk'EVENTANDclk='1');

--WAITUNTIL(clock'EVENTANDclock='1');

--q<=q'1';

--endif;

--count<=q;

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--clock'eventandclock='1';

--count<=0;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITriseedgeclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=1;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=2;

--endif;

--endif;

--endif;

--ENDPROCESS;

ENDcounter;

十四计数器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYfourteencoutIS

PORT(clk,reset,enable:

INstd_logic;count:

OUTstd_logic_vector(3downto0));

ENDfourteencout;

ARCHITECTUREcounterOFfourteencoutIS

SIGNALcount_int:

std_logic_vector(0to3);

BEGIN

PROCESS(clk,reset)

BEGIN

WAITUNTILrising_edge(clk);

IFreset='1'THEN

count_int<=(OTHERS=>'0');

ELSIFenable='1'THEN

IF(count_int="1101")THEN

count_int<="0000";

ELSE

count_int<=count_int1;

--ELSE

--NULL;

--IF(count_int="1001")THEN

--count_int<="0000";

ENDIF;

ENDIF;

ENDPROCESS;

count<=count_int;

--IF(reset='0')then

--q<="0000";

---ELSIF(clk'eventandclk='1')THEN

--q<=q1;

--IF(q<="1001")then

--q<="0000";

---ENDIF;

--IF(reset<='1')THEN

--q<="00";

--ELSIF

--waituntil(clk'eventandclk='1');

--WAITUNTIL(clk'EVENTANDclk='1');

--WAITUNTIL(clock'EVENTANDclock='1');

--q<=q'1';

--endif;

--count<=q;

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--clock'eventandclock='1';

--count<=0;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITriseedgeclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=1;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=2;

--endif;

--endif;

--endif;

--ENDPROCESS;

ENDcounter;

十三计数器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYthireteencoutIS

PORT(clk,reset,enable:

INstd_logic;count:

OUTstd_logic_vector(3downto0));

ENDthireteencout;

ARCHITECTUREcounterOFthireteencoutIS

SIGNALcount_int:

std_logic_vector(0to3);

BEGIN

PROCESS(clk,reset)

BEGIN

WAITUNTILrising_edge(clk);

IFreset='1'THEN

count_int<=(OTHERS=>'0');

ELSIFenable='1'THEN

IF(count_int="1100")THEN

count_int<="0000";

ELSE

count_int<=count_int1;

--ELSE

--NULL;

--IF(count_int="1001")THEN

--count_int<="0000";

ENDIF;

ENDIF;

ENDPROCESS;

count<=count_int;

--IF(reset='0')then

--q<="0000";

---ELSIF(clk'eventandclk='1')THEN

--q<=q1;

--IF(q<="1001")then

--q<="0000";

---ENDIF;

--IF(reset<='1')THEN

--q<="00";

--ELSIF

--waituntil(clk'eventandclk='1');

--WAITUNTIL(clk'EVENTANDclk='1');

--WAITUNTIL(clock'EVENTANDclock='1');

--q<=q'1';

--endif;

--count<=q;

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--clock'eventandclock='1';

--count<=0;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITriseedgeclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=1;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=2;

--endif;

--endif;

--endif;

--ENDPROCESS;

ENDcounter;

十二计数器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYtwelvecoutIS

PORT(clk,reset,enable:

INstd_logic;count:

OUTstd_logic_vector(3downto0));

ENDtwelvecout;

ARCHITECTUREcounterOFtwelvecoutIS

SIGNALcount_int:

std_logic_vector(0to3);

BEGIN

PROCESS(clk,reset)

BEGIN

WAITUNTILrising_edge(clk);

IFreset='1'THEN

count_int<=(OTHERS=>'0');

ELSIFenable='1'THEN

IF(count_int="1011")THEN

count_int<="0000";

ELSE

count_int<=count_int1;

--ELSE

--NULL;

--IF(count_int="1001")THEN

--count_int<="0000";

ENDIF;

ENDIF;

ENDPROCESS;

count<=count_int;

--IF(reset='0')then

--q<="0000";

---ELSIF(clk'eventandclk='1')THEN

--q<=q1;

--IF(q<="1001")then

--q<="0000";

---ENDIF;

--IF(reset<='1')THEN

--q<="00";

--ELSIF

--waituntil(clk'eventandclk='1');

--WAITUNTIL(clk'EVENTANDclk='1');

--WAITUNTIL(clock'EVENTANDclock='1');

--q<=q'1';

--endif;

--count<=q;

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--clock'eventandclock='1';

--count<=0;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITriseedgeclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=1;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=2;

--endif;

--endif;

--endif;

--ENDPROCESS;

ENDcounter;

十一计数器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYelevencoutIS

PORT(clk,reset,enable:

INstd_logic;count:

OUTstd_logic_vector(3downto0));

ENDelevencout;

ARCHITECTUREcounterOFelevencoutIS

SIGNALcount_int:

std_logic_vector(0to3);

BEGIN

PROCESS(clk,reset)

BEGIN

WAITUNTILrising_edge(clk);

IFreset='1'THEN

count_int<=(OTHERS=>'0');

ELSIFenable='1'THEN

IF(count_int="1010")THEN

count_int<="0000";

ELSE

count_int<=count_int1;

--ELSE

--NULL;

--IF(count_int="1001")THEN

--count_int<="0000";

ENDIF;

ENDIF;

ENDPROCESS;

count<=count_int;

--IF(reset='0')then

--q<="0000";

---ELSIF(clk'eventandclk='1')THEN

--q<=q1;

--IF(q<="1001")then

--q<="0000";

---ENDIF;

--IF(reset<='1')THEN

--q<="00";

--ELSIF

--waituntil(clk'eventandclk='1');

--WAITUNTIL(clk'EVENTANDclk='1');

--WAITUNTIL(clock'EVENTANDclock='1');

--q<=q'1';

--endif;

--count<=q;

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--clock'eventandclock='1';

--count<=0;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITriseedgeclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=1;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=2;

--endif;

--endif;

--endif;

--ENDPROCESS;

ENDcounter;

十计数器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYcountIS

PORT(clk,reset,enable:

INstd_logic;count:

OUTstd_logic_vector(3downto0));

ENDcount;

ARCHITECTUREcounterOFcountIS

SIGNALcount_int:

std_logic_vector(0to3);

BEGIN

PROCESS(clk,reset)

BEGIN

WAITUNTILrising_edge(clk);

IFreset='1'THEN

count_int<=(OTHERS=>'0');

ELSIFenable='1'THEN

IF(count_int="1001")THEN

count_int<="0000";

ELSE

count_int<=count_int1;

--ELSE

--NULL;

--IF(count_int="1001")THEN

--count_int<="0000";

ENDIF;

ENDIF;

ENDPROCESS;

count<=count_int;

--IF(reset='0')then

--q<="0000";

---ELSIF(clk'eventandclk='1')THEN

--q<=q1;

--IF(q<="1001")then

--q<="0000";

---ENDIF;

--IF(reset<='1')THEN

--q<="00";

--ELSIF

--waituntil(clk'eventandclk='1');

--WAITUNTIL(clk'EVENTANDclk='1');

--WAITUNTIL(clock'EVENTANDclock='1');

--q<=q'1';

--endif;

--count<=q;

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--clock'eventandclock='1';

--count<=0;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITriseedgeclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=1;

--WAITUNTIL(clock'EVENTANDclock='1');

--WAITUNTILclock='1';

--if(clock'eventandclock='1')then

--WAITUNTILrising_edge(clock);

--count<=2;

--endif;

--endif;

--endif;

--ENDPROCESS;

ENDcounter;

九计数器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYninecoutIS

PORT(clk,reset,enable:

INstd_logic;count:

OUTstd_logic_vector(3downto0));

ENDninecout;

ARCHITECTUREcounterOFninecoutIS

SIGNALcount_int:

std_logic_vector(0to3);

BEGIN

PROCESS(clk,reset)

BEGIN

WAITUNTILrising_edge(clk);

IFreset='1'THEN

count_int<=(OTHERS=>'0');

ELSIFenable='1'THEN

IF(count_int="1000")THEN

count_int<="0000";

ELSE

count_int<=count_int1;

--ELSE

--NULL;

--IF(count_int="1001")THEN

--count_int<="0000";

ENDIF;

ENDIF;

ENDPROCESS;

count<=count_int;

--IF(reset='0')then

--q<="0000";

---ELSIF(clk'eventandclk='1')THEN

--q<=q1;

--IF(q<="1001")then

--q<="0000";

---ENDIF;

--IF(reset<='1')THEN

--q<="00";

--ELSIF

--waituntil(clk'eventandclk='1');

--WAITUNTIL(clk'EVENTANDclk='1');

--WAITUNTIL(clock'EVENTANDclock=

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- VHDL 源代码 计数器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx