Lyrtech平台用户手册.docx

Lyrtech平台用户手册.docx

- 文档编号:2942205

- 上传时间:2022-11-16

- 格式:DOCX

- 页数:24

- 大小:644.89KB

Lyrtech平台用户手册.docx

《Lyrtech平台用户手册.docx》由会员分享,可在线阅读,更多相关《Lyrtech平台用户手册.docx(24页珍藏版)》请在冰豆网上搜索。

Lyrtech平台用户手册

第1章Lyrtech平台简介

Lyrtech系统是基于DSP和FPGA的高性能的算法仿真验证平台,平台具有通用性、灵活性可扩展性等特点,软件开发流程则与MATLAB\Simulink高效仿真工具集成,利用自动代码生成工具进行软硬件实现。

此文档的目的是简要说明各个模块的作用及其参数配置,搭建模型过程中常见的错误等。

并以MUSIC算法的仿真实验为例,介绍平台的使用方法。

1.1Lyrtech平台的软件配置

1.1.1Lyrtech平台的软件配置及安装方法

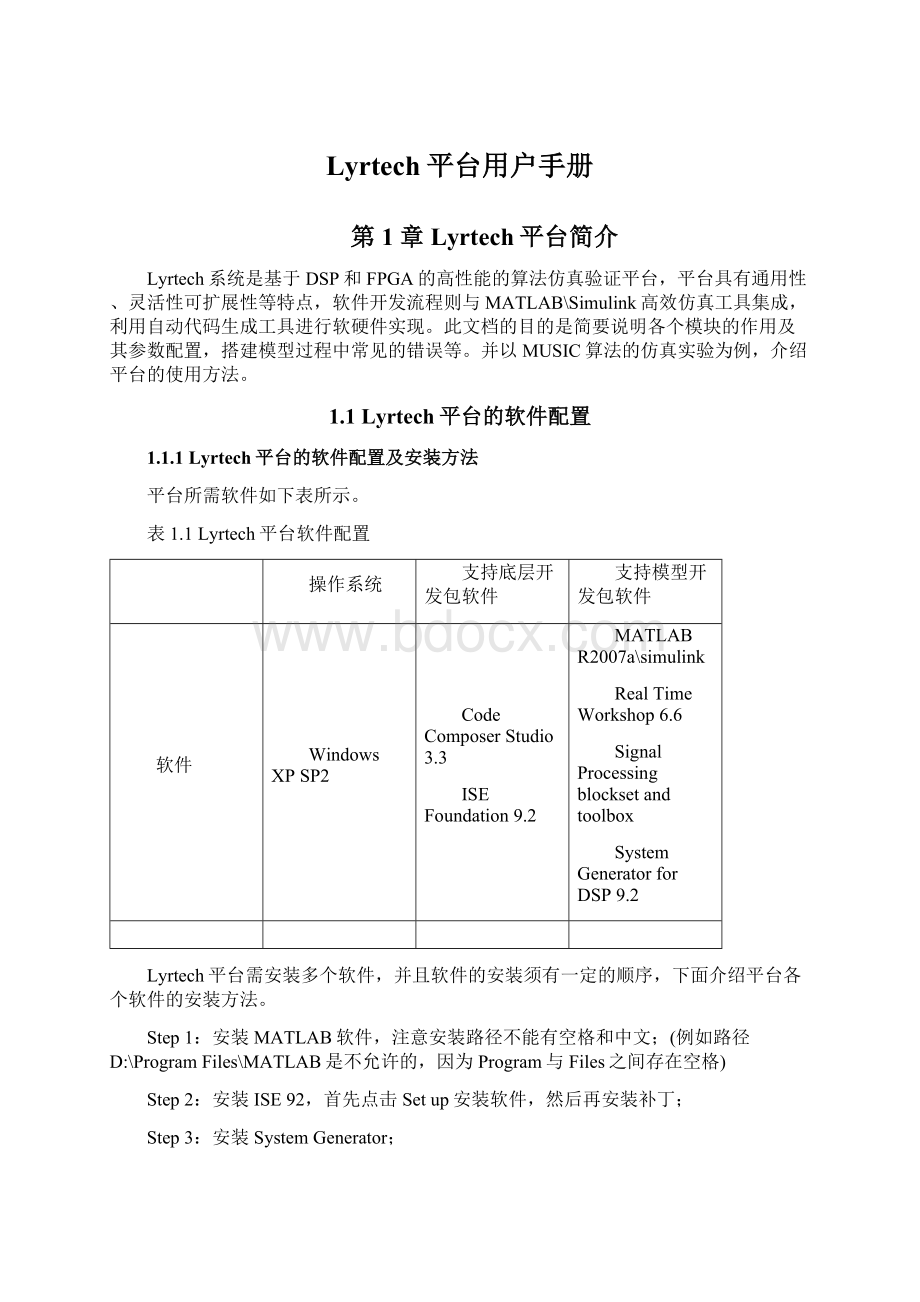

平台所需软件如下表所示。

表1.1Lyrtech平台软件配置

操作系统

支持底层开发包软件

支持模型开发包软件

软件

WindowsXPSP2

CodeComposerStudio3.3

ISEFoundation9.2

MATLABR2007a\simulink

RealTimeWorkshop6.6

SignalProcessingblocksetandtoolbox

SystemGeneratorforDSP9.2

Lyrtech平台需安装多个软件,并且软件的安装须有一定的顺序,下面介绍平台各个软件的安装方法。

Step1:

安装MATLAB软件,注意安装路径不能有空格和中文;(例如路径D:

\ProgramFiles\MATLAB是不允许的,因为Program与Files之间存在空格)

Step2:

安装ISE92,首先点击Setup安装软件,然后再安装补丁;

Step3:

安装SystemGenerator;

Step4:

安装CCS.3.0,安装完成后需设置环境变量。

在安装包中找到CCS中的DOS-run,右键单击DOS-run选择“编辑”,则出现一个窗口(记为窗口1),里面显示了所要设置的环境变量。

在桌面右键单击“我的电脑”选择“属性”,再选择“高级选项”和“环境变量”,此时同样出现一个窗口(记为窗口2)。

如下图所示:

点击“新建(w)”,出现新的窗口,如下图:

窗口1中,“=”号前面的即为变量名,“=”后面的即为变量值,将窗口1中的一个变量名和变量值复制到上图中,然后点击“确定”,这样一个环境变量就设置好了,之后的各个变量设置都是相同的,唯一不同的是在设置变量名为Path的变量时,因为窗口2中已有Path变量,因此将窗口1中的Path变量值复制在原有的Path变量值之后,中间插入一个“;”隔开。

Step5:

安装Lyrtech软件。

1.1.2Xilinx模块简介

Lyrtech平台的模块可以分为3类,分别为Xilinx模块、Lyrtech模块以及Simulink模块。

虽然模块众多,但是常用的模块只有二十到三十个之间。

下面两个章节主要介绍常用模块的功能,以及如何设置模块参数。

本节主要介绍Xilinx模块。

首先介绍多数模块共有参数的意义,以及如何选择参数。

其次再详细介绍各个常用模块的功能和参数。

(1)模型参数的一般选项

由于模块的许多参数都相同或类似,因此首先介绍一些模型共有的参数选项。

a)Precision:

在Xilinx模块里运算可以是任意精度的定点数。

许多模块都允许用户选择精度.缺省情况下模块采用全精度,也就是足够的精度以保证结果无误差.大多数模块也允许用户指定位宽和小数点位置。

一般有Full和Userdefined两种选择。

b)Outputtype:

定义输出数据类型,可以是Signed(2’scomp)和Unsigned两种。

c)Numberofbits:

定点数是通过制定其位宽,小数点位置,数据类型来制定的,最大可支持4096位宽。

d)Binarypoint:

指定小数点右边的位宽。

e)OverflowandQuantization:

当用户自定义精度的时候,可能会出现量化和溢出错误。

溢出是数据超过了可表示的范围,量化是小数部分不到足够的精度。

一般此项取默认选项。

f)ProvideEnablePort:

可以为模块增加一个en针脚,当该信号有效的时候模块保持现在的状态,驱动他的信号必须为Bool型。

g)SamplePeriod:

一般设置为1。

(2)SystemGenerator模块

SystemGenerator模块如图所示,它对整个系统和仿真参数进行控制,并用于激活代码生成,一个带有System模块的Simulink模型必须带有这1个SystemGenerator模块。

模块参数配置如下表

Compilation

选择板卡类型

Part

选择FGGA型号,本设备FPGA为LX160

Targetdirectory

填入生成Bitstream文件的存放路径

Hardwaredescriptionlanguage

选择HDL语言,可选VHDL或者Verilog

FPGAclockperiod

一般取10,如果系统复杂可适当提高

其他

默认值

(3)AddSub模块

模块如图所示,该模块用于加法或减法运算。

(4)Reinterpret模块

Reinterpret模块强制输出一个新类型,其保持输入数据各个位上的值不变,而只移动小数点的位置。

因此其作用是把数据扩大

倍(

为小数点移动的位数,左移为负,右移为正)。

(5)Convert模块

该模块的作用是该模块将输入的采样值转化为期望的数据类型。

(6)Constant模块

该模块用于产生一个常数,可以设定为定点数,布尔数。

(7)Counter模块

此模块提供自由计数或是有限制的向上、向下或向上/向下型的计数。

计数器的输出是一个有符号或者无符号的定点数。

(8)Inverter模块

此模块计算一个定点数的位逻辑补,即逻辑取反。

(9)Delay模块

该模块提供固定周期的延迟,此模块主要用于电路其他部分的匹配流水线延迟。

其与寄存器的区别是,寄存器模块允许只有一个周期的延迟,并包含初始值参数,而此模块支持确定的延迟但没有初始值。

运行延迟时,需启用AddressableshiftRegister模块,且延迟必须为整数倍的周期。

(10)Slice模块

此模块用于分割所输入的数据,并创建新的数值。

作为输出模块用,此模块在输入数据的宽度或二进制点位置变化时才有效。

(11)Mux模块

多路复用模块,它有一个选择输入和一个用户配置的数据总线输入,变化范围是2-1024。

(12)Mult模块

该模块实现乘积功能,计算输入端口两数据的乘积在输出端口输出。

(13)CMult模块

实现增益运算,输出

输入

常数值。

此常数值可以是一个值为常数的MATLAB表达式。

(14)Logical模块

此模块用于执行2-4个定点数的逻辑运算。

(15)Mcode模块

此模块是执行Simulink中用户自定义的MATLAB函数的一个容器。

此模块有三个主要的编码原则:

第一,所有的输入/输出必须是Xilinx定点类型;第二,此模块至少有一个输出;第三,此模块中的代码必须存在于MATLAB路径,或在同一目录下

(16)SineCosine模块

用于计算正弦或余弦,输入值由下式定义:

其中,

为输入数据的位宽。

(17)FIRCompilerv3.0模块

基于FIR滤波器来实现高速

(18)FDATool模块

此模块提供了FDATool软件的借口,并作为MATLAB信号处理工具的一部分。

在定义滤波器时需要把此模块放入要定义的子系统中。

(19)DDSv5.0

此模块是一个直接数字频率合成器,通常也成为数控振荡器(NCO)。

它用查表来产生正弦波。

其相位控制字和频率控制字有下式定义:

其中,

为想要得的正弦波的相位(单位

),

为频率(单位

),

为输入控制字的位宽。

DDS模块参数配置页面如下所示,这里Basic一栏里的参数很容易理解,故只介绍后两部分的参数配置,参数设置如下表所示

Spuriousfreedynamicrange(dB)

80

Frequencyresolution(Hz)

0.04

Memorytype

BlockRAM

其他

默认值

(20)Gatewayout、Gatewayin模块

这两个模块分别将定点型数据转化成浮点型、浮点型转化为定点型。

1.1.3Lyrtech模块简介

Lyrtech模块参数设置的思路是一致的,因此这里只介绍常用模块的功能。

首先介绍DSP中的Lyrtech模块。

(1)DSPboardconfiguration模块

该模块是必须具备的。

当用户拖拽这个模块到Simulink模型里时,系统会提示用户是否想要配置模型为Lyrtech默认选项值,选择yes,这会节省大量的配置参数的时间。

此处系统自动将模型尤其是RTW的参数配置好。

(2)Profiler模块

此模块用在Simulink模型中,来计算基带处理板上DSP的负载。

当仿真中如果最高采样时间设为1时,则采样时间为1的每个模块产生代码来执行一个DSP处理循环。

(3)CMDfilegenerator模块

此模块允许根据DSP模型的需要创建自己的命令文件(.cmd)。

该模块与基带处理板上的DSPboardconfiguration连在一起。

(4)Fastbus模块

通过DSP中的32位EMIF总线来发送和接收从FPGA来的数据。

此模块不支持模拟,只有在RTW中才提供有效数据。

(5)Customregister模块

此模块给出从DSP到FPGA自定义寄存器发送或接收方向上的通道。

通过DSP的EMIF总线进行异步数据传输。

因此,此模块只用于从FPGA中发送和接收参数,不适合大量传输。

(6)VHS-DACVirtex-4control、VHS-ADCVirtex-4control模块

此模块的作用是进行远程控制或配置一个或多个VHS-DAC(VHS-ADC)。

它能同时面向和控制1-8个VHS-DAC(VHS-ADC)。

(7)Setbitstream模块

此模块仅用在DSP模型当中。

当连接和锁定一个板时,此模块用来定义比特流下载。

它没有I/O端口。

下面介绍FPGA上的Lyrtech模块

(1)FPGAboardconfiguration模块

该模块指示SystemGenerator按照Lyrtech的编译流程进行编译。

(2)Customregister模块

此模块可以访问16位内存映射寄存器。

每个寄存器可读可写,并由DSP控制,此模块只用在FPGA中

(3)Fastbus模块

FPGA中的Fastbus模块通过DSP的32位EMIF总线从DSP中发送和接收数据,此模块仅用于FPGA中。

(4)FPGASDRAMRecord模块

用此模块为FPGA中的SDRAM写入大量连续数据。

此模块仅用来记录数据,若想从主机设备上传接收数据,需要有外部设备

(5)Rapidchannel模块

此模块用于两个FPGA之间的数据传送,且仅用于FPGA中。

传送数据遵循两个原则,第一是接收采用发送的设计时钟,则认为是同步传送;第二是接收采用不同的时钟,则认为是异步传送。

(6)Logviewer模块

用在FPGA中,用来检测编译过程中产生的文件。

(7)DAC模块

此模块与DSP用在一起,把数字数据输出到VHS-DAC上进行数模转换。

可设置此模块来提供、触

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Lyrtech 平台 用户手册

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx