数字集成电路设计与分析.docx

数字集成电路设计与分析.docx

- 文档编号:29387067

- 上传时间:2023-07-22

- 格式:DOCX

- 页数:23

- 大小:345.29KB

数字集成电路设计与分析.docx

《数字集成电路设计与分析.docx》由会员分享,可在线阅读,更多相关《数字集成电路设计与分析.docx(23页珍藏版)》请在冰豆网上搜索。

数字集成电路设计与分析

问答:

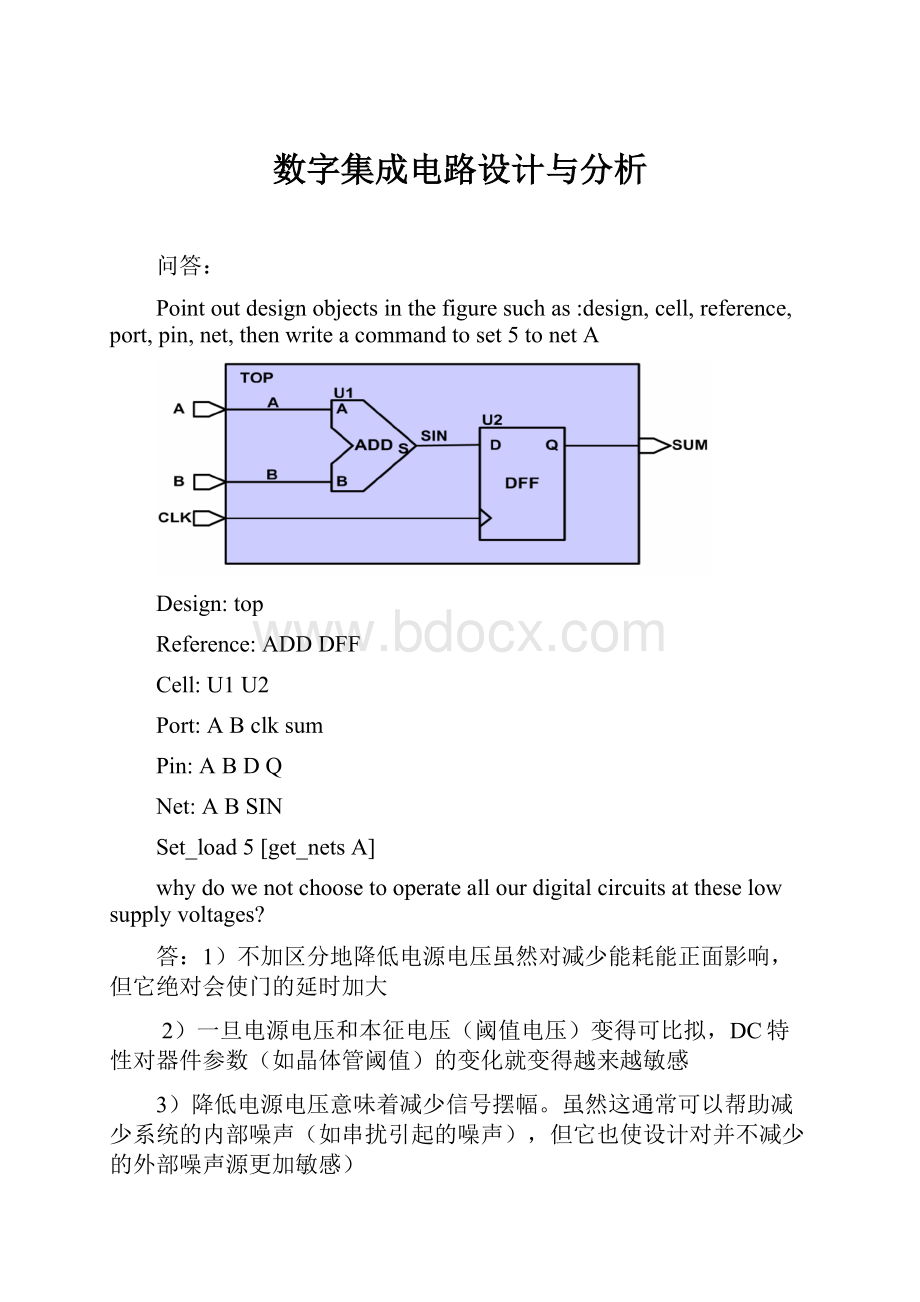

Pointoutdesignobjectsinthefiguresuchas:

design,cell,reference,port,pin,net,thenwriteacommandtoset5tonetA

Design:

top

Reference:

ADDDFF

Cell:

U1U2

Port:

ABclksum

Pin:

ABDQ

Net:

ABSIN

Set_load5[get_netsA]

whydowenotchoosetooperateallourdigitalcircuitsattheselowsupplyvoltages?

答:

1)不加区分地降低电源电压虽然对减少能耗能正面影响,但它绝对会使门的延时加大

2)一旦电源电压和本征电压(阈值电压)变得可比拟,DC特性对器件参数(如晶体管阈值)的变化就变得越来越敏感

3)降低电源电压意味着减少信号摆幅。

虽然这通常可以帮助减少系统的内部噪声(如串扰引起的噪声),但它也使设计对并不减少的外部噪声源更加敏感)

问道题:

1.CMOS静态电路中,上拉网络为什么用PMOS,下拉网络为什么用NMOS管

2.什么是亚阈值电流,当减少VT时,VGS=0时的亚阈值电流是增加还是减少?

3.什么是速度饱和效应

4.CMOS电压越低,功耗就越少?

是不是数字电路电源电压越低越好,为什么?

5.如何减少门的传输延迟?

P203

6.CMOS电路中有哪些类型的功耗?

7.什么是衬垫偏置效应。

8.gate-to-channelcapacitanceCGC,包括哪些部分

VirSim有哪几类窗口

3-6.GiventhedatainTable0.1forashortchannelNMOStransistorwith

VDSAT=0.6Vandk′=100µA/V2,calculateVT0,γ,λ,2|φf|,andW/L:

解答:

对于短沟道器件:

在选择公式的时候,首先要确定工作区域,表格中的所有VDS均大于VDSAT,所以不可能工作在线性区域。

如果工作在饱和区域则:

VT应该满足:

VGS-VT 2-VT<0.61.4 这是不可能的,所以可以假设所有的数据都是工作在速度饱和区域 所以: 由1&2 ( )所以1,2,3是在速度饱和区 由2&3 由2&41297/1146=[(2-Vt0)x0.6-o.62/2]/[(2-Vt)x0.6-0.62/2] Vt=0.587V 由2&5Vt=0.691V 这两个值都满足Vt<1.4,所以表中的数据都是工作的速度饱和状态 由4&5和 可以计算出 和 得到W/L=1.5 3-7GivenTable0.2,thegoalistoderivetheimportantdeviceparametersfrom thesedatapoints.Asthemeasuredtransistorisprocessedinadeep-submcirontechnology,the‘unifiedmodel’holds.Fromthematerialconstants,wealsocoulddeterminethatthesaturationvoltageVDSATequals-1V.Youmayalsoassumethat -2ΦF=-0.6V. NOTE: TheparametervaluesonTable3.3doNOTholdforthisproblem. a.IsthemeasuredtransistoraPMOSoranNMOSdevice? Explainyouranswer. b.DeterminethevalueofVT0. c.Determineγ. d.Determineλ. e.Giventheobtainedanswers,determineforeachofthemeasurementstheoperationregionofthetransistor(choosefromcutoff,resistive,saturated,andvelocitysaturated).Annotate yourfindingintheright-mostcolumnoftheabove. 解答: a)这是PMOS器件 b) 比较各表中 的值知道1,4为工作在速度饱和状态 由1&4 Vt0=0.5V c)由1&5和上面求出的Vt0的值: 1,5工作在速度饱和区域则: (-84.375)/(-72.0)=[(-2.5-Vt0)*(-1)-12/2]/[(-2.5-Vt)*(-1)-12/2] 求出Vt,代入下面公式: 求出: γ=0.538V1/2 d)由1&6,因为1,6均工作在速度饱和区域: λ=0.05V-1 e)1-vel.Sat,2-cutoff,3-saturation,4-5-6vel.Sat,7-linear 3-8AnNMOSdeviceispluggedintothetestconfigurationshownbelowinFigure 0.4.TheinputVin=2V.Thecurrentsourcedrawsaconstantcurrentof50µA.Risavariable resistorthatcanassumevaluesbetween10kΩand30kΩ.TransistorM1experiences shortchanneleffectsandhasfollowingtransistorparameters: k’=110*10-6V/A2,VT=0.4, andVDSAT=0.6V.ThetransistorhasaW/L=2.5µ/0.25µ.Forsimplicitybodyeffectand channellengthmodulationcanbeneglected.i.eλ=0,γ=0.. a.WhenR=10kΩfindtheoperationregion,VDandVS. b.WhenR=30kΩagaindeterminetheoperationregionVD,VS c.ForthecaseofR=10kΩ,wouldVSincreaseordecreaseifλ≠0.Explainqualitatively 解答: 1)当R=10k,VD=VDD-IR VD=2.5-50x10-6x104=2.5-0.5=2V 假设器件工作在饱和区(需要以后验证)则: =0.3V所以VGS=0.3+0.4=0.7V VS=2-0.7=1.3V Vmin=min(VGS-Vt,VDSAT,VDS)=min(0.3,0.6,0.7)=VGS-Vt所以是饱和区 VD=2V VS=1.3Vsaturationoperation b)VD=2.5-30x103x50x10-6=2.5-1.5=1V assumelinearop: Min(VGS-VT,VDS,VDSAT)=min((1-0.93-0.4).0.07,0)=VDSSOlinear c)increase,R=10kΩ R变化,则VD必须变化以保持电流稳定, 试图增加电流,而为了恒定电流值,VGS必须减小,即VS必须增加 1、(10)P137 Assumeaninverterinthegeneric0.25mmCMOStechnologydesignedwithaPMOS/NMOSratioof3.4andwiththeNMOStransistorminimumsize(W=0.375mm,L=0.25mm,W/L=1.5).VM=1.25V,pleasecomputeVIL,VIH,NML,NMH.theprocessparametersispresentedintable1 由此可以得到VIL,VIH,NML,NMH: 因为VIH=VM-VM/g,VIL=VM+(VDD-VM)/g NMH=VDD-VIH,NML=VIL VIL=1.2V,VIH=1.3V,NML=NMH=1.2 5.3、FortheinverterofFigure1andanoutputloadof3pF,atVout=2.5V,IDVsat=0.439mA,atVout=1.25V,IDvsat=0.41mA fig1 a.Calculatetplh,tphl,andtp. b.Aretherisingandfallingdelaysequal? Whyorwhynot? 解答: tpLH=0.69RLCL=155nsec. 对于tpHL: 首先计算RonforVoutat2.5Vand1.25V. 因为Vout=2.5V,IDVsat=0.439mA所以Ron=5695 当Vout=1.25V,IDvsat=0.41m所以Ron=3049. 这样,Vout=2.5VandVout=1.25V之间的平均电阻Raverage=4.372k. tpLH=0.69RaverageCL=9.05nsec. tp=av{tpLH,tpHL}=82.0nsec b.Aretherisingandfallingdelaysequal? Whyorwhynot? Solution tpLH>>tpHL因为RL=75k远大于有效线性电阻effectivelinearizedon-resistanceofM1. 5-5ThenextfigureshowstwoimplementationsofMOSinverters.Thefirstinverterusesonly NMOStransistors.CalculateVOH,VOL,VMforeachcase.有的参数参考表1 解答: 电路A. VOH: 当M1关掉,M2的阈值是: 当下面条件满足的时候,M2将关闭: 所以VOUT=VOH=1.765V VOL: 假设VIN=VDD=2.5V. 我们期望VOUT为低,因此我们可以假设M2工作在速度饱和区,而M1工作在线性区域. 因为ID1=ID2,所以VOUT=VOL=0.263V,假设成立 VM: 当VM=VIN=VOUT. 假设两晶体管均工作在速度饱和区域,我们得到下面两个方程: 设ID1=ID2,得到VM=1.269V 电路B. 当VIN=0V,NMOS关掉,PMOS打开,并把VOUT拉到VDD,soVOH=2.5.同样,当VIN=2.5V,thePMOS关掉,NMOS把VOUT拉到地,所以VOL=0V. 为了计算VM: VM=VIN=VOUT. 假设两晶体管均工作在速度饱和区域,可以得到下面两组方程. 设ID3+ID2=0,可以得到rVM=1.095V. 所以假设两晶体管均工作在速度饱和区域是正确的. 5-7ConsiderthecircuitinFigure5.5.DeviceM1isastandardNMOSdevice.DeviceM2hasall thesamepropertiesasM1,exceptthatitsdevicethresholdvoltageisnegativeandhasavalue of-0.4V.Assumethatallthecurrentequationsandinequalityequations(todeterminethe modeofoperation)forthedepletiondeviceM2arethesameasaregularNMOS.Assumethat theinputINhasa0Vto2.5Vswing.(VDSAT=0.63v) a.DeviceM2hasitsgateterminalconnectedtoitssourceterminal.IfVIN=0V,whatisthe outputvoltage? Insteadystate,whatisthemodeofoperationofdeviceM2forthisinput? b.ComputetheoutputvoltageforVIN=2.5V.YoumayassumethatVOUTissmalltosimplify yourcalculation.Insteadystate,whatisthemodeofoperationofdeviceM2forthis input? 解答a 当VIN=0V,M1则关掉.M2开,因为VGS=0>VTn2.所以没有电流通过M2,M2的源漏电压等于0,故M2工作在线性区域,所以VOUT=2.5V. Solutionb 假设M1工作在线性区域,M2工作在速度饱和区域,这就意味: 因为Vout很小,所以可以忽略V2out/2,所以可以得到 因此我们的假设是合理的。 5-15Sizingachainofinverters. a.Inordertodrivealargecapacitance(CL=20pF)fromaminimumsizegate(withinput capacitanceCi=10fF),youdecidetointroduceatwo-stagedbufferasshowninFigure ,Assumethatthepropagationdelayofaminimumsizeinverteris70ps.Alsoassume thattheinputcapacitanceofagateisproportionaltoitssize.Determinethesizingofthe twoadditionalbufferstagesthatwillminimizethepropagationdelay. b.Ifyoucouldaddanynumberofstagestoachievetheminimumdelay,howmanystages wouldyouinsert? Whatisthepropagationdelayinthiscase? 解答a: 当每个buffer的延迟相等的时候,可以得到最小延迟时间.此时每个buffer的尺寸系数分别为f,f2 解答b: 最小延迟时间发生在f=e的时候,因此 6-1Implementtheequation usingcomplementaryCMOS.SizethedevicessothattheoutputresistanceisthesameasthatofaninverterwithanNMOSW/L=2andPMOSW/L=6.Whichinputpattern(s)wouldgivetheworstandbestequivalentpull-uporpull-downresistance? 解答: 因为 最坏的上拉电阻发生在,只有一个通路存在outputnodetoVdd. 如: ABCDEFG=1111100and0101110. 最好的上拉电阻发生在: ABCDEFG=0000000. 最坏的下拉电阻发生在,只有一个通路存在outputnodetoGND. 如: ABCDEFG=0000001and0011110. 最好的下拉电阻发生在: ABCDEFG=1111111. 5章 Assumeaninverterinthegeneric0.25mCMOStechnologydesignedwithaPMOS/NMOSratioof3.4andwiththeNMOStransistorminimumsize(W=0.375mm,L=0.25mm,W/L=1.5).PleasecomputeVIL,VIH,NML,NMH theprocessparametersispresentedintable1 解: 我们首先计算在VM(=1.25V)的增益 所以: VIL=1.2V,VIH=1.3V,NML=NMH=1.2 1.Howtodeducethatthepropagationdelayofagate? p203 ☐Keepcapacitances(CL)small ☐Increasetransistorsizes(W/L) ☐IncreaseVDD(seefigure5.22) 减小CL: 增加晶体管的W/L,提高VDD 2.DeterminethesizesoftheinvertersinthecircuitofFigure5.22,suchthatthedelaybetweennodesOutandInisminimized.YoumayassumethatCL=64Cg,1 P210 Figure5.22, 3.ForthecircuitofFigure4.11,assumethatadriverwithasourceresistanceof isusedtodrivea10cmlong,1mmwideAl1wire.Andassumethatthetotallumpedcapacitanceforthiswireequals11pF.Whenapplyingastepinput(withVingoingfrom0tov),pleasecomputethepropagationdelayofthecircuit.P151 Figure4.11 解答: 4pleaseanalyzeintrinsiccapacitancesofMOSFETtransistor,writeoutthreesourcesofit,anddrawoutMOSFETtransistorcapacitancemodel.P112 答: 基本的MOS结构,沟道电荷以及漏和源反向偏置pn结的耗尽区。 电容器件模型如下: 5.pleasewriteouttheexpressionofequivalentresistanceReqofthecircuitinFigure1when(dis)chargingacapacitor.AssumingthatthesupplyvoltageVDDissubstantiallygreaterthanthevelocity-saturationvoltageVDSATofthetransistor.thechannel-lengthmodulationfactor( )cannotbeignoredinthisanalysis, areknownparameters.P105 解答: Program 1.pleasewriteoutverilogcodeandtestbenchfora4bitup-counter Modulecounter(clk,reset,enable,count); Inputclk,reset,enable; Output[3: 0]count; Reg[3: 0]count; Always@(posedgeclk) If(reset==1’b1) Count<=0; Elseif(enable==1’b1) Count<=count+1; Endmodule Modulecounter_tb; Regclk,reset,enable; Wire[3: 0]count; CounterU0(clk,reset,enable,count); Initial Begin Clk=0; Reset=0; Enable=0; End Always #5clk=! clk; initial begin $monitor($time,,,“clk=%dreset=%denable=%dcount=%d”,clk,reset,enable,count); #100$finish end endmodule 2.pleasewriteoutverilogcodeandtestbenchforabitfulladder Moduleaddbit(a,b,ci,sum,co); Inputa,b,ci; Outputsum.co; Wirea,b,ci,sum,co; Assign{co,sum}=a+b+ci ; Endmodu

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 集成电路设计 分析

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx