可靠性仿真典型案例模拟.docx

可靠性仿真典型案例模拟.docx

- 文档编号:2932984

- 上传时间:2022-11-16

- 格式:DOCX

- 页数:32

- 大小:1.53MB

可靠性仿真典型案例模拟.docx

《可靠性仿真典型案例模拟.docx》由会员分享,可在线阅读,更多相关《可靠性仿真典型案例模拟.docx(32页珍藏版)》请在冰豆网上搜索。

可靠性仿真典型案例模拟

一、模拟电路的仿真案例

1.整体电路功能说明

过流检测电路用于监视电路工作电流的大小,当电路负载上的电流超过某一数值,电路会给出报警信号。

检测电流可以在流入负载一侧取样,也可以在流出负载一侧取样,这两种检测方法可以分别称为高端和低端电流检测。

它们都是通过取样电阻采样电流然后通过电压放大器放大,都要求放大器有较高的输入阻抗、放大倍数线性度和一定的共模范围。

以下时一个可能的应用场景,0.1欧姆的电阻串接在1.8V电源和负载之间,一个仪表放大器将0.1欧姆电阻上的电压放大100倍(实际略低)后输入给运放的正相输入端,带隙电路产生的基准电压输入给运放的反相输入端,3.3V的电源给仪表放大器、基准和运算放大器供电,其中仪表放大器是由三个运算放大器组成的。

该电路一共由4个运算放大器模块和1个带隙基准模块组成,电路元件总数超过300个。

1.8V电源上的负载电流超过某一个设定值,运算放大器会输出一个高电平的报警信号。

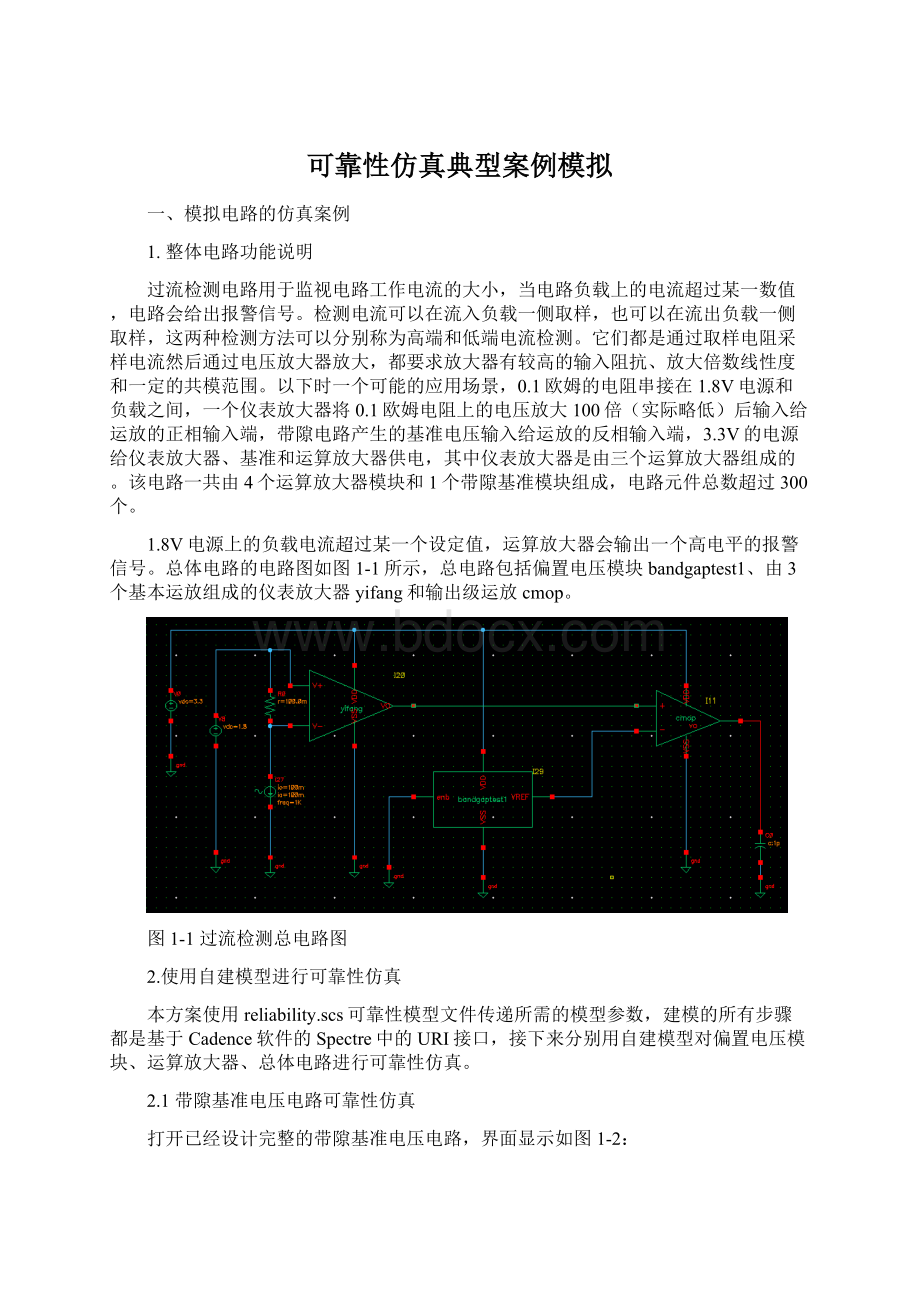

总体电路的电路图如图1-1所示,总电路包括偏置电压模块bandgaptest1、由3个基本运放组成的仪表放大器yifang和输出级运放cmop。

图1-1过流检测总电路图

2.使用自建模型进行可靠性仿真

本方案使用reliability.scs可靠性模型文件传递所需的模型参数,建模的所有步骤都是基于Cadence软件的Spectre中的URI接口,接下来分别用自建模型对偏置电压模块、运算放大器、总体电路进行可靠性仿真。

2.1带隙基准电压电路可靠性仿真

打开已经设计完整的带隙基准电压电路,界面显示如图1-2:

图1-2带隙基准电压源电路图

图1-3等效电路结构图(a)

图1-4等效电路结构图(b)

图1-2是详细电路图,该电路是一个带隙基准结构。

带隙基准的工作原理是根据硅材料的带隙电压与电压和温度无关的特性,利用△VBE的正温度系数与双极型晶体管VBE的负温度系数相互抵消,实现低温漂、高精度的基准电压。

双极型晶体管提供发射极偏压VBE;由两个晶体管之间的△VBE产生VT,通过电阻网络将VT放大α倍;最后将两个电压相加,即VREF=VBE+αVT,适当选择放大倍数α,使两个电压的温度漂移相互抵消,从而可以得到在某一温度下为零温度系数的电压基准。

图1-3是电流源产生电路,充当图1-4中的恒流源。

接下来进行该带隙基准电路的可靠性仿真。

点击Launch菜单下ADEL选项,如图1-5所示,进入仿真设置界面。

图1-5打开设置界面的步骤

如图1-6所示,是Candence的仿真设置界面

图1-6仿真设置界面

点击图1-6中标注有数字“1”的红色框中的按钮,进行分析模式的选择,选择瞬态分析模式,具体配置如图1-7所示,配置完成后点击OK按钮。

再次点击图1-6标记为“1”的按钮进行分析模式选择,选择dc分析模式,具体配置如图1-8所示,配置完成后点击OK按钮,则在此次仿真中同时进行瞬态仿真和dc仿真。

图1-7添加tran(瞬态)仿真分析模式

图1-8添加dc仿真分析模式

点击图1-6中红色方框中标注有数字“2”的按钮,进行输出波形的信号来源选择,点击该按钮后会弹出图1-9所示的选择对话框,点击“FromSchematic”按钮,便可以直接从电路图中选择需要输出波形的信号。

此处由于我们仅需要观察基准电压Vref的情况,因此仅选择Vref的电压输出波形。

图1-9输出波形信息设置界面

如图1-10所示,点击菜单栏中的Setup菜单中的ModelLibraries选项,进行模型库的选择,点击该选项后,会弹出如图1-11所示的界面,可在该界面中选择模型库。

图1-10选择模型库菜单

图1-11选择模型库界面

点击图1-11中的红色浏览按钮,在/models路径下选择可靠性仿真需要的仿真模型文件,在此处由于是进行自建模型的可靠性仿真,因此选择reliablility.scs文件,选好后的界面如图1-12所示。

图1-12选择好自建模型文件后的界面

点击菜单栏中的Simulation->Reliability->Setup选项,进行可靠性仿真的相关参数设置,点击该选项后会出现如图1-13所示的配置页面。

图1-13可靠性仿真相关参数设置界面

在图1-13中,仅需要配置Basic选项里的内容,各项配置可参照图1-13中配置,在这里仅对红色方框中的内容作简要说明,方框1的内容是选择老化时间,此处是选择仿真老化10年后的结果;方框2是选择性能损耗比,这里设置是损耗10%,则仿真工具会计算该电路各个器件性能损耗10%需要的时间;方框3是选择可靠性仿真接口库文件,由于这里是使用URI自建模型,需要选择接口库文件,点击浏览按钮选择“libURI.so”(若使用的是Cadence自带HCI模型,则不需要进行方框3中的选项的配置)。

最后点击“OK”按钮保存配置。

点击图1-6中的标注有数字“3”的红色方框中的按钮,开始进行可靠性仿真。

此次可靠性仿真仅考虑MOS管的损耗因素,忽略BJT管的损耗因素。

图1-14是关键MOS管部分电路的截图,该电路中的MOS的管参数(主要是宽度和长度)是进行可靠性仿真之前的参数。

图1-14可靠性仿真关键MOS管

图1-15是进行可靠性仿真的仿真图,红色线表示该电路工作时间为0时,电源从0v到7v变化,基准电压的曲线;黄色曲线表示该电路工作时间为10年时,电源从0v到7v变化,基准电压的曲线。

不难看出,当此电路工作了10年后,电路性能已明显下降,这是MOS管老化过快的结果。

图1-15可靠性仿真基准电压曲线图

为了找到老化过快的原因,需要打开可靠性仿真时的相关数据分析,如图1-16所示,点击菜单栏Result->ReliabilityData->Results,会弹出如图1-17所示的对话框。

图1-16打开可靠性仿真数据分析界面的步骤1

图1-17打开可靠性仿真数据分析的步骤2

点击图1-17中红色方框内的按钮,就可以看到可靠性仿真的相关数据分析。

如图1-18所示

图1-18可靠性仿真相关数据

可以看到MOS管PM1和PM2的寿命非常短,红色圈里是该两个MOS管性能损耗10%所需要的时间。

因此可以看出正是这两个管子损耗非常快,才导致整个电路老化较快,因此需要作出相应修改已解决此问题。

MOS管的老化主要受管子宽度W、管子长度L和源漏电压Vds影响,W和L越大,损耗速度越慢;Vds越大,损耗速度越快。

由于修改Vds对电路的状态影响过大,一般不考虑此解决方法,而同比例增加W和L,一般情况下对电路状态的影响很小,因此采用同比例增大W和L的方法来减小电路的老化速度。

在图1-14中,PM0、PM1、PM2和宽度W和长度L分为20um、1um,接下来将宽度和长度同时增大为原来的5倍,即W=100um,L=5um,修改后的MOS管参数如图1-19所示。

图1-19修改W、L后的关键MOS管

图1-20是增大MOS管的宽度和长度后,进行可靠性仿真的仿真图,红色线表示该电路工作时间为0时,电源从0v到7v变化,基准电压的曲线;黄色曲线表示该电路工作时间为10年时,电源从0v到7v变化,基准电压的曲线。

可以看到该电路工作10年后,电路性能变化较小,这表明通过增大MOS管宽度和长度以降低电路老化速度的方法是可行的。

图1-20修改W、L后进行可靠性仿真的输出波形

打开可靠性数据分析页面,如图1-21所示,可以看到PM1和PM2的性能降低10%的时间已经明显延长,将PM1和PM2的宽度和长度同比例增大5倍后,其性能降低10%所需要的时间分别从7.05x10-3年变为12.5年、3.82x10-3年变为6.74年,增长了3个数量级,通过同比例增大MOS管的宽度和长度的效果非常明显。

图1-21修改W、L后的可靠性仿真相关数据

2.2运算放大器部分可靠性仿真

运算放大器是模拟电路里的重要模块,可以构成许多有用的电路,典型的运算放大器由两级组成,第一级是差分输入级,将输入的差分电压转换为电流信号,第二级则是单端输出级,负责将电流信号再转换回单端的输出电压。

运算放大器内部一般需要进行补偿,以保证运算放大器在负反馈电路中不出现振荡。

图1-22是单个基本运算放大器的内部详细的电路图,它的输入端由PMOS和NMOS差分对并联构成,这样可以保证输入电压范围轨到轨,之后是一个电流求和电路,最后是AB类的输出电路。

图1-22运算放大器内部详细电路图

图1-23为运算放大器仿真时的外部电路,对它进行dc、ac、tran三种仿真。

重点观察ac仿真结果,查看运放的相位裕度和增益带宽积。

在可靠性仿真中设置的agingtime是半年。

图1-23运算放大器仿真电路

打开运算放大器的电路图,按照第2.1节的相关步骤进行可靠性仿真的设置,这里不再赘述,分析模式设置和输出波形设置如图1-24中红色框1和红色框2中所示。

图1-24分析模式设置和输出波形设置

点击开始仿真按钮,进行仿真,仿真结果见图1-25和图1-26。

图1-25运算放大器进行可靠性仿真的增益

图1-26运算放大器进行可靠性仿真的相位

图1-25是不同频率下的增益,红色代表老化之前的增益,黄色代表老化之后的增益。

图1-26是不同频率下的相位,红色代表老化之前的相位,黄色代表老化之后的相位。

通过图1-25和1-26可以看出,老化之前,运放单位增益带宽为231MHz,相位裕度为76度,老化半年后相位裕度变为36度,单位增益带宽只有93MHz。

打开可靠性数据分析页面,如图1-27所示

图1-27运算放大器的可靠性性仿真相关数据

查看电路中NMOS和PMOS器件的寿命和衰减情况,可以看出不同MOS管间寿命差异很大,主要的影响因素是不同MOS管的漏源电压Vds不同。

由于漏源电压出现在模型公式的指数项里,所以只要漏源电压稍有不同,器件阈值电压的变化就会有很大不同。

在给出的结果中,可以看到M2、M3、M6、M7、M13的寿命非常短(不足一个月),其中M3的寿命最短,只有0.0228年。

这5个MOS管都在偏置电路里,具体位置见图1-26,它们所在电源到地的支路上只有2~3个MOS管,就是说只有2~3个MOS管的漏源共同承担3.3V的电源电压,这5个MOS管的漏源电压均大于2V,所以它们的寿命都特别短。

图1-28寿命较短的MOS管在电路图中的位置

这5个MOS管都处在电流偏置电路里,考虑老化之后,它们的阈值电压升高了20%~40%,导致偏置电路给出的偏置电流偏小,在老化前β倍增电路产生的偏置电流为21.8uA,老化之后偏置电流只有6.4uA,电路的其它偏置电流都是有这个电流成比例复制产生的,所以阈值电压增大导致整个电路的偏置电流减小,速度变慢。

查找图1-28可以看到寿命最短的MOS管为M3,它的寿命只有0.0228年。

如果老化时间设置为0.0228年,则可以保证所有的器件阈值电压变化量在10%。

在Simulation->Reliability->Setup菜单项里修改老化时间,如图1-29所示,

图1-29将老化时间设置为0.0228年的界面

将老化时间设置为0.0228年再进行仿真得到运放的频率响应曲线。

如图1-30,

图1-30修改老化时间后运算放大器的可靠性仿真

可以看到老化后运放的单位增益带宽变为173MHz,相位裕度为72度,相比较老化前单位增益带宽下降较多,但是运放的相位裕度仍大于60度,运放可以稳定工作。

查看运放的偏置电路发现β倍增电路产生的偏置电流为17.2uA,相比于老化前只降低了4.4uA。

2.3总电路可靠性仿真

仿真界面相关设置参考2.1小节,此处不再赘述。

老化前仿真结果见图1-31,假设负载的电流按照正弦的方式变化,峰峰值是200mV。

图

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 可靠性 仿真 典型 案例 模拟

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx