SDRAM控制器课设报告完整.docx

SDRAM控制器课设报告完整.docx

- 文档编号:29074517

- 上传时间:2023-07-20

- 格式:DOCX

- 页数:11

- 大小:1.38MB

SDRAM控制器课设报告完整.docx

《SDRAM控制器课设报告完整.docx》由会员分享,可在线阅读,更多相关《SDRAM控制器课设报告完整.docx(11页珍藏版)》请在冰豆网上搜索。

SDRAM控制器课设报告完整

SDRAM控制器课设报告

<姓名>

北京至芯科技FPGA培训课程

2016年4月30日星期六

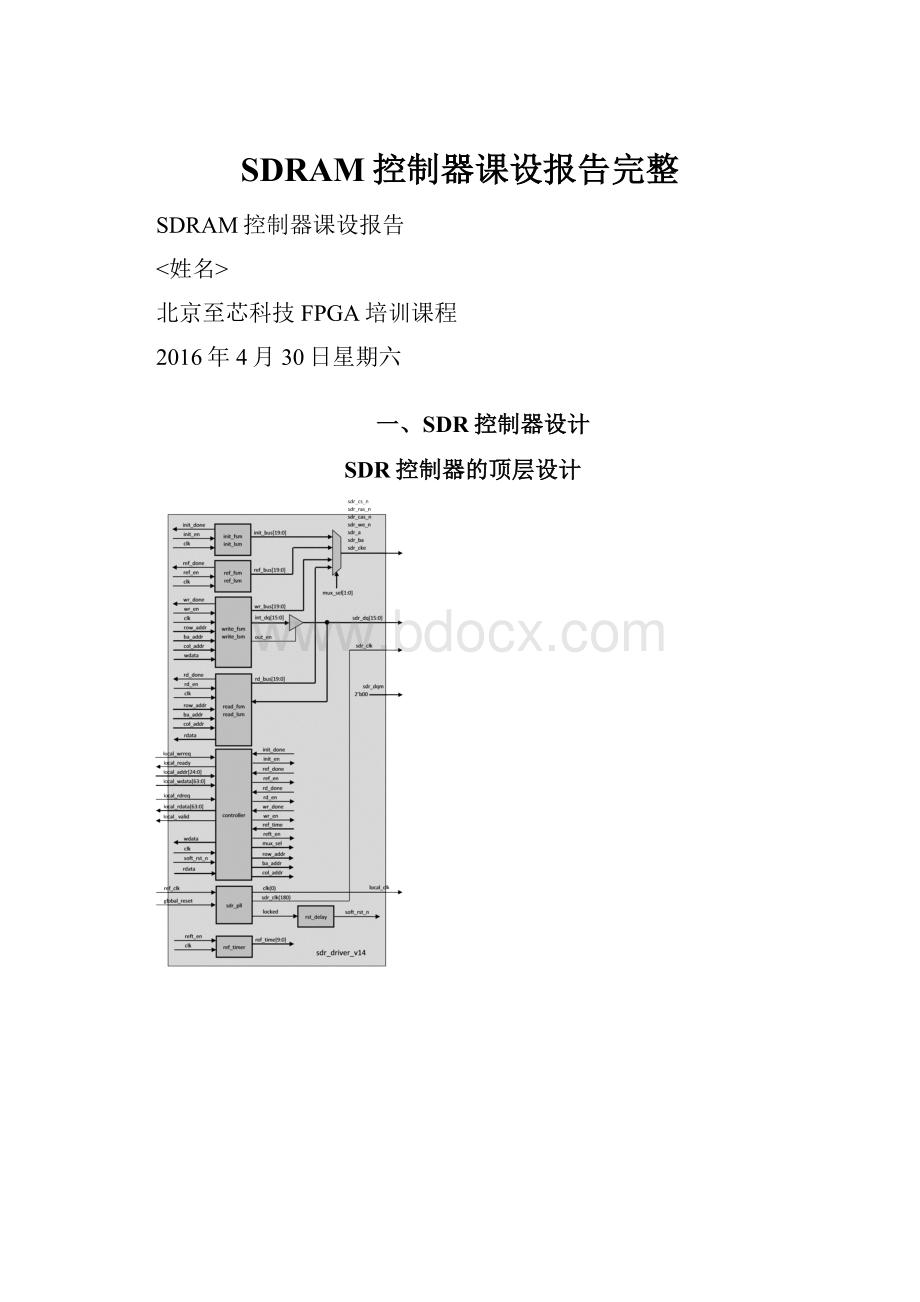

一、SDR控制器设计

SDR控制器的顶层设计

基本需求

顶层框图符号

SDR控制器的上电序列

上电序列的架构设计

上电序列的状态机设计(STG)

SDR控制器的上电和刷新序列

顶层架构

刷新序列模块的状态机设计(STG)

SDR控制器的上电刷新读写序列(完整控制器设计)

顶层设计

说明:

1.突发长度BL=4,本地数据宽度=16*4=64;2.忽略数据写掩码,DQM始终为0

3.全部读写命令均使能AP

顶层接口正常和非正常的写时序:

顶层接口正常和非正常的读时序:

顶层设计

写序列设计

写序列时序:

写序列模块的STG(BL=4):

读序列设计(有跨时钟域问题)

读序列架构:

说明:

1.装配器Fitter的fit_en有效时,将dq_sys装配到rdata,此时,若fit_load=0,则装配到rdata[15:

0],fit_load=1则装配到rdata[31:

16],fit_load=2则装配到rdata[47:

32],fit_load=3则装配到rdata[63:

48]

2.再同步寄存器链的长度为2(SL=2)

读序列时序设计(CL=2,BL=4,SL=2,AP模式,ctRCD=2)

读序列状态机设计:

主控制器设计

STG:

S1部分算法流程图ASMcharts:

二、DDR2控制器设计

编写自己的控制器

顶层设计

说明:

1.突发长度BL=4,本地数据宽度=16*4=64;2.忽略数据写掩码,DQM始终为0

3.全部读写命令均使能AP

顶层架构

使用Altera的IP核(DDR2HPCII,数据块搬运模块例子)

说明(基本需求):

1.使用DDR2HPCII构建的数据搬运模块

2.本地突发长度设置为4(local_size=4)

3.全速运行设置

4.DDR2器件采用16位宽,4Bank,速度667Mbps,存储器时钟333MHz

5.数据搬运尺寸设置为LPM参数DEPTH=512,即512本地字(全速情况下字宽为32)

6.数据搬运模块具有块搬运启动命令start。

start命令启动一次从source至target的搬运

7.数据搬运模块具有块搬运清除命令clear。

clear命令启动一次从target区的清零

数据块搬运模块顶层

数据块搬运模块的状态转移图

三、DDR3控制器设计

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- SDRAM 控制器 报告 完整

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx