基于FPGA的数字CMOS摄像机图像采集精编版.docx

基于FPGA的数字CMOS摄像机图像采集精编版.docx

- 文档编号:28952835

- 上传时间:2023-07-20

- 格式:DOCX

- 页数:32

- 大小:89.90KB

基于FPGA的数字CMOS摄像机图像采集精编版.docx

《基于FPGA的数字CMOS摄像机图像采集精编版.docx》由会员分享,可在线阅读,更多相关《基于FPGA的数字CMOS摄像机图像采集精编版.docx(32页珍藏版)》请在冰豆网上搜索。

基于FPGA的数字CMOS摄像机图像采集精编版

基于FPGA的数字CMOS摄像机图像采集

一、数据采集系统概述

数据采集是指将以各种形式输入的被测信号,包括语音信号、温度信号、湿度信号、图像信号等经过适当处理,成为计算机可以识别的数字信号,从而送入计算机进行存储处理的过程,数据采集卡就是典型的基于数据采集系统原理的集成计算机扩展卡。

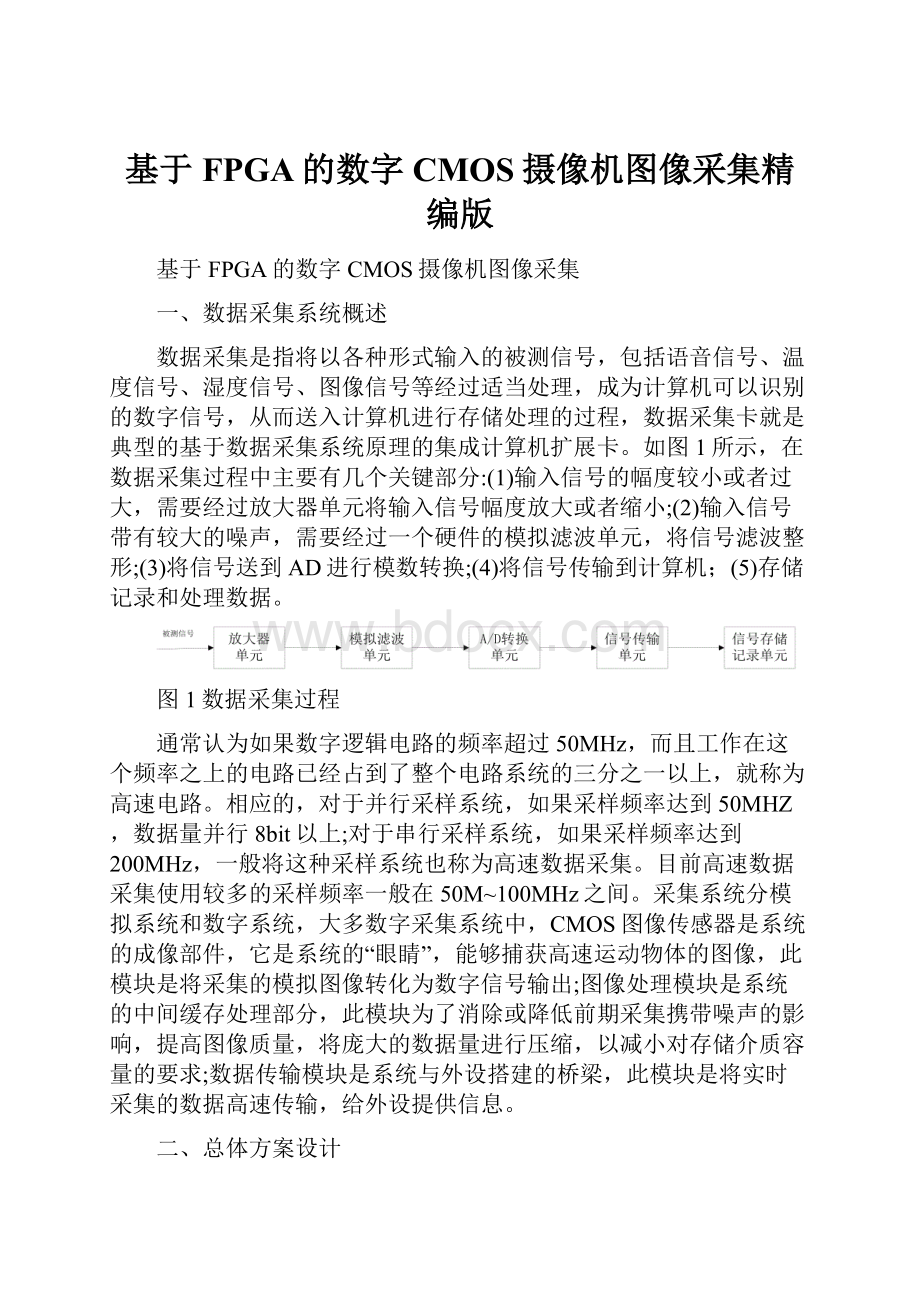

如图1所示,在数据采集过程中主要有几个关键部分:

(1)输入信号的幅度较小或者过大,需要经过放大器单元将输入信号幅度放大或者缩小;

(2)输入信号带有较大的噪声,需要经过一个硬件的模拟滤波单元,将信号滤波整形;(3)将信号送到AD进行模数转换;(4)将信号传输到计算机;(5)存储记录和处理数据。

图1数据采集过程

通常认为如果数字逻辑电路的频率超过50MHz,而且工作在这个频率之上的电路已经占到了整个电路系统的三分之一以上,就称为高速电路。

相应的,对于并行采样系统,如果采样频率达到50MHZ,数据量并行8bit以上;对于串行采样系统,如果采样频率达到200MHz,一般将这种采样系统也称为高速数据采集。

目前高速数据采集使用较多的采样频率一般在50M~100MHz之间。

采集系统分模拟系统和数字系统,大多数字采集系统中,CMOS图像传感器是系统的成像部件,它是系统的“眼睛”,能够捕获高速运动物体的图像,此模块是将采集的模拟图像转化为数字信号输出;图像处理模块是系统的中间缓存处理部分,此模块为了消除或降低前期采集携带噪声的影响,提高图像质量,将庞大的数据量进行压缩,以减小对存储介质容量的要求;数据传输模块是系统与外设搭建的桥梁,此模块是将实时采集的数据高速传输,给外设提供信息。

二、总体方案设计

方案1:

图像数据的传输通过USB总线技术完成系统的初始化以及将最终的传输信号准确无误地传送到上位机上。

USB技术具有简单化、通用性、可靠性、热插拔、传输速率高等优点,

随之带来的是应用USB技术的复杂程度高、总线传输协议需要协调等问题。

方案2:

利用两片SDRAM进行图像数据的短时间存储并快速传输,SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了,这也就大大提高了存储器的访问速度。

其优点是设计相对简单、不许考虑传输时转换总线的问题、较为可靠,缺点是SDRAM容量有限、传输时序需要计算准确、SDRAM经常刷新等。

根据综合分析和考虑,我们选用相对简单方便的方案2,选择器件如下:

FPGA采用Altera的CycloneEP2C35F484C8,视频采集芯片用飞利浦的SAA7113作为A/D转换单元,两块型号为K4S641632E的SDRAM和FPGA构成图像帧存储及传输处理系统,ADV7125是数模转换芯片,和计算机VGA显示器相连作为显示终端,系统整体框图如图2所示。

图2视频监控系统整体框图

以上图像视频监视系统的大部分设计工作都集中在对FPGA的编程开发上,通过分析可以确定出FPGA需要包含如下几个功能模块。

(1)视频接口配置模块:

视频采集芯片SAA7113具有多种采集方式,这里FPGA通过I²C总线对其内部寄存器进行配置,使其按照一定的格式进行采样。

(2)异步FIFO模块:

当FPGA接收A/D采样的视频数据时,由于SAA7113和FPGA一般在不同的时钟频率下,这就会出现通常所说的异步时钟问题,处理不当就容易出现亚稳态,常用方法是在两者之间添加一块异步FIFO。

(3)视频变换模块:

对得到的数字视频流进行解码,识别出行、场同步信号,并且根据需要选择采集图像的大小,进而变换成RGB格式的图像数据,以便于后续显示。

(4)图像帧存读写模块:

将解码后的数据经由一个乒乓机制依次存放在两片RAM中,每个里面刚好存放一幅图像,通过乒乓机制使得两块存储区域交替进行存储输入和显示输出,避免等待,提高速度。

(5)VGA控制模块:

根据VGA的工业参数,产生相应的行同步和场同步信号,并在适当时刻送入数据,经由ADV7125送VGA进行显示。

图3描述了FPGA内部的各个主要功能模块。

系统上电时,FPGA首先从外部Flash中读取配置数据,完成自身的程序加载,进入工作模式状态。

随后I²C配置接口模块完成对SAA7113的初始化,初始化结束后,FPGA等待采集图像的命令。

FPGA收到采集命令后,启动采集视频数据模块、异步FIFO模块和视频解码模块进行解码,将数据轮换写到两个帧存中,经通信模块送出,以上即为该系统的工作流程。

下面主要针对SDRAM控制模块的具体实现过程进行详细分析和介绍。

图3FPGA系统内部各模块整体框图

三、SDRAM控制模块

系统要把每一幅图像数据存储到一个SDRAM里面供后续显示,由于SDRAM整个数据的写入和读出都需要一定的时间,为了避免中间等待过程,采用两片等大的SDRAM交替工作,一片在从FIFO向其写入时另一片向VGA输出,使用乒乓机制交换它们的工作性质。

这样问题的重点就集中在FPGA对SDRAM的读写控制模块上。

3.1SDRAM概述

之所以要用到SDRAM,是因为它价格低、体积小、速度快、容量大,是比较理想的存储器件。

在基于FPGA的图像采集和集中显示系统中,常常要用到这种大容量、高速度的存储器。

但SDRAM的控制逻辑比较复杂,对时序要求也十分严格,这就要求有一个专门的控制器,使系统用户能很方便地操作SDRAM。

SDRAM器件的管脚分为控制信号、地址和数据3类。

通常一个SDRAM中包含几个BANK,每个BANK的存储单元是按行和列寻址的。

由于这种特殊的存储结构,SDRAM有以下几个工作特性。

(1)SDRAM的初始化

SDRAM在上电100~200μs后,必须由一个初始化进程来配置SDRAM的模式存储器,模式存储器的值决定SDRAM的工作模式。

访问存储单位:

为减少I/O引脚数量,SDRAM复用地址线,所有在读写SDRAM时,先由ACTIVE命令激活要读写的BANK,并锁存行地址,然后在读写指令有效时锁存列地址。

一旦BANK被激活后,只有执行一次预充命令后才能再次激活同一BANK。

(2)刷新和预充

SDRAM的存储单元可以理解为一个电容,总是倾向于放电,因此必须有定时刷新周期以避免数据全失。

刷新周期可由(最小刷新周期+时候周期)计算获得。

对BANK预充电或者关闭已激活的BANK,可预充特定BANK也可同时作用于所有BANK,A10、BA0和BA1用于选择BANK。

(3)操作控制

SDRAM的具体控制命令由一些专用控制引脚和地址线辅助完成。

CS、RAS、CAS和WR在时钟上升沿的状态决定具体操作动作,地址线和BANK选择控制线在部分操作动作中作为辅助参数输入。

由于特殊的存储结构,SDRAM操作指令比较多,不像SRAM一样只有简单的读写。

根据系统要求,本设计选用SAMSUNG的K4S6432SDRAM芯片。

3.2SDRAM控制器总体设计

SDRAM控制器与外部的接口示意图由图4给出,控制器右端接口信号均为直接与SDRAM对应管脚相连的信号;控制器左端的接口信号为与FPGA相连的系统控制接口信号,其中,CLK为系统时钟信号,RESET_N为复位信号,ADDR为系统给出的SDRAM地址信号,DAIN是系统用于写入SDRAM的数据信号,FPGA_RD和FPGA_WR为系统读、写请求信号(1为有效,0为无效),SDRAM_FREE是SDRAM的空闲状态标示信号(0为空闲,1为忙碌),FDATA_ENABLE是控制器给系统的数据收发指示信号(为0时,无法对SDRAM进行数据收发;为1时,若是系统读操作,则系统此时可从DAOUT接收SDRAM的数据,若是写操作,则系统此时可以通过DAIN发送数据给SDRAM)。

图4总体设计框图和外部接口信号

参照SDRAM的数据手册可知,它的指令译码对照表如表1所示。

表1SDRAM指令译码对照表

命令

CS_

RAS_

CAS_

WE_

A10AP

空操作指令(NOP)

0

1

1

1

X

刷新指令(REF/SELF)

0

0

0

1

X

读写停止指令(BST)

0

1

1

0

X

模式设置指令(MRS)

0

0

0

0

0/1

激活指令(ACTIVE)

0

0

1

1

0/1

读指令(READ)

0

1

0

1

0

带预充的读指令(READA)

0

1

0

1

1

写指令(WRITE)

0

1

0

0

0

带预充的写指令(WRITEA)

0

1

0

0

1

预充指令(PRE)

0

0

1

0

0

仔细分析SDRAM的各个接口信号、时序要求和工作模式,将该SDRAM控制器的内部进一步细化为多个功能模块,结构组成如图5所示,包括系统控制接口模块、CMD命令解析模块、命令相应模块、数据通路模块。

系统控制接口模块用于接收系统的控制信号,进而产生不同的CMD命令组合;CMD命令解析模块用于接收CMD命令并解码成操作指令;命令响应模块用于接收操作指令并产生SDRAM的操作动作;数据通路模块则用于控制数据的有效输入输出。

图5SDRAM控制器的结构图

3.3SDRAM系统控制接口子模块设计

该模块主要包括初始化和系统指令分析功能。

其工作过程如下:

由计数器控制在系统上电约200μs后,先进行SDRAM的初始化配置工作,由一个Prechargeallback指令完成对所有BANK的预充,接着是多个Refresh指令,然后是模式配置指令LOADMODE,完成SDRAM的工作模式设置。

之后进行控制器的初始化配置工作,先发出指令LOADREG1给控制器载入模式字,再发出LOADREG2指令载入控制器的刷新计数器值,完成控制器初始化配置。

上述初始化过程结束后,系统指令分析机制才可接收并分析系统的读写信号和地址信息,以及从下个模块反馈回来的CMD_ACK信号,并产生对应的CMD命令和SADDR地址信息给CMD命令解析模块。

通过程序设置,实现了根据初始化配置的参数来确定在读写到特定时刻发出Precharge或者Refresh的CMD指令,从而简化了系统的控制。

而每当收到CMD_ACK为1时,表示CMD指令已经发出并有效,此时就要发出NOP命令(CMD=000)。

要说明的是,SADDR是分时复用的,在初始化载入模式时,SADDR用以传输用户自己定义的模式字内容;而在正常的读写期间,SADDR作为地址线传输SDRAM所需的行、列和块地址。

代码示例如附件1.

3.4CMD命令解析和命令相应子模块

该模块首先对CMD指令进行判断,其结果解释输出相应的操作指令进行响应。

例如,CMD为001时,则会输出do_read信号为1;CMD为010时,则会输出do_write信号为1,在同一时刻,只会输出一种有效的操作指令。

然后该模块根据操作指令,做出符合SDRAM读写规范的操作动作,来进行用户期望的操作;给出数据选通信号OE,来控制数据通路模块(写操作OE为1,读操作时OE为0)。

此外,该模块把系统非复用的地址ADDR处理为SDRAM复用的地址,分时送给SA、BA。

程序中地址复用的方法为:

assignraddr=ADDR[ROWSTART+ROWSIZE-1:

ROWSTART];//raddr为行地址

assigneaddr=ADDR[COLSTART+COLSIZE-1:

COLSTART];//eaddr为列地址

assignbaddr=ADDR[BANKSTART+BANKSIZE-1:

BANKSTART];//baddr为BANK地址

在程序中,WRITEA和READA的CMD指令实际隐含了ACTIVE命令,所以该模块在收到do_write或do_read指令后,会先进行激活动作,经过初始化配置规定的CAS延迟时间之后再进行读写动作。

此外,该模块内含用以预设某些模式参数的模式寄存器,主要包括3类:

第1类是SDRAM模式控制寄存器,在LOADMODE指令时,将该寄存器的值送入SDRAM的模式寄存器中,以控制SDRAM的工作模式;第2类是SDRAM控制器的参数寄存器(LOAD_REG1),使得SDRAM控制器的工作方式与外部的SDRAM器件的工作方式匹配;第3类是SDRAM的刷新周期控制寄存器,该寄存器预设用户定义的自动刷新计数值,用于SDRAM的刷新周期预设。

上述3类寄存器的预设值都是系统控制接口模块在初始化时通过SADDR传送给来的。

收到各类操作指令后,该模块会反馈给CMD命令解析模块cmdack信号为1,并最终反馈到系统控制接口模块的CMDACK信号为1,如果没有收到任何操作指令,则cmdack=0,CMDACK信号为0。

代码示例如附件2.

3.5数据通路子模块

该模块受OE信号的控制,使数据的进出和相应的操作指令在时序上同步。

OE为1时,数据可由DQ脚写入SDRAM,OE为0时,数据可从SDRAM的DQ脚读出。

因为是内部模块,所以应该尽量避免使用双向端口,因此在这里DQ的输入输出作用分别用端口DQIN和DQOUT代替,在顶层模块调用时再使用OE信号实现三态双向传输。

代码示例如附件3.

3.6SDRAM控制器顶层模块

实际上在大型工程开发过程中很少用到图形编辑工具,因为连接线较多不易连接,容易显得杂乱,可读性和可移植性都不强。

因此大多数模块调用都是通过代码形式来调用的,读者要熟悉并习惯使用在程序中调用另一个子模块的方式。

附件4是SDRAM控制器顶层模块代码示例,通过这种调用方式将其他子模块融合在一个统一的大工程下。

附件1:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

entitycontrol_interfaceis

generic(ASIZE:

integer:

=32);

port(

CLK:

instd_logic;

RESET_N:

instd_logic;

CMD:

instd_logic_vector(2downto0);

ADDR:

instd_logic_vector(ASIZE-1downto0);

REF_ACK:

instd_logic;

CM_ACK:

instd_logic;

NOP:

outstd_logic;

READA:

outstd_logic;

WRITEA:

outstd_logic;

REFRESH:

outstd_logic;

LOAD_MODE:

outstd_logic;

SADDR:

outstd_logic_vector(ASIZE-1downto0);

SC_CL:

outstd_logic_vector(1downto0);

SC_RC:

outstd_logic_vector(1downto0);

SC_RRD:

outstd_logic_vector(3downto0);

SC_PM:

outstd_logic;

SC_BL:

outstd_logic_vector(3downto0);

REF_REQ:

outstd_logic;

CMD_ACK:

outstd_logic;

);

endcontrol_interface;

architectureRTLofcontrol_interfaceis

--signaldeclarations

signalLOAD_REG1:

std_logic;

signalLOAD_REG2:

std_logic;

signalREF_PER:

std_logic_vector(15downto0);

signaltimer:

signed(15downto0);

signaltimer_zero:

std_logic;

signalSAADR_int:

std_logic_vector(ASIZE-1downto0);

signalCMD_ACK_int:

std_logic;

signalSC_BL_int:

std_logic_vector(3downto0);

begin

--ThismoduledecodesthecommandsfromtheCMDinputtoindividual

--commandlines,NOP,READA,WRITEA,REFRESH,PRECHARGE,LOAD_MODE;

--ADDRisregisterinordertokeepitalignedwithdecodedcommand.

process(CLK,RESET_N)

begin

if(RESET_N='0')then

NOP<='0';

READA<='0';

WRITEA<='0';

REFRESH<='0';

PRECHARGE<='0';

LOAD_MODE<='0';

load_reg1<='0';

load_reg2<='0';

SAADR_int<=(others=>'0');

elseifrising_edge(CLK)then

SAADR_int<=ADDR;

if(CMD='000')then

NOP<='1';

else

NOP<='0';

endif;

if(CMD='001')then

READA<='1';

else

READA<='0';

endif;

if(CMD='010')then

WRITEA<='1';

else

WRITEA<='0';

endif;

if(CMD='011')then

REFRESH<='1';

else

REFRESH<='0';

endif;

if(CMD='100')then

PRECHARGE<='1';

else

PRECHARGE<='0';

endif;

if(CMD='101')then

LOAD_MODE<='1';

else

LOAD_MODE<='0';

endif;

if((CMD='110')and(LOAD_REG1='0'))then

LOAD_REG1<='1';

else

LOAD_REG1<='0';

endif;

if((CMD='111')and(LOAD_REG2='0'))then

LOAD_REG2<='1';

else

LOAD_REG2<='0';

endif;

endif;

endprocess;

.......

EndRTL;

附件2:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

entitycommandis

generic(

ASIZE:

integer:

=23;

DSIZE:

integer:

=32;

ROWSIZE:

integer:

=12;

COLSIZE:

integer:

=9;

BANKSIZE:

integer:

=2;

ROWSTART:

integer:

=9;

COLSTART:

integer:

=0;

BANKSTART:

integer:

=20;

);

port(

CLK:

instd_logic;

RESET_N:

instd_logic;

SADDR:

instd_logic_vector(ASIZE-1downto0);

NOP:

instd_logic;

READA:

instd_logic;

WRITEA:

instd_logic;

REFRESH:

instd_logic;

PRECHARGE:

instd_logic;

LOAD_MODE:

instd_logic;

SC_CL:

instd_logic_vector(1downto0);

SC_RC:

instd_logic_vector(1downto0);

SC_RRD:

instd_logic_vector(3downto0);

SC_PM:

instd_logic;

SC_BL:

instd_logic_vector(3downto0);

REF_REQ:

instd_logic;

REF_ACK:

outstd_logic;

CM_ACK:

outstd_logic;

OE:

outstd_logic;

SA:

outstd_logic_vector(11downto0);

BA:

outstd_logic_vector(1downto0);

CS_N:

outstd_logic_vector(1downto0);

CKE:

outstd_logic;

RAS_N:

outstd_logic;

CAS_N:

outstd_logic;

WE_N:

outstd_logic;

);

endcommand;

architectureRTLofcommandis

--signaldeclarations

signaldo_nop:

std_logic;

signaldo_reada:

std_logic;

signaldo_writea:

std_logic;

signaldo_writea1:

std_logic;

signaldo_refresh:

std_logic;

signaldo_precharge:

std_logic;

signaldo_load_mode:

std_logic;

signalcommand_done:

std_logic;

signalcommand_delay:

std_logic_vector(7downto0);

signalrw_shift:

std_logic_vector(3downto0);

signaldo_act:

std_logic;

signalrw_flag:

std_logic;

signaldo_rw:

std_logic;

signaloe_shift:

std_logic_vector(7downto0);

signaloe1:

std_logic;

signaloe2:

std_logic;

signaloe3:

std_logic;

signaloe4:

std_logic;

signalrp_shift:

std_logic_vector(3downto0);

signalrp_done:

std_logic;

signalrowaddr:

std_logic_vector(ROWSIZE-1downto0);

signalcoladdr:

std_logic_vector(COLSIZE

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基于 FPGA 数字 CMOS 摄像机 图像 采集 精编

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx