西电微电子学院数字集成电路上机作业.docx

西电微电子学院数字集成电路上机作业.docx

- 文档编号:28896430

- 上传时间:2023-07-20

- 格式:DOCX

- 页数:26

- 大小:342.70KB

西电微电子学院数字集成电路上机作业.docx

《西电微电子学院数字集成电路上机作业.docx》由会员分享,可在线阅读,更多相关《西电微电子学院数字集成电路上机作业.docx(26页珍藏版)》请在冰豆网上搜索。

西电微电子学院数字集成电路上机作业

《数字集成电路》上机实验

姓名:

***

班级:

***

学号:

***

第一次实验

一、实验目的:

掌握HSPICES软件的使用方法,用于分析二极管及CMOS反相器的直流特性,通过改变电源电压及MOS管的宽长比得到一组CMOS反相器的电压传输特性曲线,从而理解CMOS反相器电压传输特性曲线的影响因素和调整方法。

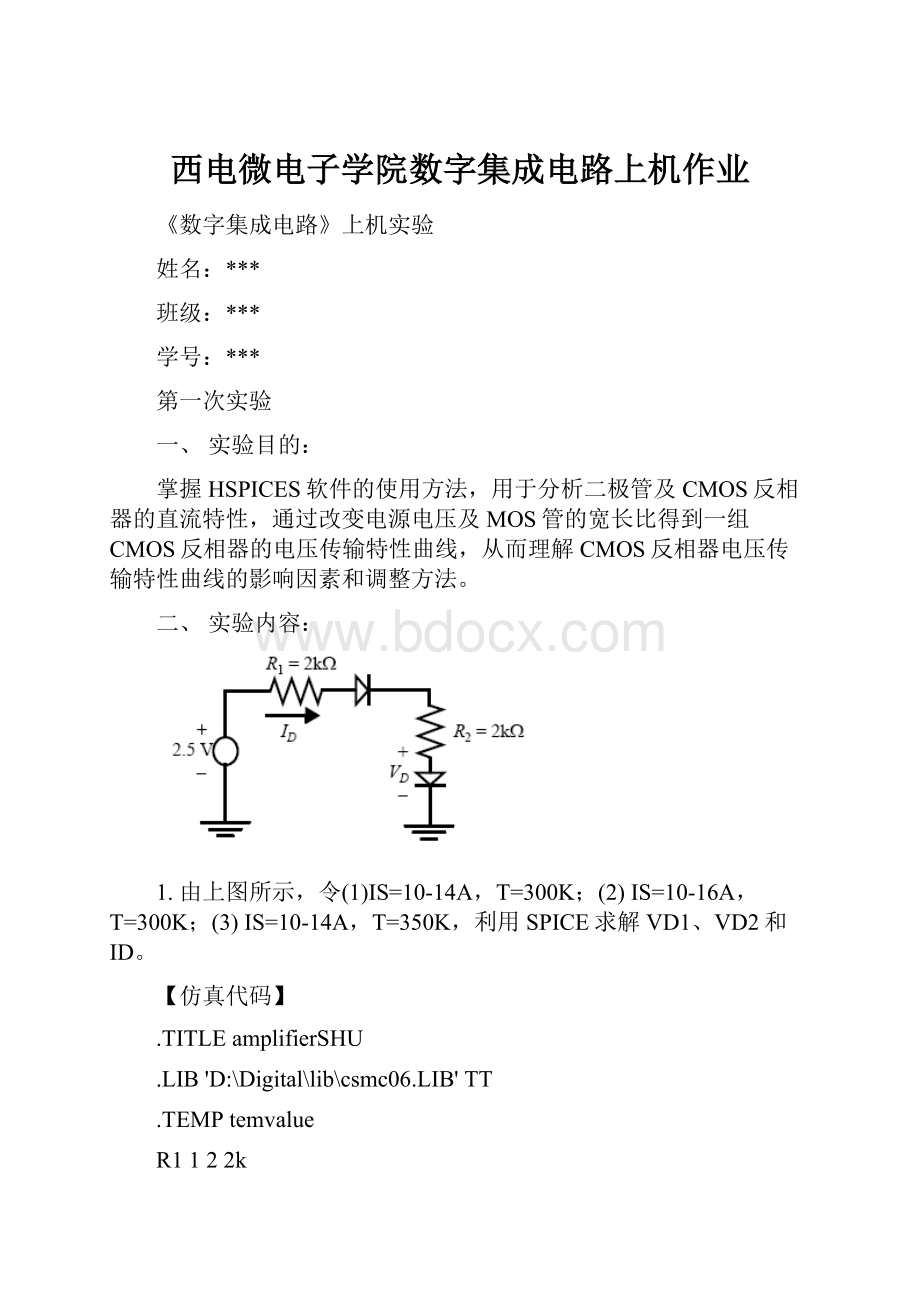

二、实验内容:

1.由上图所示,令

(1)IS=10-14A,T=300K;

(2)IS=10-16A,T=300K;(3)IS=10-14A,T=350K,利用SPICE求解VD1、VD2和ID。

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\csmc06.LIB'TT

.TEMPtemvalue

R1122k

R2342k

D123DMOD

D240DMOD

.MODELDMODDIs=isvalue

.PARAMtemvalue=27isvalue=1E-14

V110DC2.5

.OP

.ALTER

.PARAMtemvalue=27isvalue=1E-16

.ALTER

.PARAMtemvalue=77isvalue=1E-14

.OPIONSLISTNODEPOST=2

.END

【结果】

【分析】

VD1=525.4463mv、VD2=525.4463mv和ID=362.2768uA

2.

(1)由下图所示,令Vin从0V变化到2.5V,步长为0.5V,利用SPICE求M1管电流变化的曲线,判断管子的工作状态;当M1的尺寸变化为W/L=4u/1u时,求IM1,并解释两条曲线存在误差的原因。

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.PARAMdd=2.5

Vdd10DCdd

Vin20DC

M_M10211pchL=1UW=4U

.DCVin02.50.5

.PRINTI

(2)

.OP

.OPTIONNODELISTPOST

.END

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.PARAMdd=2.5

Vdd10DCdd

Vin20DC

M_M10211pchL=0.25UW=1U

.DCVin02.50.5

.PRINTI

(2)

.OP

.OPTIONNODELISTPOST

.END

【结果】

【分析】

在1.5V之前是工作在线性区,1.5-2V之间是可变电阻区,2V以后工作在饱和区。

(2)如上图所示,取一组Vin值(0,0.5,1,1.5,2,2.5),令VDD从0V变化到2.5V,步长为0.5V,利用SPICE求M1管的I-V特性曲线。

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.PARAMdd=2.5

Vdd10DCdd

Vin20DC

M_M10211pchL=0.25UW=12U

.DCVin02.50.5sweepVdd02.50.5

.PRINTI

(2)

.OP

.OPTIONNODELISTPOST

.END

【结果】

【分析】

当加上不同的栅电压时,会造成沟道的宽度不一样,源漏电压一定时,沟道电流的大小不一样。

栅电压越大,电流越大。

三、实验步骤:

1、对照电路编写网表

2、运行HSPICE

a.点击OPEN键,加载编写好的网表;

b.点击SIMULATE键,进行仿真;

c.点击EDITLL键,查个输出结果;若发现有错误,点击EDITNL键修改网表,保存后继续b步操作;

d.点击AVANWAVES,打开图形化窗口察看各种输入输出波形。

第二次实验

一、实验内容:

3.

(1)求上述反相器的电压转换曲线,根据其特性曲线找出电路临界电压值Vckt(Vckt=Vin=Vout);(.dcvin00.250.25)

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.PARAMdd=2.5

Vdd10DCdd

Vin20DC

Vsb04DC

M_Mp3211pchL=0.25UW=1.25U

M_Mn3204nchL=0.25UW=0.375U

.DCVin02.50.01

.PRINTDCV(Vin)V(Vout)

.OP

.OPTIONNODELISTPOST

.END

【结果】

【分析】

根据其特性曲线找出电路临界电压值Vckt为1.26V

(2)若想得到Vckt=Vdd/2的电路临界值,那么PMOS及NMOS的栅极宽度比值应该是多少?

(扫描wn或wp,根据模型提供的宽长比范围选择扫描范围。

wn(0.35u~0.4u,0.001u),wp(1.2u~1.21u,0.001u),范围越小,线性度越好。

Vinvin0DC1.25

.dcwp1.2u1.21u0.001u)

【仿真代码】

.OPTIONPOSTNODELIST

.LIB'E:

\Digital\lib\mix025_1.lib'TT

M_M13211pchL=0.25uwp=1.25u

M_M23204nchL=0.25uwn=0.35u

vdd10dc2.5

vin20dc1.25

vsb40dc0.3

.dcvin00.250.25sweepwn0.35u0.4u0.001u

.op

.plotv

(2)v(3)

.end

【结果】

【分析】

PMOS及NMOS的栅极宽度比值应该是PMOSL=0.25uwp=1.25u。

NMOSL=0.25uwn=0.35u

(3)令VSB从0变化到0.3V,求反相器的电压转换曲线,解释VOUT产生变化的原因。

(.dcvin02.50.25sweepvsb00.30.1)

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.PARAMdd=2.5

Vdd10DCdd

Vin20DC

Vsb04DC

M_Mp3211pchL=0.25UW=1.25U

M_Mn3204nchL=0.25UW=0.375U

.DCVin02.50.01sweepVsb00.30.06

.PRINTDCV(Vin)V(Vout)

.OP

.OPTIONNODELISTPOST

.END

【结果】

【分析】

由于源和衬底之间存在电压,会使衬底电子的能量变高,也就是说源漏之间的势垒高度会变高,则需要更大的栅压才能导通源漏,也就是使得阈值电压变大了

4.考虑下图中的电路:

(1)如上图所示,输入一个脉冲信号Vin:

pulse(0Vdd5n0.1n0.1n9n20n),.测量它的上升时间tr、下降时间tf、传播延时tp和平均功耗。

其中:

tp=(TPLH+TPHL)/2

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

vdd10dc2.5

vin20pulse(02.55n0.1n0.1n9n20n)

M_M13211pchL=0.25uWp=1.25u

M_M23200nchL=0.25uWn=0.375u

.MEASTRANVmaxmaxV(3)FROM=0.01nTO=20n

.MEASTRANVminminV(3)FROM=0.01nTO=20n

.MEASTRANtrTRIGV(3)VAL='0.1*(Vmax-Vmin)+Vmin'RISE=2

+TARGV(3)VAL='0.9*(Vmax-Vmin)+Vmin'RISE=2

.MEASTRANtfTRIGV(3)VAL='0.9*(Vmax-Vmin)+Vmin'FALL=2

+TARGV(3)VAL='0.1*(Vmax-Vmin)+Vmin'FALL=2

.MEASTRANtpPARAM='0.5*(tf+tr)'

.MEASTRANAvgPpowerAVGP(Vin)FROM=0.01nsTO=60ns

.tran0.01n60n

.PRINTTRANP(3)P

(2)power

.OP

.OPTIONNODELISTPOST

.END

【结果】

【分析】

如结果所示,上升时间tr为6.5581E-11s、下降时间tf为5.2444E-11s、传播延时tp为5.9013E-11s和平均功耗1.9845E-05W

(2)当Vdd从1V变化到2.5V,且步长为0.25时,测量tp和平均功耗。

利用这些数据绘出“tp—Vdd”、“Power—Vdd”,分析Vdd变化对转换器性能有什么影响。

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.prot

.unpr

M_M13211pchL=0.25uWp=1.25u

M_M23200nchL=0.25uWn=0.375u

vdd10dc2.5

vin20pulse(02.55n0.1n0.1n9n20n)

.MEASTRANVmaxmaxV(3)FROM=0.01nTO=20n

.MEASTRANVminminV(3)FROM=0.01nTO=20n

.MEASTRANtrTRIGV(3)VAL='0.1*(Vmax-Vmin)+Vmin'RISE=2

+TARGV(3)VAL='0.9*(Vmax-Vmin)+Vmin'RISE=2

.MEASTRANtfTRIGV(3)VAL='0.9*(Vmax-Vmin)+Vmin'FALL=2

+TARGV(3)VAL='0.1*(Vmax-Vmin)+Vmin'FALL=2

.MEASTRANtpPARAM='0.5*(tf+tr)'

.MEASTRANAvgPowerAVGP(Vin)FROM=0.01nsTO=60ns

.tran0.01n60nsweepvdd12.50.25

.END

【结果】

tp—Vdd

Power—Vdd

【分析】

由结果中图表可以看出来,随着Vdd的增加,tp先明显增加,然后趋于平稳并很缓地下降。

平均功耗随着Vdd的增加先减小再趋于平稳,最后继续下降。

5.考虑下图中的电路:

图5CMOS组合逻辑门

a.CMOS晶体管网络所完成的逻辑功能是什么?

确定NMOS和PMOS器件的尺寸,使得输出电阻与由一个W/L=4的NMOS管和一个W/L=8的PMOS管组成的反相器的输出电阻相等。

(.TFV(out)vin)

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

M_M17188pchL=0.25uW=2u

M_M27388pchL=0.25uW=2u

M_M37698pchL=0.25uW=4u

M_M49588pchL=0.25uW=4u

M_M57540nchL=0.25uW=3u

M_M67640nchL=0.25uW=3u

M_M74320nchL=0.25uW=3u

M_M82100nchL=0.25uW=3u

vdd80dc2.5

va60pulse(02.55n0.1n0.1n9n20n)

vb50pulse(02.55n0.1n0.1n9n20n)

vc30pulse(02.55n0.1n0.1n9n20n)

vd10pulse(02.55n0.1n0.1n9n20n)

.tran0.1n20n

.TFV(7)va

.OPTIONPOSTNODELIST

.end

【结果】

【分析】

由分析可以得出尺寸:

M_M17188pchL=0.25uW=2u

M_M27388pchL=0.25uW=2u

M_M37698pchL=0.25uW=4u

M_M49588pchL=0.25uW=4u

M_M57540nchL=0.25uW=3u

M_M67640nchL=0.25uW=3u

M_M74320nchL=0.25uW=3u

M_M82100nchL=0.25uW=3u

可以从仿真结果看出来输出电阻与由一个W/L=4的NMOS管和一个W/L=8的PMOS管组成的反相器的输出电阻相等。

b.什么样的输入模式导致最坏情况的tpHL和tpLH。

清楚说明为了获得最大的传播延时,初始输入模式是什么和那个(些)输入必须发生变化。

考虑内部节点的电容的效应。

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.PARAMalvdd=2.5v

M1voutvinvddvddPCHw=1.250ul=0.25u

M2voutvin0vsbNCHw=0.375ul=0.25u

Vddvdd0DCalvdd

Vsb0vsbDC0

Vinvin0pulse0alvdd5n0.1n0.1n9n20n

.TRAN0.1n60nSWEEPalvdd1v2.5v0.25v

.OPTIONSLISTNODEPOST=2

.measavg_powerAVGPOWER

.measTRANvmaxiMAXV(vin)FROM2nTO60n

.measTRANvminiMINV(vin)FROM2nTO60n

.measTRANvmaxoMAXV(vout)FROM2nTO60n

.measTRANvminoMINV(vout)FROM2nTO60n

.measTRANTPHLTRIGv(vin)VAL=('0.5*(vmaxi-vmini)+vmini')RISE=2

+TARGv(vout)VAL=('0.5*(vmaxo-vmino)+vmino')FALL=2

.measTRANTPLHTRIGv(vin)VAL=('0.5*(vmaxi-vmini)+vmini')FALL=2

+TARGv(vout)VAL=('0.5*(vmaxo-vmino)+vmino')RISE=2

.measTRANtpPARAM='(TPHL+TPLH)*0.5'

.END

【结果】

【分析】

.逻辑功能是实现F=(A+B)CD的非。

第三次实验

1.输入电容为10pf,采用2级反相器级联,其中反相器中的NMOS、PMOS的长度均采用最小尺寸LN=LP=0.25μm,WN=0.375μ,输入Vin为脉冲信号pulse(0Vdd5n0.1n0.1n9n20n),Vdd=2.5V,确定WP值以得到最小延迟时间,考虑延迟时间随WP值变化的原因。

图1buffer

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

VinIN0pulse(02.55n0.1n0.1n9n20n)

.PARAMvdd=2.5

.globalvdd

.SUBCKTINVINOUTwn=0.375uwp=1.2u

M1outin00nchW=wnL=0.25u

M2outinvddvddpchW=wpL=0.25u

.ENDS

X1IN1INVWn=0.375uWp=1.2u

X21OUTINVWn=0.375uWp=1.2u

CinIN010pf

VccVdd05V

.MEASTRANVmaxmaxV(out)FROM=0.01nTO=20n

.MEASTRANVminminV(out)FROM=0.01nTO=20n

.MEASTRANtrTRIGV(out)VAL='0.1*(Vmax-Vmin)+Vmin'RISE=2

+TARGV(in)VAL='0.9*(Vmax-Vmin)+Vmin'RISE=2

.MEASTRANtfTRIGV(out)VAL='0.9*(Vmax-Vmin)+Vmin'FALL=2

+TARGV(out)VAL='0.1*(Vmax-Vmin)+Vmin'FALL=2

.MEASTRANtpparam='0.5*(tr+tf)'

.TRAN0.01n60n

.END

【结果】

【分析】

由公式得延迟和WP成正比,所以WP越小,延迟越小。

故查lib得到WP的最小值为1.2um,故此时延迟最小。

2.考虑下图中的电路:

图5CMOS组合逻辑门

a.CMOS晶体管网络所完成的逻辑功能是什么?

确定NMOS和PMOS器件的尺寸,使得输出电阻与由一个W/L=4的NMOS管和一个W/L=8的PMOS管组成的反相器的输出电阻相等。

(.TFV(out)vin)

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

M_M17188pchL=0.25uW=2u

M_M27388pchL=0.25uW=2u

M_M37698pchL=0.25uW=4u

M_M49588pchL=0.25uW=4u

M_M57540nchL=0.25uW=3u

M_M67640nchL=0.25uW=3u

M_M74320nchL=0.25uW=3u

M_M82100nchL=0.25uW=3u

vdd80dc2.5

va60pulse(02.55n0.1n0.1n9n20n)

vb50pulse(02.55n0.1n0.1n9n20n)

vc30pulse(02.55n0.1n0.1n9n20n)

vd10pulse(02.55n0.1n0.1n9n20n)

.tran0.1n20n

.TFV(7)va

.OPTIONPOSTNODELIST

.end

【结果】

【分析】

由分析可以得出尺寸:

M_M17188pchL=0.25uW=2u

M_M27388pchL=0.25uW=2u

M_M37698pchL=0.25uW=4u

M_M49588pchL=0.25uW=4u

M_M57540nchL=0.25uW=3u

M_M67640nchL=0.25uW=3u

M_M74320nchL=0.25uW=3u

M_M82100nchL=0.25uW=3u

可以从仿真结果看出来输出电阻与由一个W/L=4的NMOS管和一个W/L=8的PMOS管组成的反相器的输出电阻相等。

b.什么样的输入模式导致最坏情况的tpHL和tpLH。

清楚说明为了获得最大的传播延时,初始输入模式是什么和那个(些)输入必须发生变化。

考虑内部节点的电容的效应。

【仿真代码】

.TITLEamplifierSHU

.LIB'D:

\Digital\lib\mix025_1.lib'TT

.PARAMalvdd=2.5v

M1voutvinvddvddPCHw=1.250ul=0.25u

M2voutvin0vsbNCHw=0.375ul=0.25u

Vddvdd0DCalvdd

Vsb0vsbDC0

Vinvin0pulse0alvdd5n0.1n0.1n9n20n

.TRAN0.1n60nSWEEPalvdd1v2.5v0.25v

.OPTIONSLISTNODEPOST=2

.measavg_powerAVGPOWER

.measTRANvmaxiMAXV(vin)FROM2nTO60n

.measTRANvminiMINV(vin)FROM2nTO60n

.measTRANvmaxoMAXV(vout)FROM2nTO60n

.measTRANvminoMINV(vout)FROM2nTO60n

.measTRANTPHLTRIGv(vin)VAL=('0.5*(vmaxi-vmini)+vmini')RISE=2

+TARGv(vout)VAL=('0.5*(vmaxo-vmino)+vmino')FALL=2

.measTRANTPLHTRIGv(vin)VAL=('0.5*(vmaxi-vmini)+vmini')FALL=2

+TARGv(vout)VAL=('0.5*(vmaxo-vmino)+vmino')RISE=2

.measTRANtpPARAM='(TPHL+TPLH)*0.5'

.END

【结果】

【分析】

.逻辑功能是实现F=(A+B)CD的非。

第四次实验

一.实验目的:

搭建反相器网络,理解多扇出反相器链的性能优化方法。

通过调整输入信号的上升下降时间和输出负载,理解输入输出信号的上升下降时间对电路性能功耗的影响。

二.实验内容:

1.由上图所示,假设Cl=64Cg,1,计算各级反相器的尺寸

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 微电子 学院 数字集成电路 上机 作业

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《贝的故事》教案4.docx

《贝的故事》教案4.docx