51 四人抢答器设计.docx

51 四人抢答器设计.docx

- 文档编号:2835565

- 上传时间:2022-11-15

- 格式:DOCX

- 页数:11

- 大小:91.53KB

51 四人抢答器设计.docx

《51 四人抢答器设计.docx》由会员分享,可在线阅读,更多相关《51 四人抢答器设计.docx(11页珍藏版)》请在冰豆网上搜索。

51四人抢答器设计

第5章数字系统程序设计与仿真实验

5.1四人抢答器程序设计与仿真实验

1.实验目的

设计一个四人抢答器。

2.实验原理

系统设计一个4人参加的智力竞赛抢答器,当有一参赛选手首先按下抢答器开关时,相应显示该选手所在抢答器开关的编号,此时抢答器不再接受其他的输入信号。

电路还具有时间控制功能,要求回答问题时间小于100秒,显示为(0-99),时间显示采用倒计时,当达到限定时间时,发出提示信号。

系统组成模块如下:

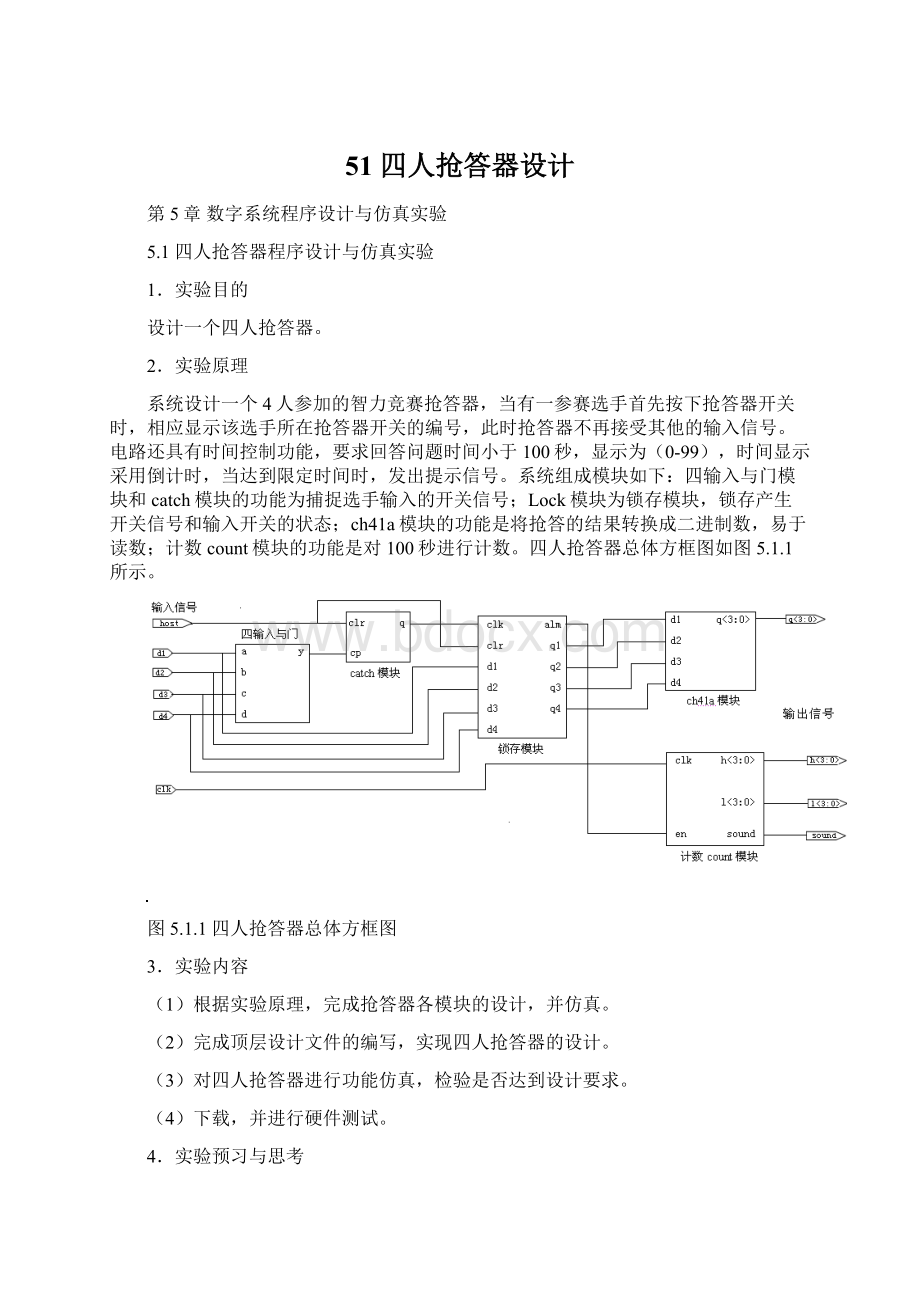

四输入与门模块和catch模块的功能为捕捉选手输入的开关信号;Lock模块为锁存模块,锁存产生开关信号和输入开关的状态;ch41a模块的功能是将抢答的结果转换成二进制数,易于读数;计数count模块的功能是对100秒进行计数。

四人抢答器总体方框图如图5.1.1所示。

图5.1.1四人抢答器总体方框图

3.实验内容

(1)根据实验原理,完成抢答器各模块的设计,并仿真。

(2)完成顶层设计文件的编写,实现四人抢答器的设计。

(3)对四人抢答器进行功能仿真,检验是否达到设计要求。

(4)下载,并进行硬件测试。

4.实验预习与思考

(1)考虑四人抢答器设计中信号传递的时间延迟方法。

(2)如何实现当已经有选手输入抢答信号后对其他选手的输入信号进行屏蔽。

5.程序设计与仿真

(1)程序设计

①四输入与门模块(略)。

libraryieee;

useieee.std_logic_1164.all;

entityand4is

port(a,b,c,d:

instd_logic;

z:

outstd_logic);

endand4;

architecturemediedofand4is

begin

z<=(aandb)and(candd);

endmedied;

②catch模块(catch.vhd)源程序如下,RTL电路如图5.1.2所示。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycatchis

Port(cp:

instd_logic;--脉冲

clr:

instd_logic;--复位信号

q:

outstd_logic);

endcatch;

architectureBehavioralofcatchis

begin

process(cp,clr)

begin

ifclr='0'then

q<='0';

elsifcp'eventandcp='0'then

q<='1';

endif;

endprocess;

endBehavioral;

图5.1.2catch模块RTL电路

③Lock模块(lock.vhd)为锁存模块,锁存产生开关信号时和输入开关的状态,锁存模块源程序如下,RTL电路图略。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitylockis

Port(d1:

instd_logic;--四位选手的输入信号

d2:

instd_logic;

d3:

instd_logic;

d4:

instd_logic;

clk:

instd_logic;

clr:

instd_logic;--复位

q1:

outstd_logic;--锁存数据输出

q2:

outstd_logic;

q3:

outstd_logic;

q4:

outstd_logic;

alm:

outstd_logic);--提示信号

endlock;

architectureBehavioraloflockis

begin

process(clk)

begin

ifclr='0'then

q1<='0';

q2<='0';

q3<='0';

q4<='0';

alm<='0';

elsifclk'eventandclk='1'then

q1<=d1;

q2<=d2;

q3<=d3;

q4<=d4;

alm<='1';

endif;

endprocess;

endBehavioral;

④ch41a模块(ch41a.vhd),此模块的功能是将抢答的结果转换成二进制数,易于读数,源程序如下,RTL电路图略。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitych41ais

Port(d1:

instd_logic;--选手信号

d2:

instd_logic;

d3:

instd_logic;

d4:

instd_logic;

q:

outstd_logic_vector(3downto0));--输出

endch41a;

architectureBehavioralofch41ais

begin

process(d1,d2,d3,d4)

variabletmp:

std_logic_vector(3downto0);

begin

tmp:

=d1&d2&d3&d4;

casetmpis

when"0111"=>q<="0001";

when"1011"=>q<="0010";

when"1101"=>q<="0011";

when"1110"=>q<="0100";

whenothers=>q<="1111";

endcase;

endprocess;

endBehavioral;

⑤count模块(count.vhd),本模块的功能是对100秒进行计数。

count模块源程序如下,RLT电路图略。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycountis

Port(clk:

instd_logic;--输入时钟

en:

instd_logic;--使能

h:

outstd_logic_vector(3downto0);--计时高位

l:

outstd_logic_vector(3downto0);--计时低位

sound:

outstd_logic);--计满提醒

endcount;

architectureBehavioralofcountis

begin

process(clk,en)

variablehh,ll:

std_logic_vector(3downto0);

begin

ifclk'eventandclk='1'then

ifen='1'then

ifll=0andhh=0then

sound<='1';

elsifll=0then

ll:

="1001";

hh:

=hh-1;

else

ll:

=ll-1;

endif;

else

sound<='0';

hh:

="1001";

ll:

="1001";

endif;

endif;

h<=hh;

l<=ll;

endprocess;

endBehavioral;

⑥顶层设计文件(ans_top.vhd),源程序如下:

RTL电路如图5.1.3所示。

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityans_topis

Port(d1:

instd_logic;--抢答输入的四个开关信号,低电平有效

d2:

instd_logic;

d3:

instd_logic;

d4:

instd_logic;

host:

instd_logic;

clk:

instd_logic;--系统时钟

q:

outstd_logic_vector(3downto0);--开关显示输出信号

h,l:

outstd_logic_vector(3downto0);--计时输出,分高低两位

sound:

outstd_logic);--限定时间完毕提醒,低电平有效

endans_top;

architectureBehavioralofans_topis

componentcatch

Port(cp:

instd_logic;

clr:

instd_logic;

q:

outstd_logic);

endcomponent;

componentch41a

Port(d1:

instd_logic;

d2:

instd_logic;

d3:

instd_logic;

d4:

instd_logic;

q:

outstd_logic_vector(3downto0));

endcomponent;

componentcount

Port(clk:

instd_logic;

en:

instd_logic;

h:

outstd_logic_vector(3downto0);

l:

outstd_logic_vector(3downto0);

sound:

outstd_logic);

endcomponent;

componentlock

Port(d1:

instd_logic;

d2:

instd_logic;

d3:

instd_logic;

d4:

instd_logic;

clk:

instd_logic;

clr:

instd_logic;

q1:

outstd_logic;

q2:

outstd_logic;

q3:

outstd_logic;

q4:

outstd_logic;

alm:

outstd_logic);

endcomponent;

componentmy_and4

Port(a:

instd_logic;

b:

instd_logic;

c:

instd_logic;

d:

instd_logic;

y:

outstd_logic);

endcomponent;

signalsq1,sq2,sq3,sq4,sq5,sq6,sq7:

std_logic;

begin

u0:

my_and4portmap(a=>d1,b=>d2,

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 51 四人抢答器设计 抢答 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx