EDA例题.docx

EDA例题.docx

- 文档编号:28195585

- 上传时间:2023-07-09

- 格式:DOCX

- 页数:23

- 大小:95.75KB

EDA例题.docx

《EDA例题.docx》由会员分享,可在线阅读,更多相关《EDA例题.docx(23页珍藏版)》请在冰豆网上搜索。

EDA例题

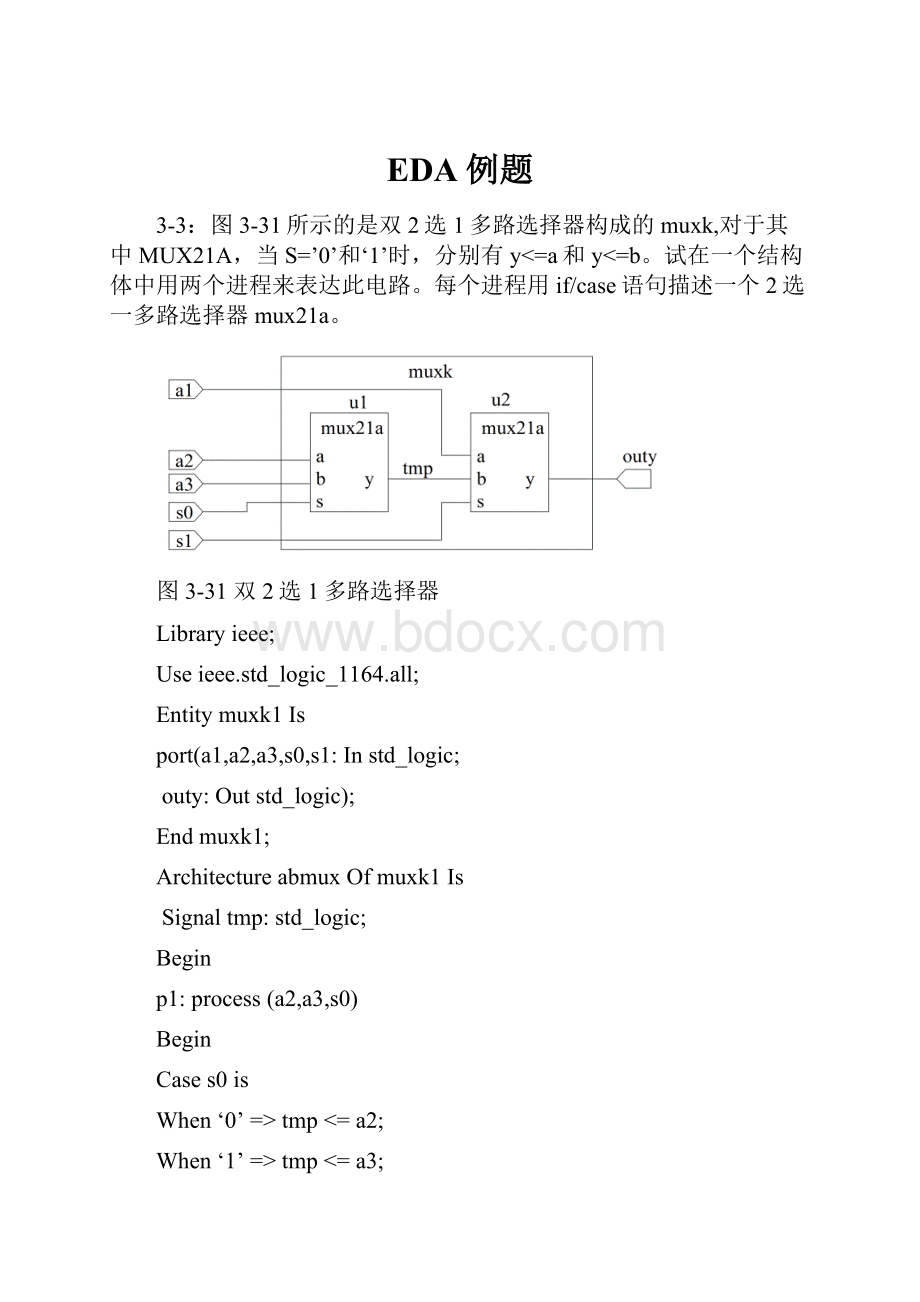

3-3:

图3-31所示的是双2选1多路选择器构成的muxk,对于其中MUX21A,当S=’0’和‘1’时,分别有y<=a和y<=b。

试在一个结构体中用两个进程来表达此电路。

每个进程用if/case语句描述一个2选一多路选择器mux21a。

图3-31双2选1多路选择器

Libraryieee;

Useieee.std_logic_1164.all;

Entitymuxk1Is

port(a1,a2,a3,s0,s1:

Instd_logic;

outy:

Outstd_logic);

Endmuxk1;

ArchitectureabmuxOfmuxk1Is

Signaltmp:

std_logic;

Begin

p1:

process(a2,a3,s0)

Begin

Cases0is

When‘0’=>tmp<=a2;

When‘1’=>tmp<=a3;

Whenothers=>Null;

EndCase;

Endprocess;

p2:

Process(a1,tmp,s1)

Begin

Cases1is

When‘0’=>outy<=a1;

When‘1’=>outy<=tmp;

Whenothers=>Null;

EndCase;

EndProcess;

Endabmux;

Libraryieee;

Useieee.std_logic_1164.all;

Entitymuxkis

Port(a1,a2,a3,s0,s1:

InStd_logic;

outy:

OutStd_logic);

Endmuxk;

ArchitectureabmuxOfmuxkis

Signaltmp:

Std_logic;

Begin

p1:

Process(a2,a3,s0)

Begin

Ifs0='1'Then

tmp<=a2;

Else

tmp<=a3;

EndIf;

EndProcess;

p2:

Process(a1,tmp,s1)

Begin

Ifs1='1'Then

outy<=a1;

Else

outy<=tmp;

Endif;

EndProcess;

Endabmux;

3-4给出一位全减器的VHDL描述,要求:

(1)首先设计1位半减器,然后用例化语句将他们连接起来,图3-32中h_suber是半减器,diff是输出差,s_out是借位输出,sub_in是借位输入。

(2)以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(x-y-subin=diffr)。

半减器程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYh_suberIS

PORT(x,y:

INSTD_LOGIC;

diff,s_out:

OUTSTD_LOGIC);

ENDENTITYh_suber;

ARCHITECTUREhOFh_suberIS

SIGNALab:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

ab<=x&y;

PROCESS(ab)

BEGIN

CASEabIS

WHEN“11”=>diff<=‘0’;s_out<=‘0’;

WHEN“10”=>diff<=‘1’;s_out<=‘0’;

WHEN“01”=>diff<=‘1’;s_out<=‘1’;

WHEN“00”=>diff<=‘0’;s_out<=‘0’;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

ENDARCHITECTUREh;

1位减法器

ENTITYf_suberis

Port(x:

InStd_logic;

y:

InStd_logic;

sub_in:

InStd_logic;

Diffr:

OutStd_logic;

sub_out:

OutStd_logic);

ENDf_suber;

ARCHITECTUREfs1Off_suberIs

Componenth_suber

Port(x,y:

InStd_logic;

s_out,diff:

OutStd_logic);

ENDComponent;

Componentor2a

Port(a,b:

InStd_logic;

c:

OutStd_logic);

ENDComponent;

Signald,e,f:

Std_logic;

Begin

U1:

h_suberportmap(x=>x,y=>y,diff=>d,s_out=>e);

U2:

h_suberportmap(x=>d,y=>sub_in,diff=>diffr,s_out=>f);

U3:

or2aportmap(a=>e,b=>f,c=>sub_out);

ENDARCHITECTUREfs1;

Libraryieee;

Useieee.std_logic_1164.all;

Entitysub8is

Port(a0,a1,a2,a3,a4,a5,a6,a7:

InStd_logic;

b0,b1,b2,b3,b4,b5,b6,b7:

InStd_logic;

subn_in:

InStd_logic;

s0,s1,s2,s3,s4,s5,s6,s7:

Outstd_logic);

Endsub8;

Architectureoneofsub8is

Componentf_suber

Port(x,y:

InStd_logic;

sub_in:

InStd_logic;

diffr:

OutStd_Logic

sub_out:

OutStd_logic);

EndComponent;

Signals0,s1,s2,s3,s4,s5,s6,s7:

Std_logic;

Begin

u1:

f_suber

PortMap(x=>a0,y=>b0,sub_in=>subn_in,diffr=>s0,sub_out=>s0);

u2:

f_suber

PortMap(x=>a1,y=>b1,sub_in=>s0,diffr=>s1,s_out=>s1);

u3:

f_suber

PortMap(x=>a2,y=>b2,sub_in=>s1,diffr=>s2,sub_out=>s2);

u4:

f_suber

PortMap(x=>a3,y=>b3,sub_in=>s2,diffr=>s3,sub_out=>s3);

u5:

f_suber

PortMap(x=>a4,y=>b4,sub_in=>s3,diffr=>s4,sub_out=>s4);

u6:

f_suber

Portmap(x=>a5,y=>b5,sub_in=>s4,diffr=>s5,sub_out=>s5);

u7:

f_suber

PortMap(x=>a6,y=>b6,sub_in=>s5,diffr=>s6,sub_out=>s6);

u8:

f_suber

PortMap(x=>a7,y=>b7,sub_in=>s6,diffr=>s7,sub_out=>s7);

Endone;

3-6根据图3-34,写出顶层文件MX3256.vhd的VHDL设计文件。

图3-34MX3256内部结构

LIBRARYieee

USEieee.std_logic_1164.all;

ENTITYMX3256is

port(CLK,INA,INB,INC:

inSTD_LOGIC;

OUT1,G:

OUTSTD_LOGIC);

END;

ARCHITECTUREAofMX3256is

COMPONENTLK35

PORT(A1,A2,CLK:

InSTD_LOGIC;

O1,O2:

OutSTD_LOGIC);

EndCOMPONENT;

COMPONENTmux

PORT(A,B,S:

InSTD_LOGIC;

C:

OutSTD_LOGIC);

EndCOMPONENT;

COMPONENTDFF

PORT(D,CLK,C:

InSTD_LOGIC;

Q:

OutSTD_LOGIC);

EndCOMPONENT;

SIGNALE,F,H:

STD_LOGIC;

BEGIN

U1:

LK35

PORTMAP(A1=>INA;A2=>INB,CLK=>INCK,O1=>E,O2=>S);

U2:

LK35

PORTMAP(A1=>S;A2=>F,CLK=>INCK,O1=>H,O2=>OUT1);

U3:

DFFPORTMAP(D=>E,CLK=>INCK,C=>INC);

U4:

MUXPORTMAP(B=>E,A=>H,S=>S,C=>G);

END;

3-7异步清零、同步置数、同步使能的加减计数器设计。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEieee.std_logic_unsigned.all;

ENTITYCOUNT16bIS

PORT(clk,clr,en,up,load:

INSTD_LOGIC;

datain:

INSTD_LOGIC_VECTOR(15DOWNTO0);

Q:

OUTSTD_LOGIC_VECTOR(15DOWNTO0);

count1,count2:

OUTSTD_LOGIC);

END;

ARCHITECTUREONEOFCOUNT16bIS

SIGNALcoun:

STD_LOGIC_VECTOR(15DOWNTO0);

BEGIN

q<=coun;

PROCESS(clk,clr,en,load)

BEGIN

IF(clr='1')THEN

coun<=0;

ELSIF(clk'EVENTANDclk='1')THEN

IF(load='1')THEN

coun<=datain;

ELSIF(en='1')THEN

Caseupis

When'1'=>coun<=coun+'1';

WhenOthers=>coun<=coun-'1';

EndCase;

ENDIF;

ENDIF;

ENDPROCESS;

count1<='1'Whenen='1'And(up='1'andcoun=“111111*********1”);

count2<='1'Whenen='1'And(up='0'andcoun=0);

ENDONE;

5-4根据图5-14(a)所示的状态图,分别按照图5-14(b)和图5-14(c)写出对应结构的VHDL状态机。

(a)

图5-14状态机

(1)图(b)状态机,为单进程状态机,程序如下:

libraryieee;

useieee.std_logic_1164.all;

ENTITYm1IS

PORT

(clk,rst:

INstd_logic;

ina:

INstd_logic_vector(2downto0);

outa:

OUTstd_logic_vector(3downto0));

ENDm1;

ARCHITECTUREaOFm1IS

Typestate_typeIs(s0,s1,s2,s3);

Signalstate:

state_type;

BEGIN

reg:

PROCESS(clk,rst)

BEGIN

IF(rst='1')THENstate<=s0;

ELSIF(clk'EVENTANDclk='1')THEN

CasestateIs

Whens0=>

caseinais

when"101"=>outa<="0010";

when"111"=>outa<="1100";

whenothers=>null;

endcase;

state<=s1;

Whens1=>IF(ina="000")THEN

state<=s1;

ELSIF(ina="110")Then

state<=s2;

ENDIF;outa<="1001";

Whens2=>IF(ina="100")THEN

state<=s2;

ELSEstate<=s3;

ENDIF;outa<="1111";

Whens3=>

caseinais

when"101"=>outa<="1101";

when"011"=>outa<="1110";

whenothers=>null;

endcase;

state<=s0;

WHENOTHERS=>STATE<=S0;

EndCase;

ENDIF;

ENDPROCESS;

end;

libraryieee;

useieee.std_logic_1164.all;

ENTITYm1IS

PORT

(clk,rst:

INstd_logic;

ina:

INstd_logic_vector(2downto0);

outa:

OUTstd_logic_vector(3downto0));

ENDm1;

ARCHITECTUREaOFm1IS

Typestate_typeIs(s0,s1,s2,s3);

Signalstate:

state_type;

BEGIN

reg:

PROCESS(clk,rst)

BEGIN

IF(rst='1')THENstate<=s0;

ELSIF(clk'EVENTANDclk='1')THEN

CasestateIs

Whens0=>IF(ina="101")THEN

outa<="0010";

ELSIF(ina="111")Then

outa<="1100";

ENDIF;state<=s1;

Whens1=>IF(ina="000")THEN

state<=s1;

ELSIF(ina="110")Then

state<=s2;

ENDIF;outa<="1001";

Whens2=>IF(ina="100")THEN

state<=s2;

ELSIF(ina="001")Then

state<=s3;

ELSEstate<=s1;

ENDIF;outa<="1111";

Whens3=>IF(ina="101")THEN

outa<="1101";

ELSIF(ina="011")Then

outa<="1110";

ENDIF;

state<=s0;

WHENOTHERS=>STATE<=S0;

EndCase;

ENDIF;

ENDPROCESS;

end;

(2)图(C)状态机,为双进程状态机,程序如下:

Libraryieee;

Useieee.std_logic_1164.all;

ENTITYm2IS

PORT(clk,rst:

INStd_logic;

ina:

INStd_logic_vector(2downto0);

outa:

OUTStd_logic_vector(3downto0));

ENDm2;

ARCHITECTUREaOFm2IS

Typestate_typeIs(s0,s1,s2,s3);

Signalsignal1:

state_type;

BEGIN

reg:

PROCESS(clk,signal1,rst)

BEGIN

IF(rst='1')THENsignal1<=s0;

ELSIF(clk'EVENTANDclk='1')THEN

casesignal1is

Whens0=>signal1<=s1;

Whens1=>IFina="000"Thensignal1<=s1;Elsesignal1<=s2;EndIf;

Whens2=>IFina="100"Thensignal1<=s2;Elsesignal1<=s3;EndIf;

Whens3=>signal1<=s0;

ENDcase;

ENDif;

ENDPROCESS;+

Com:

PROCESS(signal1,ina,clk)

variableouta1:

Std_logic_vector(3downto0);

Begin

Casesignal1is

Whens0=>

caseinais

when"101"=>outa1:

="0010";

when"111"=>outa1:

="1100";

whenothers=>outa1:

="0000";

endcase;

Whens1=>IF(ina="000")THEN

outa1:

="1001";

ENDIF;

Whens2=>IF(ina="100")THEN

outa1:

="1111";

ENDIF;

Whens3=>IF(ina="101")THEN

outa1:

="1101";

ELSIF(ina="011")THEN

outa1:

="1110";

ENDIF;

WHENOTHERS=>outa1:

="0000";

EndCase;

IF(clk'EVENTANDclk='1')THEN

outa<=outa1;

endif;

ENDPROCESS;

End;

8-7表达式c<=a+b中,A,B,C的数据类型都是STD_LOGIC_VECTOR,是否能直接进行加法运算?

说明原因和解决办法。

答:

不能。

由于VHDL没有定义STD_LOGIC_VECTOR的“+”,操作。

解决办法是加载IEEE.STD_LOGIC_UNSIGEN程序包,使用语句:

USEIEEE.STD_LOGIC_UNSIGEN.ALL;

8-8VHDL中有那三种数据对象?

详细说明它们的功能特点及其使用方法,举例说明数据对象与数据类型的关系。

答:

信号,变量,常数。

变量Variable和信号Signal一样,属于中间过渡节点量。

使用方法:

◆变量Variable说明:

变量名:

数据类型

◆变量Variable赋值:

目标变量名:

=表达式;

◆Signal说明:

信号名:

数据类型

◆信号Signal赋值:

目标信号名<=表达式AFTER时间量;

变量VARIABLE:

是局部的信息载体,只能在进程和子程序中使用。

◆常数

Constant常数名:

数据类型:

=表达式;

注意:

常数数据对象定义的同时进行赋值。

赋值符号为“:

=”

特点:

信号Signal:

是模块间的信息载体,在结构体中各进程间传递信息。

在结构体中有效。

变量:

在进程中立即赋值,不能设置传输延迟量。

信号:

在进程的最后才对信号赋值,信号可以设置传输延迟量。

……

8-10判断下列VHDL代码标识符是否合法,如果有误指出原因.

答:

16#0FA#正确

10#12F#错误,10进制没有F

8#789#错误,10进制没有9

8#356#正确

2#0101010#正确

74HC245错误,只能以英文开头

\74HC574\错误,只能用英文与数字

CLR/RESET错误,只能用英文与数字

\IN4/SCLK错误,只能用英文与数字

D100%错误,只能用英文与数字

9-5下述VHDL代码的综合结果会有几个触发器或锁存器?

程序1:

Architecturertlofexis

Signala,b:

std_logic_vector(3downto0);

Begin

Process(clk)

Begin

Ifclk=’1’andclk’eventthen

Ifq(3)/=’1’thenq<=a+b;

Endif;

Endprocess;

Endrtl;

答:

在a+b向q传输的过程中产生4个触发器。

程序2:

Architecturertlofexis

Signala,b:

std_logic_vector(3downto0);

Begin

Process(clk)

Variableintstd_logic_vector(3downto0);

Begin

Ifclk=’1’andclk’eventthen

Ifint(3)/=’1’thenint=:

a+b;q<=int;

Endif;

Endif;

Endprocess;

Endrtl;

答:

在int向q传输的过程中产生4个触发器。

程序3:

Architecturertlofexis

Signala,b,c,d,e:

std_logic_vector(3downto0);

Begin

Process(c,d,e,en)

Begin

Ifen=’1’thena<=c;b<=d;

Elsea<=e;

Endif

Endprocess;

Endrtl;

答:

因为b在else中没有说明,所以有1个锁存器。

10-1利用资源共享的面积优化方法对下面程序进行优化(仅要求在面积上优化)

[例10-9]

Libraryieee;

Useieee.std_logic_1164.all;

Useieee.std_logic_unsigned.all;

Useieee.std_arith.all;

Entityaddmuxis

Port(a,b,c,d:

instd_logic_vector(7downto0);

Sel:

instd_logic;

Result:

outstd_logic_vector(7downto0));

Endaddmux;

Archi

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 例题

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx

人教版小学语文五年级上册《钓鱼的启示》PPT课件.ppt

人教版小学语文五年级上册《钓鱼的启示》PPT课件.ppt