基带板原理图设计文档.docx

基带板原理图设计文档.docx

- 文档编号:28183955

- 上传时间:2023-07-09

- 格式:DOCX

- 页数:21

- 大小:217.99KB

基带板原理图设计文档.docx

《基带板原理图设计文档.docx》由会员分享,可在线阅读,更多相关《基带板原理图设计文档.docx(21页珍藏版)》请在冰豆网上搜索。

基带板原理图设计文档

基带板原理图设计文档

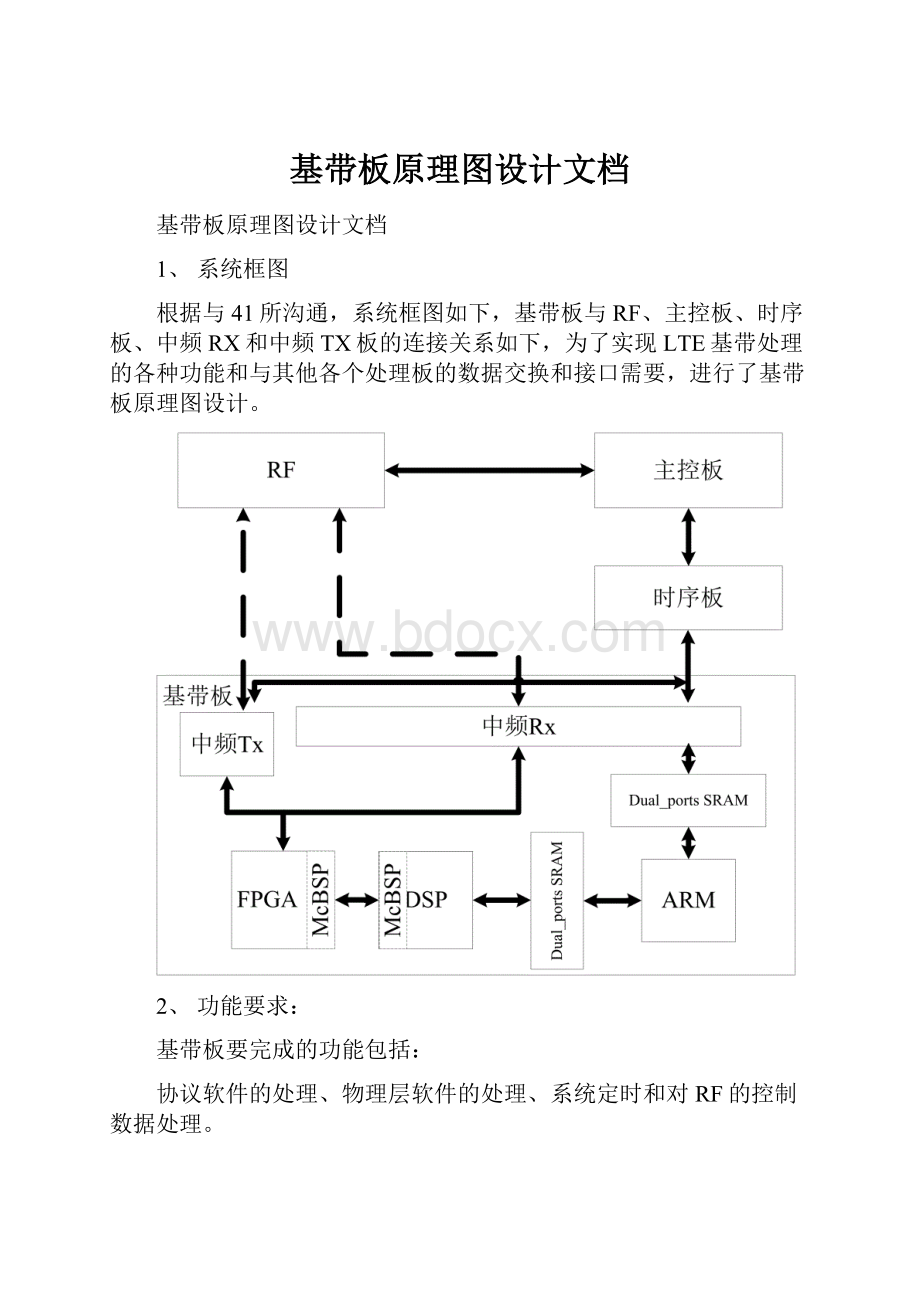

1、系统框图

根据与41所沟通,系统框图如下,基带板与RF、主控板、时序板、中频RX和中频TX板的连接关系如下,为了实现LTE基带处理的各种功能和与其他各个处理板的数据交换和接口需要,进行了基带板原理图设计。

2、功能要求:

基带板要完成的功能包括:

协议软件的处理、物理层软件的处理、系统定时和对RF的控制数据处理。

为了完成这些内容,系统包含arm、dsp和fpga三个主要器件,其中ARM完成协议软件处理、DSP负责处理物理层软件中的部分内容、FPGA完成系统定时和物理层算法的部分内容。

3、系统框图

ARM:

完成操作系统及协议、应用等功能,其支持的借口比较丰富;

接口描述:

DRAMcontroller:

DDRRAM;

SROMcontroller:

FLASH,与DSP、FPGA共用,用于boot代码的存储;

FPGA上的RAM,预留,防止协议中有算法需要用硬件实现;

双端口RAM1,用于与DSP交换数据;

双端口RAM2,用于与41所应用板交换数据;

I2C:

用于power、clk芯片的控制;

I2S:

用于codic和bluetooth;

SPI:

与FPGA间发送控制信息;

UART:

用于trace;

USB:

用于应用;

GPIO:

用于与FPGA和DSP之间产生硬件中断;

JTAG:

调试接口;

DSP:

完成物理层流程及算法;

EMIFA:

FLASH,与ARM、FPGA共用,用于boot代码的存储;

FPGA上的RAM,用于与FPGA数据交换;

双端口RAM1,用于与ARM交换数据;

DDR2:

DDRRAM;

I2C:

与FPGA相连,用于交换控制信息;

McBSP0:

用于CODIC

McBSP1:

与FPGA相连,用于交换数据信息;

RapidIO:

与FPGA相连,用于交换数据信息;

GPIO:

用于与FPGA和ARM之间产生硬件中断;

FPGA:

完成系统定时、射频数据的接收及部分物理层算法;

PCI:

用于与射频交换数据,需要确认。

4、时钟设计

LET要求的采样时钟:

122.88MHz

ARM工作时钟:

12MHz,可以通过外部的晶振提供或外部的时钟提供;

27MHz,用于其中的某些模块,可以选择是否使能;

32.768KHz,看门狗时钟;

DSP工作时钟:

CLKIN1:

33.3~66.6MHz选50MHz

CLKIN2:

12.5~26.7MHz选25MHz

EMIFCLK:

160或200MHz选200MHz

SRIOCLK:

125或156.25或312.5MHz选择125MHz备156.25MHz

系统时钟为20MHz,通过TI的CDCE937产生DSP和ARM的输入时钟

OUT

Freq

Y1

20MHz

ToFPGA

Y2

25MHz

DSPPLL1

Y3

125MHz

SRIO

Y4

50MHz

DSPPLL2

Y5

200MHz

DSP_EMIFA

Y6

12MHz

ARM

Y7

48MHz

Y8

122.88MHz

LTEtoFPGA

Y9

122.88MHz

考虑到板子单独使用和与41所接口使用的情况:

单独使用安上述设置使用

与41所接口使用时,系统时钟由41所射频板提供,时钟为122.88MHz,经过CPLD分频后得到15.36MHz的时钟,再输出到CDCE946后产生相应的其他时钟,输入为:

OUT

Freq

Y2

25MHz

DSPPLL1

Y3

125MHz

SRIO

Y4

50MHz

DSPPLL2

Y5

200MHz

DSP_EMIFA

Y6

12MHz

ARM

Y7

48MHz

SRIOCLK:

125或156.25或312.5MHz选择125MHz备156.25MHz

5电源设计

需求:

6410

电源种类:

1.2、1.8V、2.5V、3.3V

Signal

I/O

Description

Voltage

推荐值

选择值

VDDALIVE

P

Internalpowerforaliveblock

1.2

1.2

VDDARM

P

InternalpowerforARM1176coreandcache

1.1/1.2

1.2

VDDINT

P

Internalpowerforlogic

1.2

1.2

VDDMPLL

P

PowerforMPLLcore

1.2

1.2

VDDAPLL

P

PowerforAPLLcore

1.2

1.2

VDDEPLL

P

PowerforEPLLcore

1.2

1.2

VDDOTG

P

PowerforUSBOTGPHY

3.3

3.3

VDDOTGI

P

InternalpowerforUSBOTGPHY

1.2

1.2

VDDMMC

P

IOpowerforSDMMC

1.8~3.3

3.3

VDDHI

P

IOpowerforHostI/F

1.8~3.3

3.3

VDDLCD

P

IOpowerforLCD

1.8~3.3

3.3

VDDPCM

P

IOpowerforPCM(AudioI/F−I2S,AC97)

1.8~3.3

3.3

VDDEXT

P

IOpowerforexternalI/F(UART,I2C,CameraI/F,etc.)

1.8~3.3

3.3

VDDSYS

P

IOpowerforsystemcontrol.(Clock,reset,operationmode,JTAG,etc)

1.8~3.3

3.3

VDDUH

P

PowerforUSBHost

3.3

3.3

VDDADC

P

PowerforADCcoreandIO

3.3

3.3

VDDDAC

P

PowerforDACcoreandIO

3.3

3.3

VDDRTC

P

PowerforRTClogicandIO

1.8~3.0

2.5

VDDM0

P

IOpowerforMemoryPort0

1.8~3.3

3.3

VDDSS

P

IOpowerforATAIOmuxedinMEM0port

1.8~3.3

3.3

VDDM1

P

IOpowerforMemoryPort1

1.8/2.5

1.8

6455

电源种类:

1.2v、1.8v、3.3v

Signal

I/O

Description

Voltage

推荐值

选择值

VREFSSTL

A

(DVDD18/2)-VreferenceforSSTLbuffer(DDR2MemoryController).Thisinput

voltagecanbegenerateddirectlyfromDVDD18usingtwo1-kΩresistorstoform

aresistordividercircuit.

1.8V/2

VREFHSTL

A

(DVDD15/2)-VreferenceforHSTLbuffer(EMACRGMII).VREFHSTLcanbe

generateddirectlyfromDVDD15usingtwo1-kΩresistorstoformaresistor

dividercircuit.

1.5V/2

DVDDR

S

1.8-VI/Osupplyvoltage.(SRIOregulatorsupply)

1.8V

1.8

AVDDA

A

SRIOanalogsupply:

1.25-VI/Osupplyvoltage(-1000and-1200devices)

1.2-VI/Osupplyvoltage(-850and-720devices).

Donotusecoresupply.

1.25V

1.2V

1.2

AVDLL1

A

1.8-VI/Osupplyvoltage.

1.8V

1.8

AVDLL2

A

1.8-VI/Osupplyvoltage.

1.8V

1.8

DVDDRM

S

SRIOinterfacesupply:

1.25-Vcoresupplyvoltage(-1000and-1200devices)

1.2-Vcoresupplyvoltage(-850and-720devices).

thesourceforthissupplyvoltagemustbethesameasthatofCVDD

1.25V

1.2V

1.2

DVDD12

S

MainSRIOsupply:

1.25-VI/Osupplyvoltage(-1000and-1200devices)

1.2-VI/Osupplyvoltage(-850and-720devices).

Donotusecoresupply.

1.25V

1.2V

1.2

AVDDT

A

SRIOterminationsupply:

1.25-VI/Osupplyvoltage(-1000and-1200devices).

1.2-VI/Osupplyvoltage(-850and-720devices).

Donotusecoresupply.

1.25V

1.2V

1.2

DVDD15

S

1.8-Vor1.5-VI/OsupplyvoltagefortheRGMIIfunctionoftheEMAC.

1.8V

1.5V

1.8

DVDD18

S

1.8-VI/Osupplyvoltage(DDR2MemoryController)

1.8V

1.8

DVDD33

S

3.3-VI/Osupplyvoltage

3.3V

3.3

CVDD

S

1.25-Vcoresupplyvoltage(-1000and-1200devices).

1.2-Vcoresupplyvoltage(-850and-720devices).

1.25V

1.2V

1.2

FPGA

Signal

I/O

Description

Voltage

VCCAUX

2.5

VCCINT

1.0

VCCO

电源选择:

FPGA:

VCCAUX

2.5

3A

TPS74401

VCCINT

1.0

10A

PTH04T240W

VCCO

3.3

10A

PTH04T240W

1.8

6A

PTH08T230W/TPS51100

DSP、ARM

1.2

TPS65051

1.8

PTH08T230W

3.3

PTH04T240W

1.25

PTH04T240W

6、FPGA模式选择:

ConfigurationMode

M[2:

0]

BusWidth

CCLKDirection

MasterSerial

000

1

Output

MasterSPI

001

1

Output

MasterBPI-Up

010

8,16

Output

MasterBPI-Down

011

8,16

Output

MasterSelectMAP

100

8,16

Output

JTAG

101

1

Input(TCK)

SlaveSelectMAP

110

8,16,32

Input

SlaveSerial

111

1

Input

我们系统中选择JTAG或SlaveSelectMAP,所以M2固定为高,M[1:

0]为01则为JTAG,为10即为SlaveSelectMAP,为11则为slaveserial

SlaveSelectMAP模式下:

可以设置为DSPboot还是armboot,

需要的信号:

CCLK:

写使能

CS_B:

片选

RDWR_B:

GPIO

slaveserial模式下:

可以设置为DSPboot还是armboot,

CCLK:

GPIO

D_IN:

GPIO

7、DSP设置:

AEA19/BOOTMODE3

AEA18/BOOTMODE2

AEA17/BOOTMODE1

AEA16/BOOTMODE0

设置

Boot模式:

0000-Noboot(defaultmode)

0001-Hostboot(HPI)

0010-Reserved

0011-Reserved

0100-EMIFA8-bitROMboot

0101-MasterI2Cboot

0110-SlaveI2Cboot

0111-Hostboot(PCI)

1000thru1111-SerialRapidI/Obootconfigurations

CFGGP[2:

0]pinsmustbesetto000bduringresetforproperoperationofthePCIbootmode.

AEA15/AECLKIN_SEL

0

EMIFA输入时钟选择

0-AECLKIN(defaultmode)

1-SYSCLK4(CPU/x)ClockRate.TheSYSCLK4clockrateissoftwareselectableviatheSoftwarePLL1Controller.Bydefault,SYSCLK4is

selectedasCPU/8clockrate.

AEA14/HPI_WIDTH

1

HPI总线宽度选择

0-HPIoperatesasanHPI16(default).(HPIbusis16bitswide.HD[15:

0]

pinsareusedandtheremainingHD[31:

16]pinsarereservedpinsinthe

Hi-Zstate.)

1-HPIoperatesasanHPI32.

AEA13/LENDIAN

设置

DeviceEndianmode(LENDIAN)

0-SystemoperatesinBigEndianmode

1-SystemoperatesinLittleEndianmode(default)

AEA12/UTOPIA_EN

1

UTOPIAEnablebit(UTOPIA_EN)

UTOPIAperipheralenable(functional)

0-UTOPIAdisabled;EthernetMAC(EMAC)andMDIOenable(default).

EMAC/MDIOconfiguration(interface)[MII,RMII,GMIIorthestandaloneRGMII]iscontrolledbytheMACSEL[1:

0]bits.

1-UTOPIAenabled;EMACandMDIOdisabled[exceptwhentheMACSEL[1:

0]bits=11then,theEMAC/MDIORGMIIinterfaceisstillfunctional].

AndifMACSEL[1:

0]=11,theRGMIIstandalonepinfunctionscanbeused.

AEA11

1

必须接1k下拉电阻

AEA10/MACSEL1

AEA9/MACSEL0

EMAC/MDIOinterfaceselectbits

AEA8/PCI_EEAI

0

AEA8:

PCIauto-initializationviaexternalI2CEEPROM

IfthePCIperipheralisdisabled(PCI_ENpin=0),thispinmustnotbe

pulledup.

0-PCIauto-initializationthroughI2CEEPROMisdisabled(default).

1-PCIauto-initializationthroughI2CEEPROMisenabled.

AEA7

AEA6/PCI66

0

PCIFrequencySelection(PCI66)

0-PCIoperatesat33MHz(default).

1-PCIoperatesat66MHz.

IfthePCIperipheralisdisabled(PCI_EN=0),thispinmustnotbe

pulledup.

AEA5/MCBSP1_EN

0

McBSP1Enablebit(MCBSP1_EN)

0-GPIOpinfunctionsenabled(default).

1-McBSP1pinfunctionsenabled.

ASEYAS4C/LKOUT_EN

0

SYSCLKOUTEnablepin(SYSCLKOUT_EN)

0-GP[1]pinfunctionoftheSYSCLK4/GP[1]pinenabled(default).

1-SYSCLK4pinfunctionoftheSYSCLK4/GP[1]pinenabled.

AEA3

1

SRIO使能:

上拉

SRIO不使能:

下拉

AEA2/CFGGP2

AEA1/CFGGP1

AEA0/CFGGP0

000

ConfigurationGPI(CFGGP[2:

0])(AEA[2:

0])

Thesepinsarelatchedduringresetandtheirvaluesareshowninthe

DEVSTATregister.Thesevaluescanbeusedbysoftwareroutinesforboot

operations.

ABA1/EMIFA_EN

1

使能

ABA0/DDR2_EN

1

使能

左

DSP_EMIFA_BA0

DDR2_EN

1

DSP_EMIFA_ADD19

BOOTMODE3

0

DSP_EMIFA_ADD8

PCI_EEAI

0

右

DSP_EMIFA_ADD17

BOOTMODE1

0

S12

左

DSP_EMIFA_ADD18

BOOTMODE2

0

DSP_EMIFA_ADD15

AECLKIN_SEL

0

DSP_EMIFA_ADD14

HPI_WIDTH

1

DSP_EMIFA_ADD13

LENDIAN

0

DSP_EMIFA_ADD12

UTOPIA_EN

0

DSP_EMIFA_ADD11

0

DSP_EMIFA_ADD10

MACSEL1

0

DSP_EMIFA_ADD9

MACSEL0

0

右

DSP_EMIFA_ADD7

S9/S11

左

DSP_EMIFA_ADD6

PCI66

0

DSP_EMIFA_ADD16

BOOTMODE0

0

DSP_EMIFA_ADD5

MCBSP1_EN

1

DSP_EMIFA_ADD4

SYSCLKOUTEn

0

DSP_EMIFA_ADD3

SRIO使能

1

DSP_EMIFA_ADD2

CFGGP2

0

DSP_EMIFA_ADD1

CFGGP1

0

DSP_EMIFA_ADD0

CFGGP0

0

右

DSP_EMIFA_BA1

EMIFA_EN

1

S8/S10

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基带 原理图 设计 文档

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《贝的故事》教案4.docx

《贝的故事》教案4.docx