Design Entry CIS使用指南.docx

Design Entry CIS使用指南.docx

- 文档编号:27974750

- 上传时间:2023-07-07

- 格式:DOCX

- 页数:22

- 大小:415.62KB

Design Entry CIS使用指南.docx

《Design Entry CIS使用指南.docx》由会员分享,可在线阅读,更多相关《Design Entry CIS使用指南.docx(22页珍藏版)》请在冰豆网上搜索。

DesignEntryCIS使用指南

DesignEntryCIS使用指南

e栈2010-03-1815:

50:

45阅读981评论0 字号:

大中小 订阅

DesignEntryCIS(Capture和CaptureCIS)是国际上电子工程师最受欢迎的原理图设计工具,它具有使用方便和美观特点。

完美的DesignEntryCIS与Cadence公司功能强大的Allegro简直是天作之合。

Cadence软件主要包括原理图设计工具DesignEntryCIS和DesignEntryHDL(使用较少),焊盘设计工具PadDesigner和PCB设计工具PCBEditor。

1.工程管理

1.1启动软件

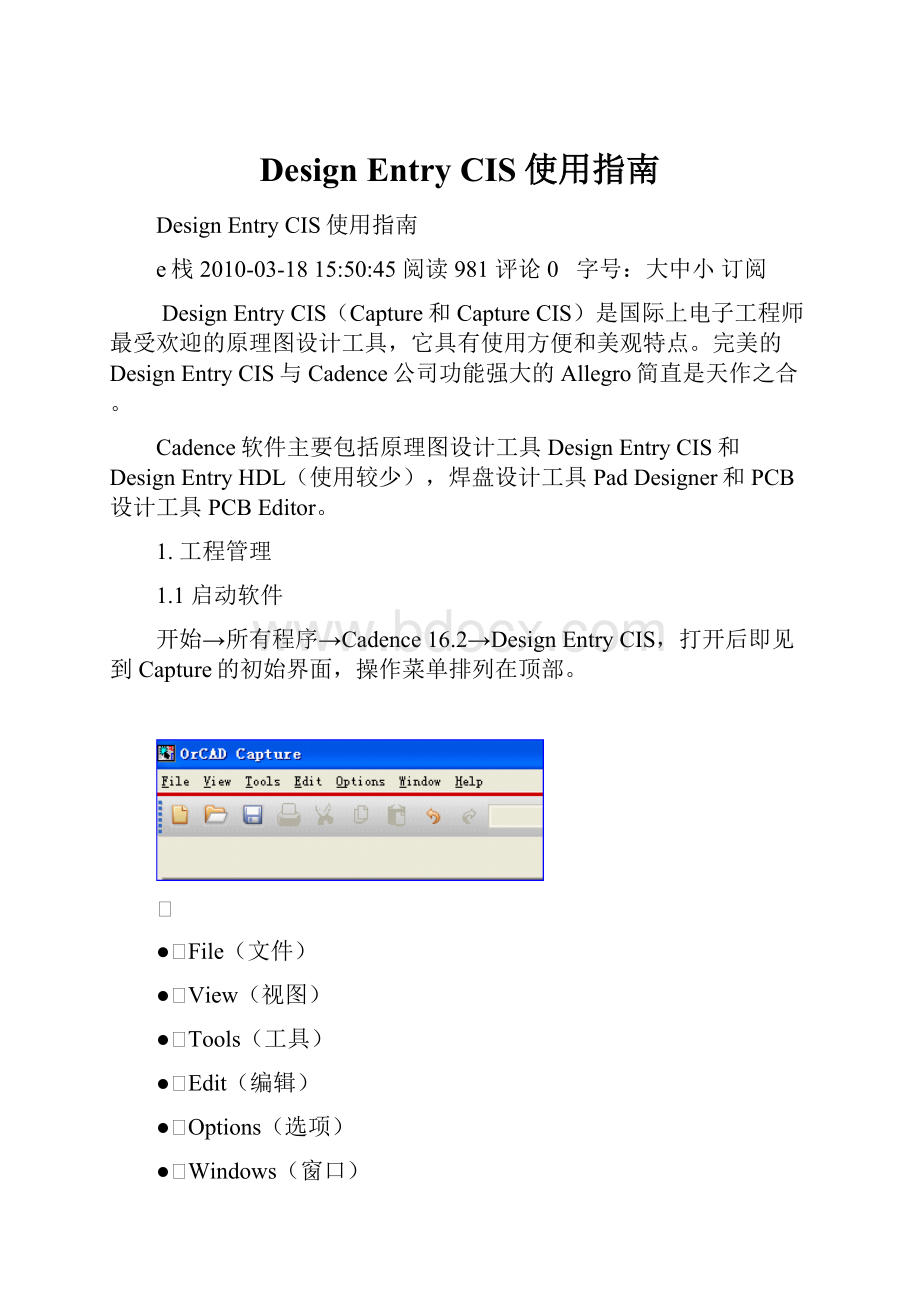

开始→所有程序→Cadence16.2→DesignEntryCIS,打开后即见到Capture的初始界面,操作菜单排列在顶部。

●File(文件)

●View(视图)

●Tools(工具)

●Edit(编辑)

●Options(选项)

●Windows(窗口)

●Help(帮助)

1.2创建工程

File→New→Project

●给工程命名

在Name下方空白处输入工程名字。

●点选Schematic

●定位工程存放路径

点Browse,选择工程存放路径,点OK完成。

1.3打开工程

File→Open→Project,选择工程存放路径和工程名,点打开。

1.4工程子项

打开工程后,工程包含以下选项,DesignResources(设计资源),Output(输出)和ReferencedProjects(参考工程)。

1.4.1设计资源

✍dsn(设计)

●SCHEMATIC

●DesignCache

✍Library(原理图库)

1.4.2输出

●Drc(规则检查输出,只有规则检查后才会有)

●Bom(材料表单,只有生成材料表单后才有)

●NetList(网络表,只有生成网络表后才有)

1.4.3参考工程

2.原理图参数设置

2.1图纸版面设置

Options→Designtemplate→PageSize

2.1.1页面单位

●Inches(英制)

●Millimeters(公制)

2.1.2页面尺寸

●Inches版面

A/B/C/D/E/Custom

●Millimeters版面

A4/A3/A2/A1/A0/Custom

2.2栅格设置

Options→Designtemplate→GridReference

2.2.1水平栅格设置

水平方向栅格设置

如果设置为millimeter的A4,则Width中输入2,否则打印出来的原理图四周的字母很大。

2.2.2竖直栅格设置

竖直方向栅格设置

一般采用默认的设置。

如果设置为millimeter的A4,则Width中输入2,否则打印出来的原理图四周的字母很大。

2.3字体设置

Options→Designtemplate→Fonts,分别对以下各项进行设置(一般采用默认设置)。

●Alias

●Bookmark

●BorderText

●Hierarchical

●NetName

●Off-Page

●Part

●PartValue

●PinName

●PinNumber

●Port

●PowerText

●Property

●Text

●TitleBlock

2.4颜色设置

Options→Preference→Colors/Print,分别对各项进行设置(一般采用默认值),可以对器件管脚数设置为蓝色。

2.5标题栏设置

Options→Designtemplate→TitleBlock,输入公司名和标题及版本等。

2.6自动备份设置

Options→Autobackup,设置间隔时间、备份数目和存放目录。

3.原理图库管理

3.1直接新建元件

3.1.1创建新库

File→New→Library,那么在Library目录下出现一个名为library1.obl的库。

添加新元件到库中

●右击library1.obl,选择NewPart。

●Name栏输入元件名字

●PartReferencePrefix栏输入元件编号前缀

●PCBFootprint栏中输入封装类型

●PartsperPkg栏中输入封装中包括的元件部分数

●PackageType中选择Homogenenous(各部分相同)/Heterogeneous(各部分不同)

●PartNumbering中选择选择Alphabetic(各部分按字母编号)/Numeric(各部分按数字编号),如U1A,U1B,U1-1,U1-2等。

完成上述设定后点击OK。

3.1.2绘制元件外形

Place→Rectangle(或点击工具栏图标),调整外形框的大小。

3.1.3添加管脚

●Place→Pin

●Name栏中输入管脚名字

●Number栏中输入管脚号

待所有的管脚输入完成后,File→save,在文件名栏输入库名,选择存放路径,点保存确定。

其他元件同样照此进行。

3.1.4阵列式放置管脚

如果管脚名呈递增规律,那么采用阵列式放置管脚。

点击左边Placepinarray的工具栏图标,出现阵列放置对话框。

●StartingName(开始名字)

●StartingNumber(开始管脚标号)

●NumberofPins(一次放置的管脚数目)

●Increment(管脚标号增加数目)

●PinSpacing(管脚间距)

设置完上述参数后,点OK,那么一排管脚被放置。

3.2用电子表格新建元件

File→New→Library,那么在Library目录下出现一个名为library1.obl的库。

添加新元件到库中,右击library1.obl,选择NewPartFromspreadsheet。

在Partname中输入元件名字,NoofSection表示分割元件的部分个数。

PartRefPrefix中输入元件名称的前缀。

PartNumbering中选择数字或字母。

在表格中输入各参数后,点save保存。

3.3修改元件

●如果是用直接方式创建的元件,直接在库中双击元件后,对个管脚进行修改。

●如果是用电子表格创建的元件,在库中右击元件,选择SplitPart后,对各参数进行修改。

3.4添加原理图库

如果采用现有自创的原理图库,可以右击Library,点AddFile,找到库存放的路径及库名,点打开添加。

3.5删除原理图库

点击Library下的库,按Delete键删除或右击鼠标,选Cut删除。

3.6capture库

●AMPLIFIER.OLB存放模拟放大器IC。

●ARITHMETIC.OLB存放逻辑运算IC,。

●ATOD.OLB存放A/D转换IC。

●BUSDRIVERTRANSCEIVER.OLB存放汇流排驱动IC。

●CAPSYM.OLB存放电源,地,输入输出口,标题栏等。

●CONNECTOR.OLB存放连接器等。

●COUNTER.OLB存放计数器IC。

●DISCRETE.OLB存放分立式元件。

●DRAM.OLB存放动态存储器。

●ELECTROMECHANICAL.OLB存放马达,断路器等电机类元件。

●FIFO.OLB存放先进先出资料暂存器。

●FILTRE.OLB存放滤波器类元件。

●FPGA.OLB存放可编程逻辑器件。

●GATE.OLB存放逻辑门(含CMOS和TLL)。

●LATCH.OLB存放锁存器。

●LINEDRIVERRECEIVER.OLB存放线控驱动与接收器。

●MECHANICAL.OLB存放机构图件。

●MICROCONTROLLER.OLB存放单晶片微处理器。

●MICROPROCESSOR.OLB存放微处理器。

●MISC.OLB存放杂项图件。

●MISC2.OLB存放杂项图件。

●MISCLINEAR.OLB存放线性杂项图件(未分类)。

●MISCMEMORY.OLB存放记忆体杂项图件(未分类)。

●MISCPOWER.OLB存放高功率杂项图件(未分类)。

●MUXDECODER.OLB存放解码器。

●OPAMP.OLB存放运放。

●PASSIVEFILTER.OLB存放被动式滤波器

●PLD.OLB存放可编程逻辑器件。

●PROM.OLB存放只读记忆体运算放大器。

●REGULATOR.OLB存放稳压IC。

●SHIFTREGISTER.OLB存放移位寄存器。

●SRAM.OLB存放静态存储器。

●TRANSISTOR.OLB存放晶体管。

4.页面操作

4.1页面添加

右击dsn下的SCHEMATIC1,点NewPage,添加新页。

然后右击该目录选Rename给目录更名。

4.2页面编号

右击新添加的页面,选择Rename,输入编号及名字。

编号以01开始依次递增。

01页名Title(标题),02页名为Index(目录)。

后面是按原理图实现的功能依次递增分的页。

Title页绘制设计的整体框图。

三页以上的原理图必须有目录。

Index页包含历史变更和各功能模块的编号。

目录以文本形式列明模块名(与标题栏的模块名相同)并简述每页图纸所实现的功能,并列明页码。

目录位于整体框图的下方。

当然上面是针对平坦式电路,层次式电路则不用添加Title和Index。

4.3页面删除

点击页面,按Delete键删除或右击鼠标,选Cut删除。

5.基本界面操作

5.1放大原理图

View→Zoom→In

5.2缩小原理图

View→Zoom→Out

6.常用快捷键

●I放大

●O缩小

●F1帮助

7.添加元件

7.1添加原理图库

点击Library下的AddLibray符号,选择库存放的路径和库名后点打开。

7.2工具栏图标

✍工具栏图标第一列

●Placewire

●Placebus

●Placebusentry

●Placeground

●Placeport

●Placeoff-pageconnector

●Placeline

●Placerectangle

●Placearc

✍工具栏第二列

●Placenetaliax

●Placejunction

●Placepower

●Placehierarchicalblock

●Placenoconnect

●Placepolyline

●Placeellipse

●Placetext

7.3放置元器件

Place→Part或直接按P键,在Libraries下选择库名,在PartList中双击元件,那么选中的元件粘在鼠标上,在放置的地方单击鼠标完成。

7.4元件的鼠标右键操作

点击元件,右击鼠标,会出现很多选项。

●MirrorHorizotally(水平镜像)

●MirrorVertically(竖直镜像)

●Rotate(旋转)

●EditPropertities(编辑属性)

●EditPart编辑器件

●Copy(拷贝)

●Cut(剪切)

●Delete(删除)

8.连线

8.1导线连接

Place→wire或点击右端工具栏图标,连接后管脚上的小框消失,这是Capture的独到之处。

8.2总线连接

放置总线的命令是Place→Bus或点击右端工具栏图标,按住shit键可以画出斜线。

8.3总线支线

Place→BusEntry可以放置一小段斜线,即总线支线。

8.4未连接管脚处理

Place→NoConnect,在未连接管脚上放置“×”符号。

9.添加信号名

9.1全局信号

●电源

点击右端的Placepower工具栏图标,选择自己爱好的电源符号(遵循规范,详见《Cadence电路设计规范》),然后点击电源符号,在Value中输入电源标号后点击OK完成。

●地

点击右端的Placeground工具栏图标,选择自己爱好的地符号(遵循规范,详见《Cadence电路设计规范》),然后点击地符号,在Value中输入地标号后点击OK完成。

9.2添加网络名

点击右端的Placenetaliax工具栏图标,然后点击网络符号,在Value中输入网络标号后点击OK完成。

9.3添加端口

点击右端的Placeport工具栏图标,修改端口的Value值后点击OK完成。

9.4添加页连接符

点击右端的Placeoff-pageconnector工具栏图标,然后点击页连接符号,在Value中输入网络标号后点击OK完成。

页连接符只有左右之分,无上下之形式。

切换到工程界面,点击dsn然后点U?

图标,选择AddIntersheetReferences进入IntersheetReferences后,XOffset中输入页连接符离网络标号的X距离,默认为80,通常设置为50或60。

在Prefix(前缀)中输入“{”符号,在Suffix(后缀)中输入“}”符号。

10.整体编辑器件

选中几个器件,点右键,选择EditProperties,给所有器件输入PCBFootprint和Value值。

电阻和电容通常采用此操作,这是Capture的独到之处。

11.添加文本

点击右端的Placetext工具栏图标,输入文字内容,点击Color的下拉菜单,选择喜欢的颜色。

然后点击Font下的Change后,选择字体、字形和大小,点击OK完成。

12.创建层次式电路

如果电路层次复杂,建议采用层次式电路设计。

目前在电路设计中比较流行“自上而下”的设计方法,从根层开始看图,线路清晰。

对于平坦式电路,须在开始页上画出整体框图。

12.1放置层次块

Place→HierarchicalBlock或点击右端工具栏图标,弹出PlaceHierarchicalBlock对话框。

在Reference文本框输入名字,在ImplementationType栏中选择SchematicView(与电路图连接),在Implementationname文本框中输入内层电路图名,指定存盘路径(不指定也可),点击OK完成。

12.2添加层次端口

选中层次块,Place→HierarchicalPIN,在name栏中输入端口名字,Type下拉表中选择引脚类型。

13.定义Room属性

点击元件,右击鼠标,选择Editproperties,弹出Editproperties窗口,向右或向下拉动滑动条,找到ROOM,在ROOM后空白栏输入ROOM名字。

14.添加页属性

单击NewColomn或Row,弹出对话框,在Name栏输入名字Page,点Apply。

在EditEditproperties对话框下出现新选项Page,在Page中输入页号“1”。

这主要为以后按页摆放器件做好准备。

15.建立差分对

Tools→CreatDifferentialPair,弹出以下对话框。

在DIffPairName空白栏输入差分对名字,在左侧选择网络名,点Creat创造差分对。

16.原理图模块元件化

点击dsn后,Tools→GeneratePart,在Partname中输入要生成的元件名,点OK确定完成。

元件化的原理图当做元件使用,通常使用频率高的模块可以生成元件来使用。

17.文件输出

17.1DRC输出

切换到工程,点击dsn,然后点击顶部的Designrulescheck工具栏图标确定后,在Outputs生成.drc文件。

17.2BOM表输出

切换到工程,点击dsn,然后点击顶部的Billofmaterials带“√”工具栏图标确定后

vScope

●Processentiredesign生成整个设计的元件清单

●Processslection生成所选部分元件清单

vMode

●Useinstances使用当前属性

●Useoccurrences使用事件属性

vLineItemDefinition

●Placeeachpartentryonseparateline元件清单中每个元件信息占一行。

●IncludeFile元件清单中加入其它文件。

在Outputs下生成.bom文件。

17.3网络表输出

切换到工程,点击dsn,然后点击顶部的Creatnetlist带“N”字样的工具栏图标确定后,

●选择CreatPCBEditorNetlist,定位NetlistFiles的位置。

●选择CreatorUpdatePCBEditorBoard,定位InputBoard和OutputBoard的位置,点击确定后,在Outputs生成psxnet.dat,pstxprt.dat和pstchip.dat三个文件。

生成网络表后,原理图设计工程师(大公司一般原理图设计和PCB设计分开)的使命暂告一段落,接下去就是把网络表交付LAYOUT

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Design Entry CIS使用指南 CIS 使用指南

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx