应用电子技术实训.docx

应用电子技术实训.docx

- 文档编号:27913736

- 上传时间:2023-07-06

- 格式:DOCX

- 页数:14

- 大小:225.06KB

应用电子技术实训.docx

《应用电子技术实训.docx》由会员分享,可在线阅读,更多相关《应用电子技术实训.docx(14页珍藏版)》请在冰豆网上搜索。

应用电子技术实训

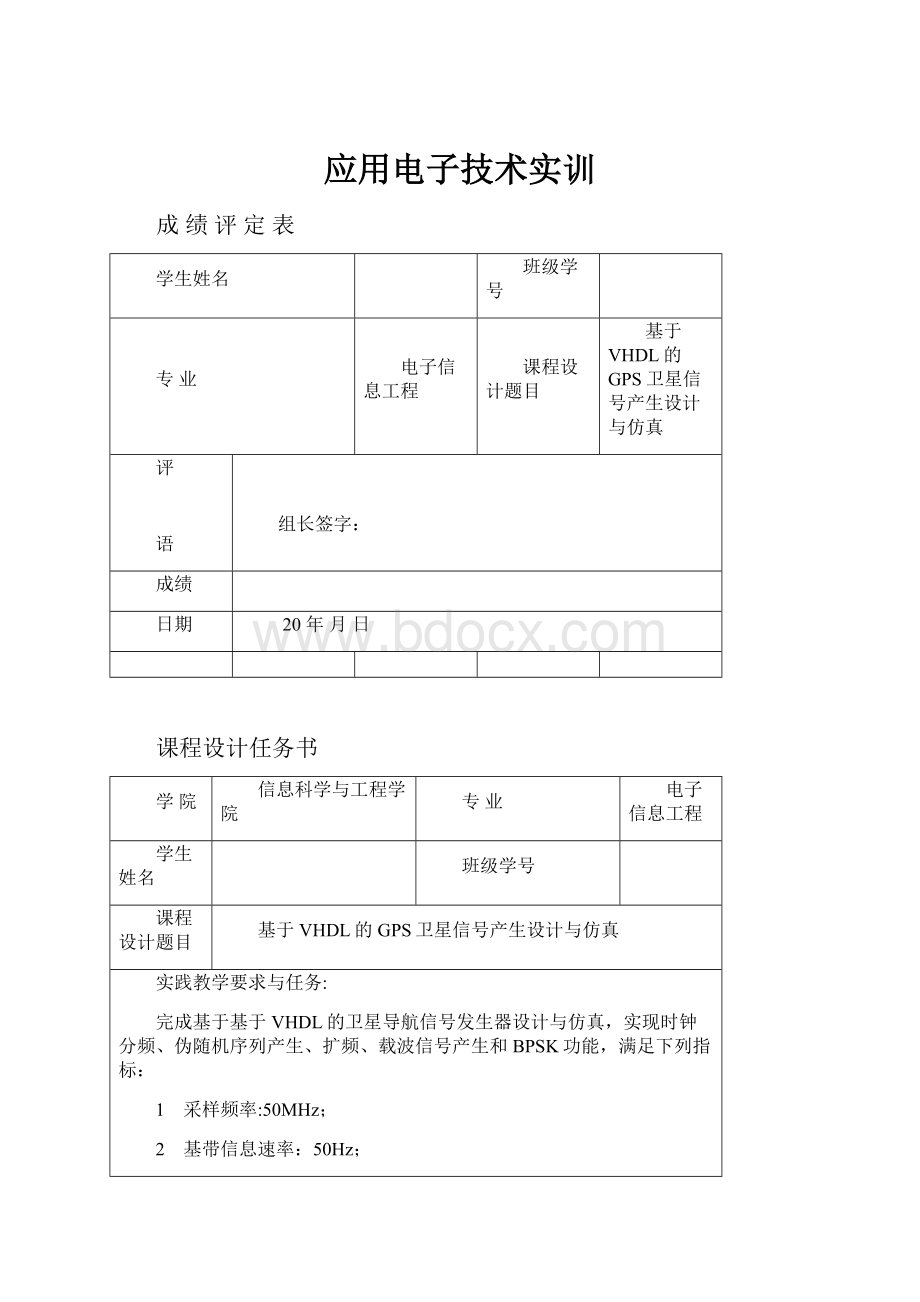

成绩评定表

学生姓名

班级学号

专业

电子信息工程

课程设计题目

基于VHDL的GPS卫星信号产生设计与仿真

评

语

组长签字:

成绩

日期

20年月日

课程设计任务书

学院

信息科学与工程学院

专业

电子信息工程

学生姓名

班级学号

课程设计题目

基于VHDL的GPS卫星信号产生设计与仿真

实践教学要求与任务:

完成基于基于VHDL的卫星导航信号发生器设计与仿真,实现时钟分频、伪随机序列产生、扩频、载波信号产生和BPSK功能,满足下列指标:

1 采样频率:

50MHz;

2 基带信息速率:

50Hz;

3 伪随机序列速率:

1MHz;

4 载波频率:

5MHz。

工作计划与进度安排:

1~4学时:

布置题目,查找资料;

5~8学时:

学习ISE开发软件和modelsim仿真软件应用;

9~12学时:

进行基于VHDL的卫星导航信号发生器设计与仿真;

13~16学时:

调试程序,撰写报告。

指导教师:

201年月日

专业负责人:

201年月日

学院教学副院长:

201年月日

摘要

全球定位系统(GPS)可以向全球用户提供位置、速度和时间信息,在航空航天、海上及陆地等许多领域,特别是军事领域得到了广泛的应用,成为一种主要的导航手段。

在理论研究和分析的基础上,设计了基于GPS信号的伪卫星发射器。

用VHDL语言与CPLD芯片完成了C/A码的设计以及与导航电文叠加的合成码设计,用BPSK调制方式将合成码调制到载波上,实现了发射器的整体功能。

GPS系统采用典型的CDMA体制,这种扩频调制信号具有低截获概率特性,系统以码分多址形式区分各卫星信号。

目前GPS系统是部分公开的,采用的伪码有C/A码、P(Y)码等。

该系统主要利用直接序列扩频调制技术,采用1.023MHz(C/A码)和10.23MHz(P(Y)码)两种速率的伪随机码在L1和L2频率上调制发射50Hz的导航定位信息,L1和L2频率在和平时期是确知的,分别为1575.42MHz和1227.6MHz,其中L1频率上的信号是非平衡QPSK调制,其I通道上的伪码序列是C/A码,L2频率上采用P码扩频的BPSK调制。

本设计是用ISE10.2软件完成L2频率上BSPK调制的FPGA实现。

采样频率50MHz;基带信息速率50Hz;伪随机序列速率1MHz;载波频率5MHz。

关键词:

GPS、C/A码、BPSK、VHDL

摘要I

1.课程设计目的及要求1

1.1设计目的1

1.2设计要求1

2.开发环境1

2.1VHDL1

2.2XilinxISE12.22

2.3modelsim仿真3

3.开发过程4

3.1信号发生器工作原理4

3.1.1GPS信号简介4

3.1.2C/A码发生器5

3.2关键模块设计6

3.2.1分频模块设计6

3.2.2GOLD码产生模块7

3.2.3DDSIP核7

3.2.4延时模块8

3.2.5BPSK调制信号产生模块8

4.仿真结果8

4.1单个模块仿真8

4.1.1分频器8

4.1.2GOLD码产生器9

4.1.3DDSIP核9

4.1.4延时模块10

4.2整体仿真10

总结11

参考文献12

1.课程设计目的及要求

1.1设计目的

1)掌握GPS系统BPSK调制的理论,熟悉C/A码的产生方式及作用,学会时钟频率的选择。

2)学会使用ISE.12.0的FPGA设计及modelsim的软件仿真。

学会使用VHDL语言的设计和TestBench的测试。

1.2设计要求

1)完成基于VHDL的卫星导航信号发生器设计:

采样频率50MHz;基带信息速率50Hz;伪随机序列速率1MHz;载波频率5MHz。

2)基于设计进行modelsim仿真调试,修正。

2.开发环境

2.1VHDL

VHDL语言的英文全名是VeryHighSpeedIntegratedCircuitHardwareDescriptionLanguage,即超高速集成电路硬件描述语言,是一种全方位的硬件描述语言,具有极强的描述能力,能支持系统行为级、寄存器传输级和逻辑门级三个不同层次的设计,因此在实际应用中越来越广泛。

HDL发展的技术源头是:

在HDL形成发展之前,已有了许多程序设计语言,如汇编、C、Pascal、Fortran、Prolog等。

这些语言运行在不同硬件平台和不同的操作环境中,它们适合于描述过程和算法,不适合作硬件描述。

CAD的出现,使人们可以利用计算机进行建筑、服装等行业的辅助设计,电子辅助设计也同步发展起来。

在从CAD工具到EDA工具的进化过程中,电子设计工具的人机界面能力越来越高。

在利用EDA工具进行电子设计时,逻辑图、分立电子原件作为整个越来越复杂的电子系统的设计已不适应。

2.2XilinxISE12.2

ISE®12设计套件是面向Virtex®-6和Spartan®-6FPGA系列并针对生产力精心优化的工具套件,在降低功耗与成本方面取得了突破性进展。

作为业界唯一一款特定领域的设计套件,赛灵思最新版本的发布,是这一行业屡获殊荣的软件不断发展和演进的又一重要一步,它将进一步提高设计生产力和系统性能,使逻辑、嵌入式、数字信号处理(DSP)和系统设计人员能够更轻松地推出更复杂的创新型可编程电子产品,从而加速产品上市进程并提升产品质量。

智能功耗优化

降低数字设计功耗是标准的系统要求,随着半导体工艺技术进一步向小型化发展,降低功耗的需求也更加明显。

现实情况是,此前用来构建系统的传统设计或IP模块几乎没有专门为针对降低功耗而设计的,同时面对市场压力,设计人员也没有时间来修改RTL代码以降低功耗。

因此,目前部署的大部分设计都存在动态功率效率低下的问题。

"时钟门控"用于降低ASIC和FPGA动态功耗的价值已为人们所熟知,但是,工程师很少有时间手动采用时钟门控技术,特别是在设计日趋复杂、产品上市时间日益缩短的情况下更是如此。

ISE12设计套件在这种利用率偏低的时钟门控技术的基础上,推出了首款"智能"FPGA时钟门控技术,可在综合后自动实施精细粒度功率优化。

这种最新优化技术会中止逻辑切片(slice)级上不必要的逻辑和互联转换活动,而无须关闭整个时钟网络就能节省大量电力。

这种自动化进程首先采用独特的算法全面分析设计中的顺序元件(主要是寄存器),检测不改变最后逻辑的转换。

软件随后创建门控信号,取消不必要的转换,并将其连接至Virtex-6和Spartan-6中的大量时钟启用(CE)引脚。

由于与FPGA架构(slice)中的基本设备群(cluster)互联并控制少量的寄存器,因此每个CE都理想地适用于功率优化。

优化归类到8位(或16位、32位等)寄存器构成的设计总线,而后可映射至一个或多个逻辑切片上,最大限度地提高软硬件实施方案的利用率。

ISE12设计套件是行业唯一一款提供时钟门控优化的工具,时钟门控优化与布局布线算法相结合,既不会改变(再合成)设计的原始逻辑或处理功能,又不会改变时钟布局。

优化创建的更多逻辑平均只增加2%的LUT,对大多数设计的时序没有影响。

FPGA的时钟门控技术并不是新的概念,但采用智能化精细粒度时钟门控技术则是赛灵思FPGA所特有的,有望通过赛灵思最新一代架构将动态功耗降低达30%之多,从12.1版本和12.2版本分别开始支持Virtex-6FPGA和Spartan-6FPGA.

平衡功耗、成本和生产力

ISE12设计套件有望成为近十年来最受欢迎的产品。

在要求嵌入式、DSP和逻辑/连接领域设计人员降低新一代产品功耗、提升性能并降低系统成本的推动下,ISE12设计套件应运而生。

ISE12能通过在降低功耗与成本方面的软件创新技术让Virtex-6和Spartan-6器件的功能发挥到极致,并同时提升整体设计效率,从而帮助设计人员有效平衡上述要求。

ISE与赛灵思的目标设计平台战略相结合后的潜在优势极其深远,它将为更多软硬件设计人员提供更高级的FPGA技术。

2.3modelsim仿真

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。

它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

3.开发过程

3.1信号发生器工作原理

3.1.1GPS信号简介

GPS系统采用典型的CDMA体制,这种扩频调制信号具有低截获概率特性,系统以码分多址形式区分各卫星信号。

目前GPS系统是部分公开的,采用的伪码有C/A码、P(Y)码等。

该系统主要利用直接序列扩频调制技术,采用1.023MHz(C/A码)和10.23MHz(P(Y)码)两种速率的伪随机码在L1和L2频率上调制发射50Hz的导航定位信息,L1和L2频率在和平时期是确知的,分别为1575.42MHz和1227.6MHz,其中L1频率上的信号是非平衡QPSK调制,其I通道上的伪码序列是C/A码,其Q通道的伪码序列是P码;L2频率上采用P码扩频的BPSK调制。

图3-1GPS卫星信号产生机理

GPS信号采用L波段作为载波,主要是因为其独有的频段特性:

L波段的频率占用率低于其他频段,不易发生频率冲突,利于导航定位测量;GPS卫星采用直接序列扩频通信技术发送导航电文,信号带宽高达20MHz左右,在占用率低的L波段上,易于传送扩频后的宽带信号;卫星在约20000km的高空运行,卫星信号的载波频率越高,多普勒频移就越大,有利于测量用户的行驶速度;GPS系统使用L波段的信号工作波长为19cm和24cm,降低了信号在传输过程中的大气衰减,利于用较经济的接收设备测量GPS信号。

3.1.2C/A码发生器

图3-2C/A码产生(GPS-ICD-200)

C/A码是一种Gold组合码,是由两个10级移位寄存器产生的m序列G1和G2模2和的复合码,图2.1.2.2所示。

可以表示为:

G(t)=G1(t)⊕G2(t+Niτ0),式中τ0为码元对应的时间1/1023ms,Ni为G1和G2间相位偏置的码元数。

每一颗GPS卫星所对应产生的C/A码取决于不同的G2输出组合,表2.1.2.1中列出了G2输出位组合产生的对应于每一颗GPS卫星的C/A码。

C/A码的码速率为1.023MHz,周期为1ms,码长为1023bit。

由于其周期短,速率低,易于被接收机相关捕获,但也造成了测量误差大的不良影响,因此C/A码也被称为粗测量码。

3.2关键模块设计

图3-3信号发生器整体结构示意图

3.2.1分频模块设计

本设计所有时钟都采用同一个时钟源,时钟频率选择与采样频率相100MH.C/A码的输入时钟频率为1KHZ.因此分频模块要达到100MHZ/1KHZ=100000分频的效果。

由于C/A码模块设计的时候自带了10分频,这里只需要实现10000分频就OK了。

process(clk)

begin

if(clk'eventandclk='1')

then

if(count=5)

thencount<="0000000";

elsecount<=count+1;

endif;

if(count<3)

thenclk_128_out<='1';

else

clk_128_out<='0';

endif;

endif;

endprocess;

3.2.2GOLD码产生模块

这里可以实现C/A码的使能,和卫星通道的选择,默认选择”000000”

最初不使能,reset复位,en使能以后,C/A码发生正式开始工作。

它的时钟输入是前面分频器的时钟输出。

3.2.3DDSIP核

ddsip核是软件自带的,配置后就可以直接使用。

此处选择采样频率50MHZ,输出频率为1MHZ,输出波形为sin正弦波。

图3-4DDSIP核配置

3.2.4延时模块

延迟单时钟周期寄存器模块,用于对伪随机序列进行延迟,确保调制时,在载波的0或pi相位发生相位翻转。

延时模块添加的个数要根据仿真结果决定。

3.2.5BPSK调制信号产生模块

根据C/A码与基带信号混合后的信号,将ddsip产生的正弦载波信号变成BPSK信号。

过程为:

以二进制调相为例,取码元为“1”时,调制后载波与未调载波同相;取码元为“0”时,调制后载波与未调载波反相;“1”和“0”时调制后载波相位差180°。

4.仿真结果

4.1单个模块仿真

4.1.1分频器

图4-16分频器

4.1.2GOLD码产生器

图4-2C/A序列码

4.1.3DDSIP核

图4-3DDSIP核产生载波

4.1.4延时模块

图4-4单周期时钟延时模块

4.2整体仿真

图4-5BPSK信号调制

总结

本课设的研究虽然取得了一定的收获,但在很多方面还有待于进一步的改进和完善。

特别是在信息技术飞速发展的今天,各种电子产品层出不穷,各种技术与方法也在不断地改善,因此对电子技术知识的学习也应不断地充实和更新,以适应工作与社会的需要。

本设计是在老师的精心指导和鼓励下完成的。

在此,谨向老师和帮助我的同学表示衷心的感谢!

此外,我还要感谢在我的论文中所有被援引过的文献的作者们,他们是我的知识之源!

参考文献

[1]郑凤涛,陈金佳.基于CPLD的数控正弦波的信号源的设计.黎明职业大学学报,2003,38

(1):

25~30

[2]徐志军,徐光辉.CPLD/FPGA的开发与应用.北京:

电子工业出版社,2002:

192~272

[3]黄正谨,徐坚,章小丽等.CPLD系统设计技术入门与应用.北京:

电子工业出版社,2002:

93~209

[4]韩素敏,郑征.基于VHDL的正弦波发生器设计.陕西工学院学报,2003,19(4):

8~10

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 应用 电子技术

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx