FPGA实验指导书1.docx

FPGA实验指导书1.docx

- 文档编号:27845489

- 上传时间:2023-07-05

- 格式:DOCX

- 页数:24

- 大小:1.06MB

FPGA实验指导书1.docx

《FPGA实验指导书1.docx》由会员分享,可在线阅读,更多相关《FPGA实验指导书1.docx(24页珍藏版)》请在冰豆网上搜索。

FPGA实验指导书1

实验一组合逻辑3-8译码器的设计

一、实验目的:

1、通过3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解可编程器件设计的全过程。

二、实验步骤:

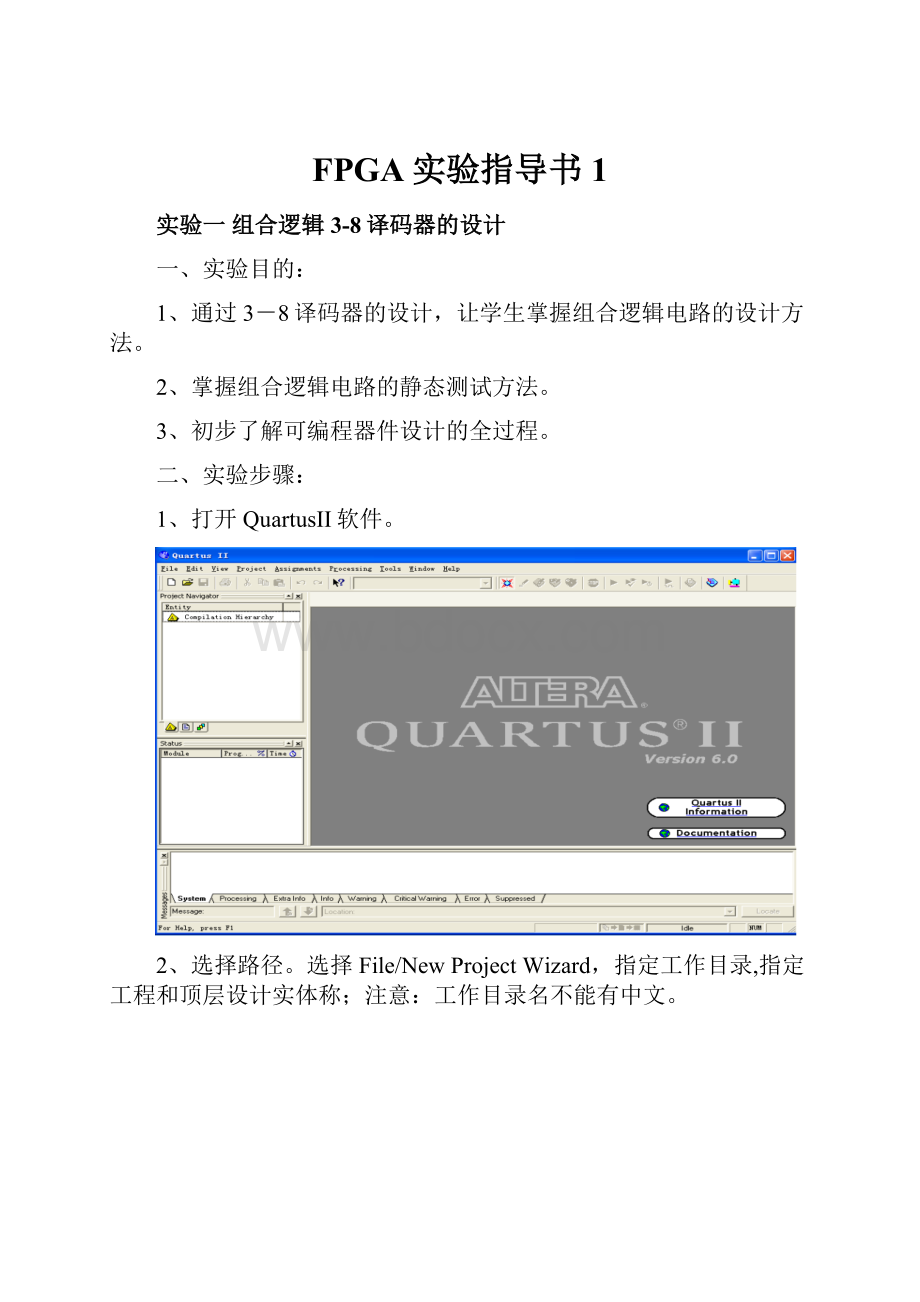

1、打开QuartusII软件。

2、选择路径。

选择File/NewProjectWizard,指定工作目录,指定工程和顶层设计实体称;注意:

工作目录名不能有中文。

3、添加设计文件。

将设计文件加入工程中。

单击“Next”,如果有已经建立好的VHDL或者原理图等文件可以在Filename中选择路径然后添加,或者选择AddAll添加所有可以添加的设计文件(.VHDL,.Verilog原理图等)。

如果没有直接点击“Next”,等建立好工程后再添加也可,这里我们暂不添加。

4、选择FPGA器件。

Family选择CycloneII,Availabledevice选EP2C35F484C8,Packge选择Any,PinCount选择484,Speedgrade选择Any;点击“Next”。

5、选择外部综合器、仿真器和时序分析器。

QuartusII支持外部工具,可通过选中来指定工具的路径。

这里我们不做选择,默认使用QuartusII自带的工具。

6、结束设置。

单击“Next”,弹出“工程设置统计”窗口,上面列出了工程的相关设置情况。

最后单击“Finish”,结束工程设置。

7、建立原理图文件。

如果在建立工程时没有添加设计文件,这时可以新建文件再添加。

也可通过选择Project/Add/RemoveFilesInProject来添加外部文件。

8、添加文件到工程中。

点击“OK”,并选择File/SaveAs,选择和工程相同的文件名。

点击“保存”,文件就被添加进工程当中。

9、原理图建立完毕。

这时,可以开始在原理图上进行设计了。

提示:

用户可以在打开QuartusII后直接建立原理图或者VHDL文件,选择SaveAs,系统会提示是否要保存为工程文件,选择建立工程文件,也可进入工程文件建立流程。

10、添加器件。

按照3-8译码器的电路图添加器件并连线。

可以看到在下图中,左下角处已添加4位功能选择位,设置状态为0001,即16位拨码开关接到16位数据总线上。

11、预编译。

选择Processing/Start/StartAnalysis&Synthesis,进行综合。

12、添加管脚信息。

当综合完成后,网表信息才会生成。

选择Assignments/AssignmentEditor在Edit中选择NodeFider,在NodeFider中选择List显示所有节点信息,然后全部选中。

13、为每个节点分配引脚。

EP1C12器件

EP2C35器件

14、全局编译。

15、下载。

下载可以选择JTAG方式和AS方式(JTAG下载方式把文件直接下载到FPGA里面,AS下载方式把文件下载到配置芯片里面,因此可以掉电存储)。

选择Tool/Programmer,选择JTAG下载方式,选择AddFile,添加.sof文件(AS下载选择.pof文件)并选中Program/Configure,点击“Start”后开始下载。

第一次使用下载时,首先点击“HardwareSetup...”,打开HardwareSetup对话框,然后点击AddHardware,选择ByteBlasterII后单击”SelectHardware”,选择下载形式为ByteBlasterII。

三、功能仿真验证

在下载程序之前可以利用QuartusII的强大功能,对所设计的工程进行功能仿真验证或时序仿真验证。

从菜单File-New中选择创建VectorWaveformFile,如下图所示。

在新的波形文件中选入需要验证的引脚,通过在左边窗栏理点击鼠标右键,选InsertNodeorBus..,在打开的对话框中点击List,选择所要观察的信号引脚,设置引脚的信号值,如下图所示。

点击保存Save.

在Settings对话框中,选中SimulatorSettings选择页,设置Function类型仿真,并将新创建的波形文件当作仿真输入,如下图所示:

设置完毕之后,点击Processing->GenerateFunctionalSimulatorNetList,生产网表文件之后,点击StartSimulator,进行功能仿真,然后验证逻辑功能是否正确。

四、实验接线及说明

A、B、C、G1、G2AN、G2BN分别对应实验箱底板SW1—SW6

Y0N—Y7N分别对应实验箱底板IO9—IO16

实验接线:

用导线将IO9—IO16与8位LEDL1—L8相连,LED为高电平点亮

控制拨码开关SW1—SW6,观察L1—L8显示状态是否与预期输出结果一置。

实验二基于FPGA的数字钟的设计

一、设计要求

1.具有时,分,秒,计数显示功能,以24小时循环计时。

2.具有清零,调节小时、分钟功能。

3.具有整点报时功能,整点报时的同时LED灯花样显示。

二、实验目的

1.掌握多位计数器相连的设计方法。

2.掌握十进制,六进制,二十四进制计数器的设计方法。

3.继续巩固多位共阴级扫描显示数码管的驱动,及编码。

4.掌握扬声器的驱动。

5.LED灯的花样显示。

6.掌握EPLD技术的层次化设计方法。

三、实验原理

1.时钟计数:

秒——60进制BCD码计数;

分——60进制BCDD码计数;

时——24进制BCDD码计数;

整个计数器有清零,调分,调时功能,在接近整数时间能提供报时信号。

2.具有驱动8位八段共阴扫描数码管的片选驱动信号输出和八段字形译码输出,编码和扫描部分可参照前面实验。

3.扬声器在整点时有报时驱动信号产生。

4.LED灯在整点时有花样显示信号产生。

四、实验内容及步骤

1.根据电路持点,可在教师指导下用层次设计概念,将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口,让几个学生分做和调试其中之一,然后再将各模块合起来联试,以培养学生之间的合作精神,同时加深层次化设计概念。

2.了解软件的元件管理深层含义,以及模块元件之间的连接概念。

了解如何融合不同目录下的统一设计。

模块说明:

各种进制的计数及时钟控制模块(10进制、6进制、24进制);

扫描分时显示,译码模块;

彩灯,扬声器编码模块;

各模块都是由VHDL语言编写。

图26-1数字钟各模块连接示意图

五、实验连线◎输入接口:

1.代表清零,调时,调分信号RESET,SETHOUR,SETMIN的管脚分别已经连接按键开关。

2.代表计数时钟信号CLK和扫描时钟信号CKDSP的管脚分别已经同1HZ时钟源和32HZ(或更高)时钟源相连。

3.Reset键为低电平复位,已经接上。

◎输出接口:

1.代表扫描显示的驱动信号管脚SCAN2,SCAN1,SCAN0已经接到实验箱上的SCAN0~SCAN2,A…G接八位数码管显示模块的A~G。

2.代表花样LED灯显示的信号管脚LAMP0…LAMP2已经同3个LED灯相连。

代表到时LED灯闪烁提示的ENHOUR接LED灯。

SETHOUR、SETMIN分别对应CPU板上的PB0、PB1(有些CPU板对应的标识是SW1、SW2)

RESET对应CPU板上的RESET

CLKDSP对应CPU板上的50MHz固定晶振输入。

LAMP对应IO9-IO11。

CLK,对应IO3。

功能选择位M[3..0]状态为0010,左端8个数码管,低8位为7位段加小数点选取位,高8位为8个数码管com端选取,即如果要选取数码管0,则发送总线值为:

1111111011111111,如要选取数码管1,则发送总线值为:

1111110111111111,此时所选数码管7段和DP位将全部亮。

实验接线:

用导线连接IO3与ADJ_CLK,调整SW17-SW20,使输出频率为1Hz;

IO9-IO11接到L1-L3上;IO5接到蜂鸣器的BUZZER控制端口。

按下PB0、PB1(有些CPU板对应的标识是SW1、SW2)可以调整时钟,分钟。

实验三基于NIOS的交通灯实验

一、实验目的

1、学习NIOSII应用程序控制自定义Avalon总线外设。

2、学习用Avalon总线接口的设备控制交通灯。

二、实验原理

1、12个交通灯和蜂鸣器周围的4个LED灯的输出值由实验箱底板上下边的CPLD芯片EPM1270来控制,LED为高电平点亮,在做NIOSII实验时,实验箱底板上的两片CPLD看作是NIOSII的一个总线型外设,16位LED的输出值为这个总线型外设的一个寄存器锁存输出值。

2、NIOSII软核CPU通过Avalon三态总线桥,允许多个总线型设备同时共享总线资源,从而把多个总线型设备,挂接在同一组总线上。

每一个总线型设备拥有其唯一的片选信号,数据、地址,读写控制信号等则可以同时与其它总线型设备复用。

3、本实验中实验箱底板上两片CPLD即是一个挂接在三态总线上的一个外设。

同时挂接在这条三态总线上的设备还有CPU上的SRAM、Flash、RTL8019网络接口芯片。

两片CPLD共用同一条片选信号线,读/写信号线各一条,16位数据线用于数据读写,4位地址线可访问16个寄存器。

对LED操作即为对寄存8(二进制地址为1000)写操作。

如执行NIOSII指令:

write_bus16((cs7+8),0x0001);

则为向以cs7为基地址,以8为偏移地址的寄存器写0x0001,这条指令的功能是使LED1点亮,除LED1以外的其它LED均为不点亮状态。

三、实验步骤:

1、将样例工程SOPC_BASE.rar压缩包解压到磁盘根目录下,如:

E:

\SOPC_BASE\

(用户可以参考本样例工程创建自己的工程,或者在此样例工程的基础上进行必要的修改,添加用户所需模块或删除不必要的模块,SOPCBuilder模块资源如下图,具体创建步骤,请参考《NIOSIIStepbyStep》及其它相关资料。

)

SOPCBuilder模块资源

2、打开QuartusII工程:

在文件夹E:

\SOPC_BASE\中找到E_Play.qpf,双击打开工程文件E_Play.qpf。

3、打开SOPCBuilder:

在QuartusII环境中选择菜单ToolsSOPCBuilder…,打开SOPCBuilder向导,打开Techshine_EP1C12.ptf。

点Generate编译SOPCBuilder。

(如果使用样例工程,可以跳过步骤3。

本工程已经在QuartusII5.1sp1环境下编译通过,如果更换不同版本或更换license后,请重新编译)。

4、编译QuartusII工程:

在QuartusII环境主菜单下选择PressingStartCompilation。

编译完成后生成相关配置文件(.sof和.pof文件)。

(如果使用样例工程,可以跳过步骤4。

本工程已经在QuartusII5.1sp1环境下编译通过,如果更换不同版本或更换license后,请重新编译)。

5、打开NIOSIIIDE环境:

开始程序AlteraNIOSII5.1NIOSIIIDE。

在工作路径中输入:

E:

\SOPC_BASE\software\workspace。

6、创建NIOSII应用工程:

在NIOSIIIDE环境主菜单下选择FileNewProject……。

在弹出的新建工程向导中,选择第一项C/C++Application,点Next,下一步操作。

在弹出的C/C++Application工程向导中,在窗口左下的工程模板中选择BlankProject,命名工程为“led16”,目标硬件选择中浏览找到,QuartusII工程中的Techshine_EP1C12.ptf文件,点Next,下一步操作。

在弹出的系统库设置中,按默认选第一项Createanewsystemlibrarynamed,新建系统库.点Finish,完成系统库创建。

复制“traffic.c”原程序,选择NIOSII工程traffic,右键弹出菜单中选择Paste添加文件traffic.c到工程。

7、编译NIOSII应用工程:

在工程管理窗口中选中traffic应用工程,鼠标右键点击在弹出菜单中选择BuilderProject,NIOSIIIDE将自动先编译系统库traffic_syslib,完成后自动编译应用工程traffic。

8、下载配置文件。

在NIOSIIIDE主菜单中选择ToolsQuartusIIProgrammer,打开QuartusIIProgrammer窗口。

(或通过开始菜单打开QuartusIIProgrammer),默认为JTAG下载方式,点”AddFile…”按钮,流览添加QuartusII工程目录下的“E_Play.sof”文件,在相应的“Programmer/Configure”项上打勾,点“Start”下载程序。

在下载配置文件前,先将ByteBlasterII下载线插到JTAG方式下载口,并给目标板接通电源。

9、运行NIOSII应用工程:

在NIOSIIIDE工程管理窗口,选中要运行的工程traffic,鼠标右键弹出菜单中选择RunAsNIOSIIHardware。

运行成功,在NIOSIDE控制台显示“programmestart!

”,同时可以看到交通灯的效果。

实验四静态图像显示

一、实验目的

1、熟悉VGAIP核的寄存器操作

二、实验设备

计算机,NIOS_II&QuartusII8.1,EL-SOPC4000实验箱,E-PLAY-2C35或E-PLAY-3C25-B或E-PLAY-3C80,其他CPU板无法完成此实验。

三、实验步骤

1、连接好电脑和仿真器、CPU板和仿真器;

2、用VGA连接线连接8寸液晶屏和CPU板上的VGA接口;

3、给实验设备上电,打开QuartusII8.1,下载TechshinVGA.sof;

4、打开NiosIIIDE,导入TechshinVGA_E2C35softwareVGA_test和VGA_test_syslib。

导入过程如下:

首先在nios2projects栏空白处右键单击,然后选择Import,显示如下:

选择next,进入如下界面:

浏览找到VGA_test,

点击确定,完成后点击finish

点击yes,完成VGA_test的导入,用同样的方法导入VGA_test_syslib。

5、由于要显示的图片是预先存入flash中的,所以先要选择

进入烧写界面,

双击Flashprogrammer,选择programafileintoflashmemory,浏览找到要烧写的图片文件,图像格式为bmp,大小为900k,

偏移地址offset,对于EP3C25设置为0x00100000,对于EP2C35设置为0x01000000,对于EP3C80设置为0x00100000,EP4CE22设置为0x00100000,对于EP2C35,板上是一块flash芯片,容量为32M,所以第二幅图片烧写时设置偏移地址offset为0x01100000,第三幅图片烧写时设置偏移地址offset为0x01200000,其他以此类推,其他CPU板上是2片2M,共4M的flash,所以烧写第二,第三幅图片按如下设置。

完成后点ProgramFlash开始烧写,

在NIOS2IDE的控制台显示如上图所示时,说明flash烧写成功。

用同样的方法烧入第二幅图像设置如下:

第三幅图像的设置如下:

1、运行VGA_test。

程序的核心代码如下:

程序中,图像时存放在flash偏移地址为0x01000000,程序中之所以写成的0x01000036,0x36即54表示BMP图像的头信息。

运行程序后,可看到液晶屏上显示所烧入的图片。

也可烧入多幅图片,循环显示,做成电子相册。

仅供个人用于学习、研究;不得用于商业用途。

Forpersonaluseonlyinstudyandresearch;notforcommercialuse.

NurfürdenpersönlichenfürStudien,Forschung,zukommerziellenZweckenverwendetwerden.

Pourl'étudeetlarechercheuniquementàdesfinspersonnelles;pasàdesfinscommerciales.

толькодлялюдей,которыеиспользуютсядляобучения,исследованийинедолжныиспользоватьсявкоммерческихцелях.

以下无正文

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 实验 指导书

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《贝的故事》教案4.docx

《贝的故事》教案4.docx