EDA 第五章作业.docx

EDA 第五章作业.docx

- 文档编号:27724909

- 上传时间:2023-07-04

- 格式:DOCX

- 页数:15

- 大小:1.01MB

EDA 第五章作业.docx

《EDA 第五章作业.docx》由会员分享,可在线阅读,更多相关《EDA 第五章作业.docx(15页珍藏版)》请在冰豆网上搜索。

EDA第五章作业

5-7.用74283加法器和逻辑门设计实现一位841BCD码加法器电路,输入输出均为BCD码,CI为低位的进位信号,CO为高位的进位信号,输入为两个一位十进制数A,输出用S表示。

设计如下

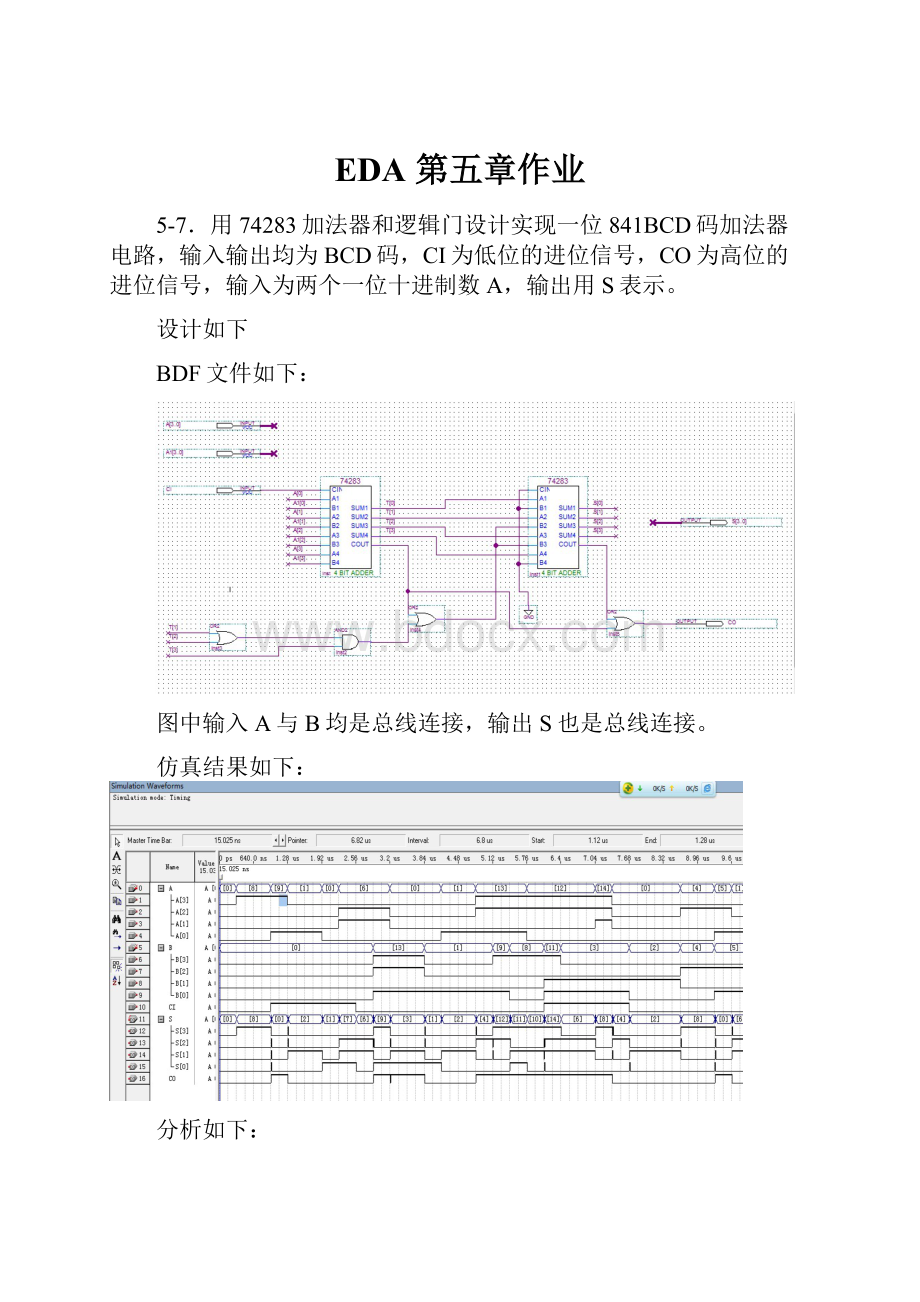

BDF文件如下:

图中输入A与B均是总线连接,输出S也是总线连接。

仿真结果如下:

分析如下:

仿真图刚开始时,A=1000,B=0000,CI=0,此时输出S=1000。

当仿真到5.12us左右时,A=1101,B=1001,CI=0,此时S=0100,同时CO=1。

因此,此设计是符合逻辑的,是正确的。

5-1-7.以1位二进制全加器为基本元件,用例化语句写出8位并行全加器的顶层文件,并讨论此加法器的电路特征。

分析:

首先应设计底层文件,然后在编写顶层文件。

底层文件

半加器设计如下:

libraryieee;

useieee.std_logic_1164.all;

entityh_adderis

port(a,b:

instd_logic;

co,so:

outstd_logic);

endentityh_adder;

architecturefh1ofh_adderis

begin

so<=not(axor(notb));co<=aandb;

endarchitecturefh1;

或门设计如下:

libraryieee;

useieee.std_logic_1164.all;

entityor2ais

port(a,b:

instd_logic;

c:

outstd_logic);

endentityor2a;

architectureoneofor2ais

begin

c<=aorb;

endarchitectureone;

全加器设计如下:

libraryieee;

useieee.std_logic_1164.all;

entityf_adderis

port(ain,bin,cin:

instd_logic;

cout,sum:

outstd_logic);

endentityf_adder;

architecturefd1off_adderis

componenth_adder

port(a,b:

instd_logic;

co,so:

outstd_logic);

endcomponent;

componentor2a

port(a,b:

instd_logic;

c:

outstd_logic);

endcomponent;

signald,e,f:

std_logic;

begin

u1:

h_adderportmap(a=>ain,b=>bin,co=>d,so=>e);

u2:

h_adderportmap(a=>e,b=>cin,co=>f,so=>sum);

u3:

or2aportmap(a=>d,b=>f,c=>cout);

endarchitecturefd1;

得到全加器的RTL图如下:

其中ain,bin为输入,cin为低位的进位,sum为和,cout为向高位的进位。

顶层文件如下:

libraryieee;

useieee.std_logic_1164.all;

entityf_adder8is

port(ain,bin:

instd_logic_vector(7downto0);

cin:

instd_logic;

sum:

outstd_logic_vector(7downto0);

cout:

outstd_logic);

endentityf_adder8;

architectureoneoff_adder8is

componentf_adderis

port(ain,bin,cin:

instd_logic;

cout,sum:

outstd_logic);

endcomponent;

signalc1,c2,c3,c4,c5,c6,c7:

std_logic;

begin

u1:

f_adderportmap(ain=>ain(0),bin=>bin(0),cin=>cin,sum=>sum(0),cout=>c1);

u2:

f_adderportmap(ain=>ain

(1),bin=>bin

(1),cin=>c1,sum=>sum

(1),cout=>c2);

u3:

f_adderportmap(ain=>ain

(2),bin=>bin

(2),cin=>c2,sum=>sum

(2),cout=>c3);

u4:

f_adderportmap(ain=>ain(3),bin=>bin(3),cin=>c3,sum=>sum(3),cout=>c4);

u5:

f_adderportmap(ain=>ain(4),bin=>bin(4),cin=>c4,sum=>sum(4),cout=>c5);

u6:

f_adderportmap(ain=>ain(5),bin=>bin(5),cin=>c5,sum=>sum(5),cout=>c6);

u7:

f_adderportmap(ain=>ain(6),bin=>bin(6),cin=>c6,sum=>sum(6),cout=>c7);

u8:

f_adderportmap(ain=>ain(7),bin=>bin(7),cin=>c7,sum=>sum(7),cout=>cout);

endarchitectureone;

得到RTL图如下:

其中ain,bin都为总线输入,都是8位的数据,cin为低位的进位;sum为8位的输出,cout为进位。

仿真波形图如下:

分析波形:

如图在刚开始的时候ain=00000001,b=00000001,ci=0,此时输出sum=00000010,实现了加法运算;当ain=01100000,b=000000111,ci=0,此时输出sum=01100111,同样是正确的。

6-9.根据例4-23设计8位左移移位寄存器,给出时序仿真波形。

编写程序如下:

libraryieee;

useieee.std_logic_1164.all;

entityshfrtis

port(clk,load:

instd_logic;

din:

instd_logic_vector(7downto0);

qb:

outstd_logic);

endentityshfrt;

architecturebehvofshfrtis

begin

process(clk,load)

variablereg8:

std_logic_vector(7downto0);

begin

ifclk'eventandclk='1'then

ifload='1'thenreg8:

=din;

elsereg8(7downto1):

=reg8(6downto0);

endif;

endif;

qb<=reg8(7);

endprocess;

endbehv;

得到RTL图如下:

仿真波形图如下:

分析波形:

如图所示,在刚开始时,将数据全部输出,以后在没来一个时钟脉冲的时候,就向高位移一位,也即左移一位,实现了8位左移。

实验6-4

题目:

32位并进/并出移位寄存器设计

8位移位寄存器设计:

libraryieee;

useieee.std_logic_1164.all;

entityshiftis

port(clk,co:

instd_logic;

md:

instd_logic_vector(2downto0);

d:

instd_logic_vector(7downto0);

qb:

outstd_logic_vector(7downto0);

cn:

outstd_logic);

endentityshift;

architecturebehavofshiftis

signalreg:

std_logic_vector(7downto0);

signalcy:

std_logic;

begin

process(clk,md,co)

begin

ifclk'eventandclk='1'then

casemdis

when"001"=>reg(0)<=co;

reg(7downto1)<=reg(6downto0);cy<=reg(7);

when"010"=>reg(0)<=reg(7);

reg(7downto1)<=reg(6downto0);

when"011"=>reg(7)<=reg(0);

reg(6downto0)<=reg(7downto1);

when"100"=>reg(7)<=co;

reg(6downto0)<=reg(7downto1);cy<=reg(7);

when"101"=>reg(7downto0)<=d(7downto0);

whenothers=>reg<=reg;cy<=cy;

endcase;

endif;

endprocess;

qb(7downto0)<=reg(7downto0);cn<=cy;

endbehav;

其RTL图如下:

8位锁存器设计:

libraryieee;

useieee.std_logic_1164.all;

entitydff_8is

port(clk:

instd_logic;

d:

instd_logic_vector(7downto0);

q:

outstd_logic_vector(7downto0));

endentitydff_8;

architecturebehavofdff_8is

begin

process(clk,d)

begin

ifclk='1'thenq<=d;

endif;

endprocess;

endbehav;

其RTL图如下:

总的设计接线图如下图,用到了4个8位移位寄存器和4个8位锁存器。

总图设计:

仿真波形如下:

由波形图可以看出d为初始值当md=101时就读入数据,如在图中d的值为“111001*********10010100101010101”

当md=101时q=“111001*********10010100101010101”。

当md=001时q的值就向高位移一个。

如此,当md为其他值时就会有对应的操作。

因此,实现了设计要求。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 第五章作业 第五 作业

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx