硬件电子琴电路模块方案设计具体步骤.ppt

硬件电子琴电路模块方案设计具体步骤.ppt

- 文档编号:2763048

- 上传时间:2022-11-12

- 格式:PPT

- 页数:43

- 大小:1.66MB

硬件电子琴电路模块方案设计具体步骤.ppt

《硬件电子琴电路模块方案设计具体步骤.ppt》由会员分享,可在线阅读,更多相关《硬件电子琴电路模块方案设计具体步骤.ppt(43页珍藏版)》请在冰豆网上搜索。

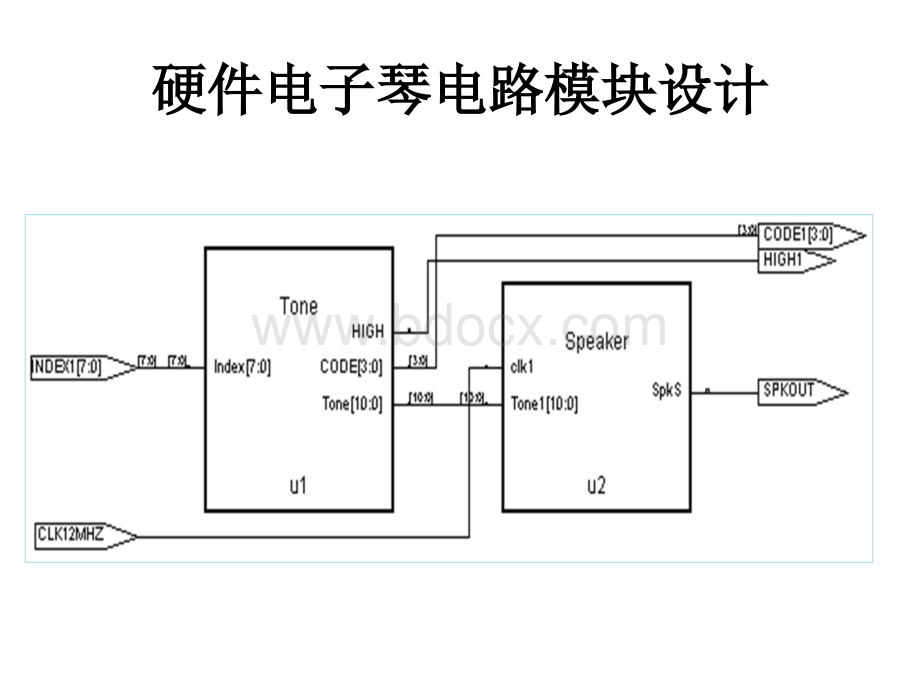

硬件电子琴电路模块设计硬件电子琴电路模块设计模块模块Speaker模块模块Speaker中的主要电路是中的主要电路是一个数控分频一个数控分频器器,它由一个初值可预置的加法计数器构,它由一个初值可预置的加法计数器构成,当模块成,当模块Speaker由端口由端口Tone获得一个获得一个2进制数后,将以此值为计数器的预置数,进制数后,将以此值为计数器的预置数,对端口对端口Clk12MHZ输入的频率进行分频,之输入的频率进行分频,之后由后由Spkout向扬声器输出发声。

向扬声器输出发声。

模块模块TONE模块模块Tone是音阶发生器,当是音阶发生器,当8位发声控制输位发声控制输入入Index中某一位为高电平时,则对应某一中某一位为高电平时,则对应某一音阶的数值将从端口音阶的数值将从端口Tone输出,作为获得该输出,作为获得该音阶的分频预置值;同时由音阶的分频预置值;同时由Code输出对应输出对应该音阶简谱的显示数码,如该音阶简谱的显示数码,如5,并由,并由High输出指示音阶高输出指示音阶高8度显示。

度显示。

增加乐曲自动演奏电路增加乐曲自动演奏电路在原设计的基础上,增加一个在原设计的基础上,增加一个Notetabs模模块用于产生节拍控制(块用于产生节拍控制(Index数据存留时间)数据存留时间)和音阶选择信号,即在和音阶选择信号,即在Notetabs模块放置模块放置一个乐曲曲谱真值表,由一个计数器的计一个乐曲曲谱真值表,由一个计数器的计数值来控制此真值表的输出,而由此计数数值来控制此真值表的输出,而由此计数器的计数时钟信号作为乐曲节拍控制信号,器的计数时钟信号作为乐曲节拍控制信号,从而可以设计出一个纯硬件的乐曲自动演从而可以设计出一个纯硬件的乐曲自动演奏电路。

奏电路。

硬件电子琴电路设计方案硬件电子琴电路设计方案1、构建一个工程名为songer的工程由File-NewProjectWizard,弹出对话框,设置文件夹目录,Project名称。

注意,1)不能将文件夹放置在软件安装目录下,应放在DATA盘上2)要求以自己的学号作为文件夹名暂无文件添加,按next,继续根据DE2实验平台,选择FPGA目标器件为:

CycloneII系列:

EP2C35F672C6仍然使用软件自带的综合仿真工具,所以按NEXT,继续Project建立总结,按Finish完成输入Speakera的Verilog文本由File-New,得如下对话框,选择VerilogHDLFile:

将设计的Verilog程序输入,并存盘名为Speakera.v由File-new,弹出对话框,选择otherfiles-VectorWaveformFile将波形文件存盘为Speakera.vwf设定Speakera.v是目前的顶层文件由Processing-start-startannlysis&elaboration对程序进行初步的分析双击波形文件下的空白区,得到如下对话框,点击NoderFinder弹出下面的对话框,单击List,选中Clk、Spks、Tone几个端口,单击_后,点击OK由edit-endtime,设定仿真终止时间为1ms,选中Clk点击设置周期是10ns,设置Tone为:

11111111000由assigments-settings,对仿真工具设定为功能仿真,并将激励文件调入由Processing-generatefunctionalsimulationnetlist,提取功能仿真的网表由processing-startsimulation进行功能仿真,并对结果进行分析。

时序仿真由assignments-settings,更改仿真器的设置为时序仿真:

timing由processing-startcompile对设计进行全编译再由processing-startsimulation进行时序仿真,分析结果仿照工程Speakera的设计方法,再分别设计NoteTabs、ToneTaba、div_27和div_50模块,并分别对ToneTaba、div_50进行功能仿真和时序仿真,对仿真结果进行分析。

而div_27模块在QuartusII仿真时间太长,选用Modelsim仿真,这里不做要求。

2、演奏模块的NoteTabs模块是一个根据时钟信号将存放在ROM中的乐曲曲谱真值表自动读取出来的模块,所以还需要设计一个存放“梁祝”乐曲演奏数据的ROM模块Music新建一个mif文件:

由File-new,弹出对话框,选择otherfiles-MemoryInitialzationFile将其宽度设置成4bit,长度设置成256根据“梁祝”乐曲演奏数据,在表中填入相应的值并保存为Music.mif调用Music.nif生成ROM模块.Tools菜单下选择MegaWizardPlug-InManager选择第一项,点Next在右边输入输出文件的文件名为:

Music在左边MemoryCompiler下选择ROM:

1-PORT,点击Next。

在弹出的窗口中设置4bit的单位存储宽度,256的存储长度,点击Next到下图所示的时候,点击”Browse”添加刚才建立的Music.mif文件,然后点击Next,到最后Finish。

3、创建顶层模块输入songer的Verilog代码并保为songer.v设置songer.v为顶层文件4、锁引脚1)根据DE2_pin_assignments文件内容、格式制作本设计引脚对应文件的引脚锁定文件:

songer.csv2)由Assignments-ImportAssignment,打开对话框,调入引脚对应文件songer.csv即可锁好引脚后由processing-startcompilation进行全编译如果编译没有错误,准备下载用发光管LEDR3LEDR0显示Code3Code0(PIN_AC22,AB21,AF23,AE23)表示琴音简谱码,发光管LEDR17(PIN_AD12)显示高8度,Spkout接AUD_DACLRCK(PIN_C6)。

当程序下载到DE2板上去后通过耳机可以听到优美的“梁祝”的乐曲。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 硬件 电子琴 电路 模块 方案设计 具体步骤

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

保育笔记.doc

保育笔记.doc

幼儿园日常安全检查记录表.xls

幼儿园日常安全检查记录表.xls