超经典!2010电子设计竞赛培训第3章(共四章).ppt

超经典!2010电子设计竞赛培训第3章(共四章).ppt

- 文档编号:2755471

- 上传时间:2022-11-11

- 格式:PPT

- 页数:99

- 大小:2.48MB

超经典!2010电子设计竞赛培训第3章(共四章).ppt

《超经典!2010电子设计竞赛培训第3章(共四章).ppt》由会员分享,可在线阅读,更多相关《超经典!2010电子设计竞赛培训第3章(共四章).ppt(99页珍藏版)》请在冰豆网上搜索。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

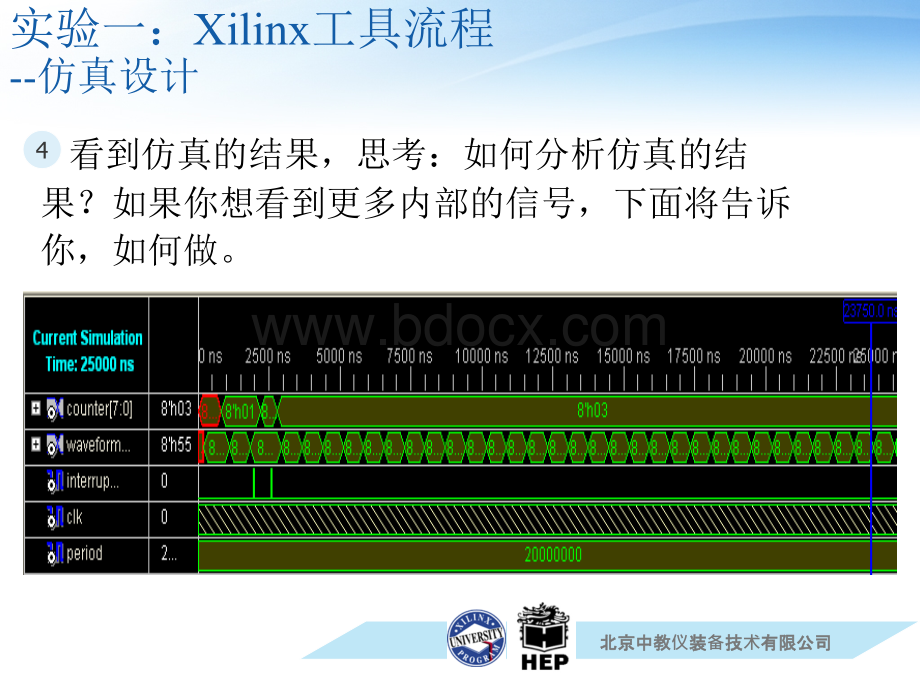

Xilinx工具流程-仿真设计看到仿真的结果,思考:

如何分析仿真的结果?

如果你想看到更多内部的信号,下面将告诉你,如何做。

4北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-仿真设计这张图说明了这个过程:

1)在Source窗口展开kcpsm3_int_test2)在下面的窗口选中address9:

0,并点击鼠标右键3)选择AddToWaveform,想要观察的信号终于出现了。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合行为级综合可以自动将系统直接从行为级描述综合为寄存器传输级描述。

行为级综合的输入为系统的行为级描述,输出为寄存器传输级描述的数据通路。

行为级综合工具可以让设计者从更加接近系统概念模型的角度来设计系统。

同时,行为级综合工具能让设计者对于最终设计电路的面积、性能、功耗以及可测性进行很方便地优化。

行为级综合所需要完成的任务从广义上来说可以分为分配、调度以及绑定。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合Xilinx综合工具在对设计的综合过程中,主要执行以下三个步骤:

1)语法检查过程,检查设计文件语法是否有错误;2)编译过程,翻译和优化HDL代码,将其转换为综合工具可以识别的元件序列;3)映射过程,将这些可识别的元件序列转换为可识别的目标技术的基本元件;北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合在ISE的主界面的处理子窗口的synthesis的工具可以完成下面的任务:

1)查看综合报告(viewSynthesisReport)2)查看RTL原理图(ViewRTLschematic)3)查看技术原理图(ViewTechnologySchematic)4)检查语法(CheckSyntax)5)产生综合后仿真模型(GeneratePost-SynthesisSimulationModel)。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合属性设置在处理子窗口下,选择Synthesis-XST,单击鼠标右键,选择Properities出现下面的窗口注意:

看起来好像很复杂,但是掌握方法,就知道其中的奥妙了,北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合属性设置如果你想彻底如果你想彻底的弄懂,参考文献的弄懂,参考文献会告诉你全部的答会告诉你全部的答案。

案。

其实,对于竞其实,对于竞赛和教学没必要都赛和教学没必要都弄清楚,这点要切弄清楚,这点要切记。

记。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合实现综合很简单,只需在处理子窗口中,用鼠标双击Synthesize-XST,小圆圈出现,并且在控制台窗口,显示综合过程中的信息。

当出现绿色小圆圈的时候,综合就完成了。

下面将揭开综合过程的一些迷,目的深入了解XST的综合过程。

1北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合查看RTL符号2双击,展开,内部结构一目了然双击,展开,内部结构一目了然北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计综合北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现在ISE中的实现(Implement)过程,是将综合输出的逻辑网表翻译成所选器件的底层模块与硬件原语,将设计映射到器件结构上,进行布局布线,达到在选定器件上实现设计的目的。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现实现过程主要分为3个步骤:

翻译(Translate)逻辑网表,映射(Map)到器件单元与布局布线(Place&Route)。

翻译的主要作用是将综合输出的逻辑网表翻译为Xilinx特定器件的底层结构和硬件原语。

映射的主要作用是将设计映射到具体型号的器件上。

布局布线的主要作用是调用Xilinx布局布线器,根据用户约束和物理约束,对设计模块进行实际的布局,并根据设计连接,对布局后的模块进行布线,产生PLD配置文件。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现参数设置选择ImplementDesign,点击鼠标左键,选择Properties,出现下面的属性设置界面。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现参数设置如果你想彻底的弄懂,参考文献会告诉你全部的答案。

其实,对于竞赛和教学没必要都弄清楚,这点要切记。

北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现实现很简单,只需在处理子窗口中,用鼠标双击ImplementDesign,小圆圈出现,并且在控制台窗口,显示综合过程中的信息。

当出现绿色小圆圈的时候,综合就完成了。

下面将揭开实现过程的一些迷,目的深入了解XST的实现过程。

1北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现实现结果的查看。

2北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现布局布线的查看,芯片内部结构一目了然3放大放大北京中教北京中教仪装装备技技术有限公司有限公司实验一:

Xilinx工具流程-设计实现放大放大北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计目标ArchitectureWizard使设计人员配置和添加FPGA资源到设计。

PACE使设计人员添加位置约束到设计。

实验二的设计目标:

1)使用ArchitectureWizard来配置和初始化DCM(DigitalControllerManagement)2)使用PACE来实现位置约束3)实现设计,并确保使用了位置约束4)使用硬件下载和测试设计。

北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计步骤该实验包含下面几个步骤:

1)配置DCM2)初始化DCM3)分配引脚位置4)用硬件测试设计北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理实验工程VHDL设计结构。

1)连接KCPSM3和程序ROM;2)将UART宏和KCPSM3连接-输入/输出端口和波特率时钟;3)使用固定间隔的定时器产生中断,使用中断响应信号。

思考:

打开工程分析顶层文件,了解上面功能实现的方法北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理PicoBlazeuart_txInstructionsAddressInstructionsrx_dataout_port7:

0port_id7:

0write_strobeDQenport_id0port_id0Interrupt_ackalarmtxinterruptcontrolInterrupt_eventDCMclkSystemclockDesignclockDQenuart_rxrxrx_datatx_full,tx_half_fullrx_half_fullrx_full000BaudCounten_16_x_baud添加DCM到设计北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理(输入端口)北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理(输出端口)北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理(输入端口)Rx宏及操作时序北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理(输出端口)UART_Tx宏及操作时序北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-UART波特率生成北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-PicoBlaze内的RAM空间的分配北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-软件发送策略北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-软件接收策略北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-设计原理该设计要求一个55MHz时钟。

硬件开发平台上包含有50MHz时钟,使用ArchitectureWizard来产生DCM,该DCM输出55MHz时钟,并例化该模块到设计中。

北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-DCM原理数字时钟管理模块(DigitalClockManager,DCM)是基于Xilinx的高端FPGA产品中内嵌的IP模块。

在时钟的管理与控制方面,DCM与其它时钟管理模块(比如DLL),功能更强大,使用更灵活。

DCM的功能包括消除时钟的延时、频率的合成、时钟相位的调整等系统方面的需求。

DCM的主要优点在于:

1、实现零时钟偏移(Skew),消除时钟分配延迟,并实现时钟闭环控制;2、时钟可以映射到PCB上用于同步外部芯片,这样就减少了对外部芯片的要求,将芯片内外的时钟控制一体化,以利于系统设计。

北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-DCM原理DCM共由四部分组成,其中包括DLL模块、数字频率合成器DFS(DigitalFrequencySynthesizer)、数字移相器DPS(DigitalPhaseShifter)和数字频谱扩展器DSS(DigitalSpreadSpectrum)。

对于DCM模块来说,其用户需要配置的参数包括输入时钟频率范围、输出时钟频率范围、输入/输出时钟允许抖动范围等。

北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-DCM符号北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-配置DCM模块打开lab2工程,在处理子窗口中,双击CreateNewSource,弹出下面的窗口,选择IP,并输入文件名1my_dcm,点击“Next”。

下面解释选项:

北京中教北京中教仪装装备技技术有限公司有限公司实验二:

ArchitectureWizard和PACE-配置DCM模块在线逻辑分析仪生成向导在线逻辑分析仪生成向导IP核生成器向导核生成器向导约束实现向导约束实现向导原理图生成向导原理图生成向导状态图生成向导状态图生成向导仿真用测试波形生成向导仿真用测试波形生成向导Verilog语言模块输入向导语言模块输入向导用用Verilog生成仿真平台向导生成仿真平台向导VHDL语言模块输入向导语言模块输入向导VHDL库生成向导库生成向导VHDL程序包生成向导程序包生成向导用用VHDL语言生

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 经典 2010 电子设计 竞赛 培训 共四章

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

保育笔记.doc

保育笔记.doc

幼儿园日常安全检查记录表.xls

幼儿园日常安全检查记录表.xls