FPGA复位.docx

FPGA复位.docx

- 文档编号:27491692

- 上传时间:2023-07-02

- 格式:DOCX

- 页数:15

- 大小:292.70KB

FPGA复位.docx

《FPGA复位.docx》由会员分享,可在线阅读,更多相关《FPGA复位.docx(15页珍藏版)》请在冰豆网上搜索。

FPGA复位

基于FPGA的通用网络下载器硬件设计

(一)

网络下载器作为航天计算机地面检测系统的重要组成部分,发挥着重要的作用。

文中主要介绍了网络下栽器的总体设计思路,给出了硬件模块的设计原理图。

并在PCB设计中,对于LVDS接口、高速总线以及叠层的设计中给出了应用参考,保证了系统硬件的可靠性,且在实际应用中取得了稳定的性能表现。

随着航天技术的发展,地面检测设备作为大系统的重要组成部分,发挥着重要作用。

通用下载器作为测试指令和测试数据上传下发的重要通道,其可靠性和稳定性备受关注,本文介绍了通用下载器的总体设计思路,给出了原理图和PCB的设计参考,同时在实际测试中验证了该设计的可靠性和稳定性。

1系统概述

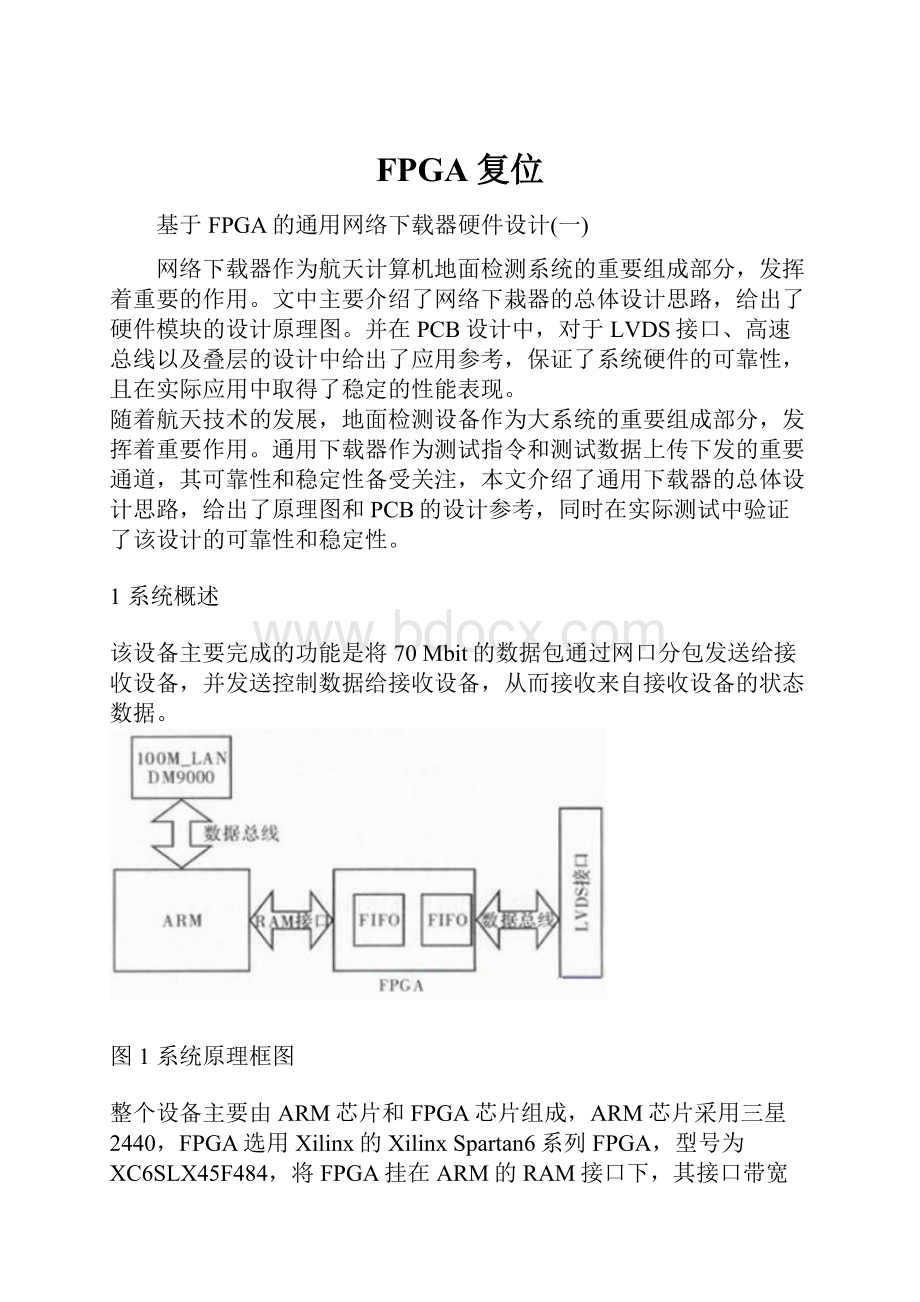

该设备主要完成的功能是将70Mbit的数据包通过网口分包发送给接收设备,并发送控制数据给接收设备,从而接收来自接收设备的状态数据。

图1系统原理框图

整个设备主要由ARM芯片和FPGA芯片组成,ARM芯片采用三星2440,FPGA选用Xilinx的XilinxSpartan6系列FPGA,型号为XC6SLX45F484,将FPGA挂在ARM的RAM接口下,其接口带宽可达133M/5x4Byte=106MByte,通过100Mbit·s-1以太网网卡与PC上位机通信,通过LVDS接口来完成与下位机的数据和控制信息交互。

FPGA通过一个FIFO接收ARM发送的数据,写使能信号(fifo_wren)由ARM发送的片选信号(nce)和写使能(nwe)控制,当地址信号为0,nce和nwe同时有效时,FIFO被写入数据(16位宽)。

FIFO读使能由FIFO空信号(fifo_empt_w)控制,当FIFO有数据写入时,FIFO空信号(fifo_empt_w)由低变高,触发读使能,数据被读出,并经LVDS后进入下位机

基于FPGA的通用网络下载器硬件设计二)

FPGA通过另一个FIFO接收下位机发送的数据,写使能信号(lvds_en_in)由下位机控制,使能信号为高后,下位机提供写时钟(lv_clk_in_wire),数据(8位宽)被写入FIFO。

FIFO读使能(fifo_rden)由ARM发送的片选信号(nce)和写使能信号(noe)控制,当FIFO有数据写入时,FIFO空信号(fifo_r_empt_w)由低变高,ARM检测到此信号后使能nce和noe,并给出读时钟,FIFO数据被读出。

ARM通过100MBIT网口接收上位机发送的TCP/IP数据包,ARM将其解包使数据内容通过ARM的RAM口发送给FPGA,而FPGA将数据包通过LVDS接口发送给接收设备。

图2FPGA模块框图

下载器通过LVDS口接收来自接收设备发送的状态数据包并缓存至FIFO中,接收完一帧后给ARM发送中断信号,ARM接收到中断信号通过RAM接口读取FPGAFIFO中的状态数据包并打包成TCP/IP数据包并通过100Mbit网口发送给上位机。

2原理图设计

2.1电源设计

系统采用5V直流供电,FPGA需要1.2V的核心电压,2.5V的VCCAUX电压,3.3V的bank电压,RAM板与LVDS接口芯片sn551vds31/32均使用3.3V电压供电,同时保证各个电压等级互不影响,采用5V直接产生1.2V,2.5V和3.3V电压的方式,其中FPGA的1.2V核心电压采用开关电源LM2852,保证供电电压的精度,提高了电源效率,2.5V和3.3V电流预估较大,为满足系统长时间工作的散热,使用TI的电源模块pth04070。

基于FPGA的通用网络下载器硬件设计(三)

2.2网络接口设计

网络接口使用DM9000芯片以及网络接口芯片HR911103A组成,DM9000是一个全集成、功能强、性价比高的快速以太网MAC层控制器。

其带有一个通用处理器接口、EEPROM接口、10/100PHY和16kB的SRAM(其中13kB用来接收FIFO,3kB用来发送FIFO)。

电源模块采用单一电源,可分别兼容3.3V和5V的IO接口电平。

设计采用3.3V电源供电,保证了系统的稳定性,100m网口双向通信带宽为50Mbit·s-1(6MByte/s)。

DM9000和2440连接了16条数据线,1条地址线,唯一地址线用于判断数据线传输的是地址或是数据,所以这16条数据线为数据和地址复用,如图4所示。

图4DM9000与2440连接图

2.3LVDS接口设计

LVDS:

LowVoltageDifferentialSignaling,低电压差分信号。

LVDS传输支持速率一般在155Mbit·s-1以上。

LVDS是一种低摆幅的差分信号技术,其使得信号能在差分PCB线对或平衡电缆上以几百Mbit·s-1的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbit·s-1。

设计采用了LVDS接口发送芯片sn551vds31和接收芯片sn55lvds32,其中发送部分采用50Ω的串联匹配,电阻精度选择为1%,保证终端匹配电阻的精度。

图5LVDS发送部分原理图

图6LVDS接收部分原理图

基于FPGA的通用网络下载器硬件设计(四)

3PCB设计

系统PCB设计需注意叠层设计,ARM和FPGA间高速总线的设计以及LVDS总线的阻抗匹配及信号约束问题。

根据TI的参考手册,通常的叠层结构为LVDS信号层、电源层(分割成LVDS电平电源和TTL电平电源)、地层(分割成LVDS电平地和TTL电平地)和TTL信号层,如图7所示。

图7PCB叠层结构图

但在实际设计中,由于叠层的设计,不可能单独列出较多层,对于TTL和LVDS信号的地层也无需进行分割,因其会破坏地层的完整性,在确保完整地的情况下,可对其他地层TTL和LVDS信号分割。

总之,在保证地层完整的情况下,使LVDS信号和TTL信号尽量分离,最好是在不同的层进行布线。

在本PCB板的设计中,使用6层叠层结构:

TOP-GND1-INNER-POWER-GND2-BOTTOM,其中TOP和BOTTOM层走LVDS信号,INNER和GND2走LVTTL信号,这样既保持了信号的分层,也保持了完整的信号回流路径。

LVDS信号频率可达600MHz以上,所以差分线要求严格等长,差分对内最好不超过10mil(0.254mm),若频率低于600MHz,该约束值可适当放宽,但上限不能超过75mil。

不同LVDS对间的布线最大差值不超过200mil。

文中在Cadence16.3的约束设置中,具体设置如下。

图8PCB叠层设计图

图9PCB布局布线图

表1PCB约束规则表

基于FPGA的通用网络下载器硬件设计(五)

差分阻抗的不匹配会产生反射,有10%的阻抗不匹配便会产生5%的反射,所以需根据不同的情况进行不同的匹配控制。

LVDS信号的差分特性阻抗为100Ω,对于LVDS信号发射端(TX),采用差分对各自串联精度为1%的50Ω电阻进行匹配,这样既保持了信号传输的功率要求,又满足了阻抗控制的要求。

图10数据测试图

4实测结果

下载器性能实测时,将LVDS接口接收和发送部分回环连接,可使用网络调试助手发送55AA组成的1032Byte的数据包,测试下载器的功能。

结果如图10所示,从图中可看到,下载器稳定的收发数据。

5结束语

设计的网络下载器将FPGA在信号处理中的优势和ARM芯片在网络通信中的优势相结合,在PCB设计中对于LVDS接口的阻抗、高速线时序以及叠层进行了设计,较好地保证了系统硬件的可靠性,并在实际使用中达到了良好的效果

FPGA研发之道(5)从零开始调试FPGA

“合抱之木,生于毫末;九层之台,起于垒土;千里之行,始于足下。

” 老子《道德经》

对于新手来说,如何上手调试FPGA是关键的一步。

对于每一个新设计的FPGA板卡,也需要从零开始调试。

那么如何开始调试?

下面介绍一种简易的调试方法。

(1)至少设定一个输入时钟input sys_clk;

(2)设定输出output[N-1:

0] led;

(3)设定32位计数器reg[31:

0] led_cnt;

(4)时钟驱动计数器开始工作

always@(posedgesys_clk)

led_cnt<=led_cnt+1

(5)输出led信号。

assignled=led_cnt[M:

N];

程序完成。

(6)设定管教约束

如果为XILINX FPGA,在UCF文件中 NET“sys_clk” LOC =管脚名称

如果为ALTERA FPGA,在QSF文件中,添加 set_location_assignment 管脚名称-to sys_clk

其他管脚,可依次类推。

(7)编译,布局、布线,生成配置文件。

XILINX 生成BIT文件。

ALTERA生成SOF文件

(8)连接JTAG,下载相应的配置文件。

(9)观察是否闪灯(肉眼可见)。

关于闪灯的解释如下:

assign led=led_cnt[M:

N]; led_cnt为32bit的信号,需要几个闪灯,则根据输入时钟的频率和肉眼能够分辨的时间(100ms)。

如输出时钟为25Mhz。

则闪灯看见的位置能够分批到10hz。

需分频2.5M=32‘h2625A0,因此,则需要输出至少为led_cnt[21]位,才能看到闪灯。

虽然程序简单,但是,通过调试可以确认:

(1)首先可确定JTAG下载器的正确连接,能够正常下载下载文件。

如不能,常见问题包括

(一)检查是否安装驱动。

(二)下载器是否由红灯变成黄灯/绿灯。

如红灯亮一般情况下,JTAG的与电路板VCC没有供电。

(三)检查JTAG连接的线序。

(四)检查JTAG电路,检查原理图上TMS,TDI,TDO的上拉和下拉电阻是否与datasheet中一致。

通过以上四种方式,可排除绝大部分JTAG下载的错误。

(2)可以判断晶振是否起振,下载后无灯闪。

(一)首先,示波器查看晶振频率,观察晶振的输出,如无输出,查看晶振的电源和地信号,如电源正常,而晶振无反应,则更换晶振。

(二)如无示波器,也有替代的方法,通过嵌入式逻辑分析仪抓信号(任意信号)。

如逻辑分析仪点击采样后无反应,则无时钟输入。

这是因为逻辑分析仪也需要时钟进行逻辑值的存储。

(3)如正常下载后闪灯,证明该FPGA板卡硬件设计上能够达到最低限度的FPGA调试状态。

最后,说明一下,为什么是闪灯而不是亮灯的程序,这是因为,首先闪灯可以判断外部晶振工作正常,并且由于LED等通常为上拉,也就是说逻辑值0表示灯亮,而也不排除某硬件工程师非要下拉。

逻辑1表示亮。

因此采用闪灯更加方便。

问题:

为什么LED灯值为什么要上拉?

这是因为:

LED上拉后,需要灯亮时电流由外部电源提供,而下拉,灯亮时电流由芯片的CMOS电路驱动。

这种在设计中应避免

FPGA研发之道(6)架构设计漫谈

(一)流驱动和调用式

勿用讳言,现在国内FPGA开发还处于小作坊的开发阶段,一般都是三、四个人,七八台机器.小作坊如何也能做出大成果。

这是每个FPGA工程师都要面临的问题。

架构设计是面临的第一关。

经常有这样的项目,需求分析,架构设计匆匆忙忙,号称一两个月开发完毕,实际上维护项目就花了一年半时间。

主要包括几个问题,一,性能不满足需求。

二,设计频繁变更。

三,系统不稳定,调试问题不收敛。

磨刀不误砍柴工,FPGA设计的需求分析是整个设计第一步。

如何将系统的功能需求,转换成FPGA的设计需求,是FPGA架构设计的首要问题。

首先,需要明确划分软件和硬件的边界。

软件主要处理输入输出、界面显示、系统管理、设备维护。

而FPGA则负责大数据流的处理。

如果使用几百元FPGA实现了一个十几元单片机就能完成的功能,就算实现的非常完美,那么这是一个什么样的神设计?

任何一个项目都要考虑成本,研发成本、物料成本、维护成本等等。

FPGA的使用位置必定是其他器件难以企及的优势。

因此对于一个FPGA架构设计,其首先需要考虑就是性能,如没有性能的需求,其他的处理器ARM就可能替代其功能。

其次就是接口,用于处理器扩展其没有的接口,作为高速接口转换。

最后,需要考虑就是可维护性,FPGA的调试是非常耗时的,一个大型的FPGA的编译时间在几小时甚至更高(通过嵌入式分析仪抓信号,每天工作8小时,只能分析两到三次)。

而软件调试只需make,编译时间以秒来记(这个问题可以通过提升编译服务器性能改善而不能消失,本质上要考虑可测性设计)。

如果不考虑维护性和可测性,调试成本和压力就非常之大。

通常,FPGA的大部分架构设计可以采用数据流驱动的方式来实现,例子1,假设一个实现视频解压缩FPGA的设计,输入是无线接口,输出为显示屏。

那么输入输出的接口基本就能确定。

以数据流为驱动可以粗略划分,输入接口->解压缩模块->视频转换模块->显示接口。

如需要视频缓冲,则确定是否需要连接外部存储器。

那就需要确认在什么位置进行数据的缓冲。

通过要支持显示的画面的质量,就能确认最大码流,同样可以计算视频解压模块和转换模块的计算能力,从而导出所需的内部总线宽度,系统频率,以及子模块个数等等。

例子2,某支持通过有线电视网上网电视IP网关,同样也是输入的普通IP网络,输出为有线调试网的调试解调器。

将IP报文等长填充后,在固定时隙内送入有线电视网中,同样也是基于数据流驱动的方式。

数据流驱动式架构,可以作为FPGA设计中一个最重要的架构。

通常来说应用于IP领域、存储领域、数字处理领域等较大型FPGA设计都是数据流驱动式架构,主要包括输入接口单元,主处理单元,输出接口单元。

还可能包括,辅助处理单元、外部存储单元。

这些单元之间一般采用流水式处理,即处理完毕后,数据打包发完下一级处理。

其中输入输出可能有多个,此时还需要架构内部实现数据的交换。

另一种较为常用的架构方式为调用式架构,即一般FPGA通过标准接口如PCI、PCI-E,CPCI,PCI-X,EMIF等等。

各种接口,FPGA内部实现某一加速单元,如视频加速,数据处理,格式转换等操作。

这种结构基本基本围绕FPGA接口、加速单元展开,属于数据的反馈类型,即处理完数据又反馈回接口模块。

其他虽然各型各样,如SOPC,如各型接口,但本质上其都是为上述架构服务的,或做配置管理替代外部CPU,或在数据流中间传递中间参数。

或在内部实现CPU+协处理器的架构,因此说,无他变化。

孙子兵法云:

“兵无常势,水无常形”。

但是对于一种设计技术来说,没有一种固定演进的架构和设计,那么项目的整个设计层次总是推到重来,从本质上说,就是一种低水平重复。

如果总结规律,提炼共性,才能在提升设计层次,在小作坊中取得大成果。

FPGA研发之道(8)架构设计漫谈(三)时钟和复位

接口确定以后,FPGA内部如何规划?

首先需要考虑就是时钟和复位。

时钟:

根据时钟的分类,可以分为逻辑时钟,接口时钟,存储器时钟等;

(1)逻辑时钟取决与逻辑的关键路径,最终值是设计和优化的结果,从经验而不是实际出发:

低端FPGA(cyclonespantan)工作频率在40-80Mhz之间,而高端器件(stratixvirtex)可达100-200Mhz之间,根据各系列的先后性能会有所提升,但不是**性的。

(2)接口时钟,异步信号的时序一般也是通过FPG**内同步逻辑产生,一般需要同步化,即接口的同步化采样。

某些接口的同步时钟一般是固定而精确的,例如下表所示,如SERDES的时钟尽量由该BANK的专用时钟管脚输入,这样可保证一组SERDES组成的高速接口时钟偏斜一致。

接口名称

IP输入时钟

备注

MII

25Mhz

RGMII/GMII

125Mhz

XAUI

156.25Mhz

差分

IP内部倍频使用

PCI

33Mhz

PCI-e

100Mz

差分输入

IP内部倍频使用

(3)外部存储器时钟:

这里时钟主要为LPDDR/DDR2/DDR3等器件的时钟,一般来说FPGA的接口不用工作在相应器件的最高频率。

能够满足系统缓存数据的性能即可,但是一般这些IP的接口都规定了相应的最小时钟频率,因为这些接口状态机需不停进行外部器件的刷新(充电),过低的频率可能会引起刷新的问题,造成数据丢失或者不稳定。

(4)另外一些需要输出的低速时钟,例如I2C、MDIO、低速采样等操作,可以通过内部分频得到。

不用通过PLL/DCM产生所需时钟。

在XILINX的FPGA中,禁止PLL产生的时钟直接输出到管脚上,而ALTERA的器件可以如此操作。

解决此类问题的方法可通过ODDR器件通过时钟及其180度相位时钟(反向)接入的时钟管脚分别采样0、1逻辑得到。

因为有了DCM/PLL这些专用产生时钟的器件,似乎产生任意时钟输出都是可能是,但实际例化的结果,时钟的输出只能选取某些范围和某些频率,取决于输入时钟和分频系数,CLK_OUT=CLK_IN*(M/N)。

这些分频系数基本取整数,其产生的频率也是有限的值。

复位:

根据复位的分类,FPGA内部复位可以分为硬复位,逻辑复位、软复位等;

硬复位:

故名思议,即外部引脚引入的复位,可以在上电时给入,使整个FPGA逻辑配置完成后,能够达到稳定的状态,这种复位重要性在于复杂单板上除了FPGA外,可能还有多个器件(CPU、DSP),其上电顺序不同,在未完成全部上电之前,其工作状态为不稳定状态。

这种复位引脚可以通过专用时钟管脚引入,也可通过普通I/O引入,一般由单板MCU或者CPLD给出。

逻辑复位:

则是由FPGA内部逻辑产生,例如可以通过计数产生,等待一段时间开始工作,一般等待外部某些信号准备好,另一种FPGA内部逻辑准备好的状态信号,常见的有DCM/PLL的LOCK信号;只有内部各逻辑准备好后,FPGA才能正常工作。

另外FPGA内部如设计逻辑的看门狗的话,其产生的复位属于这个层次。

软复位:

严格的说,应属于调试接口,指FPGA接收外部指令产生的复位信号,用于复位某些模块,用于定位和排除问题,也属于可测性设计的一部分。

例如FPGA通过EMIF接口与CPU连接,内部设定软复位寄存器,CPU通过写此寄存器可以复位FPGA内部单元逻辑,通过写内部寄存器进行软复位,是复杂IP常用的功能接口。

调试时,FPGA返回错误或无返回,通过软复位能否恢复,可以迅速定位分割问题,加快调试速度。

复位一般通过与或者或的方式(高电平或、低电平与),产生统一的复位给各模块使用。

模块软复位信号,只在本模块内部使用。

问题:

同步复位好、还是异步复位好?

XILINX虽然推荐同步复位,但也不一概而论,复位的目的是使整个系统处于初始状态,这根据个人写代码经验,这些操作都可以,前提是整个设计为同步设计,时钟域之间相互隔开,复位信号足够长,而不是毛刺。

下面推荐一种异步复位的同步化方式,其电路图如下:

时钟和复位基本上每个模块的基本输入,也是FPGA架构上首先要规划的部分,而不要用到才考虑,搞的整个设计到处例化DCM或者输出LOCK进行复位,这些对于工程的可维护性和问题定位都没有益处。

《治家格言》说:

“宜未雨而绸缪,毋临渴而掘井。

这与FPGA时钟和复位的规划是同一个意思。

搜索更多相关主题的帖子:

FPGA 转载

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 复位

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《崔万志演讲观后感》.docx

《崔万志演讲观后感》.docx