第八章 数模模数转换电路.docx

第八章 数模模数转换电路.docx

- 文档编号:27284898

- 上传时间:2023-06-28

- 格式:DOCX

- 页数:12

- 大小:199.39KB

第八章 数模模数转换电路.docx

《第八章 数模模数转换电路.docx》由会员分享,可在线阅读,更多相关《第八章 数模模数转换电路.docx(12页珍藏版)》请在冰豆网上搜索。

第八章数模模数转换电路

返回前页

到达顶部

到达底部

第八章数模、模数转换电路

8.1D/A转换器

数模转换是将数字量转换为模拟电量(电流或电压),使输出的模拟电量与输入的数字量成正比。

实现这种转换功能的电路叫数模转换器(DAC)。

一,R-2R倒T形电阻网络的特点及转换原理

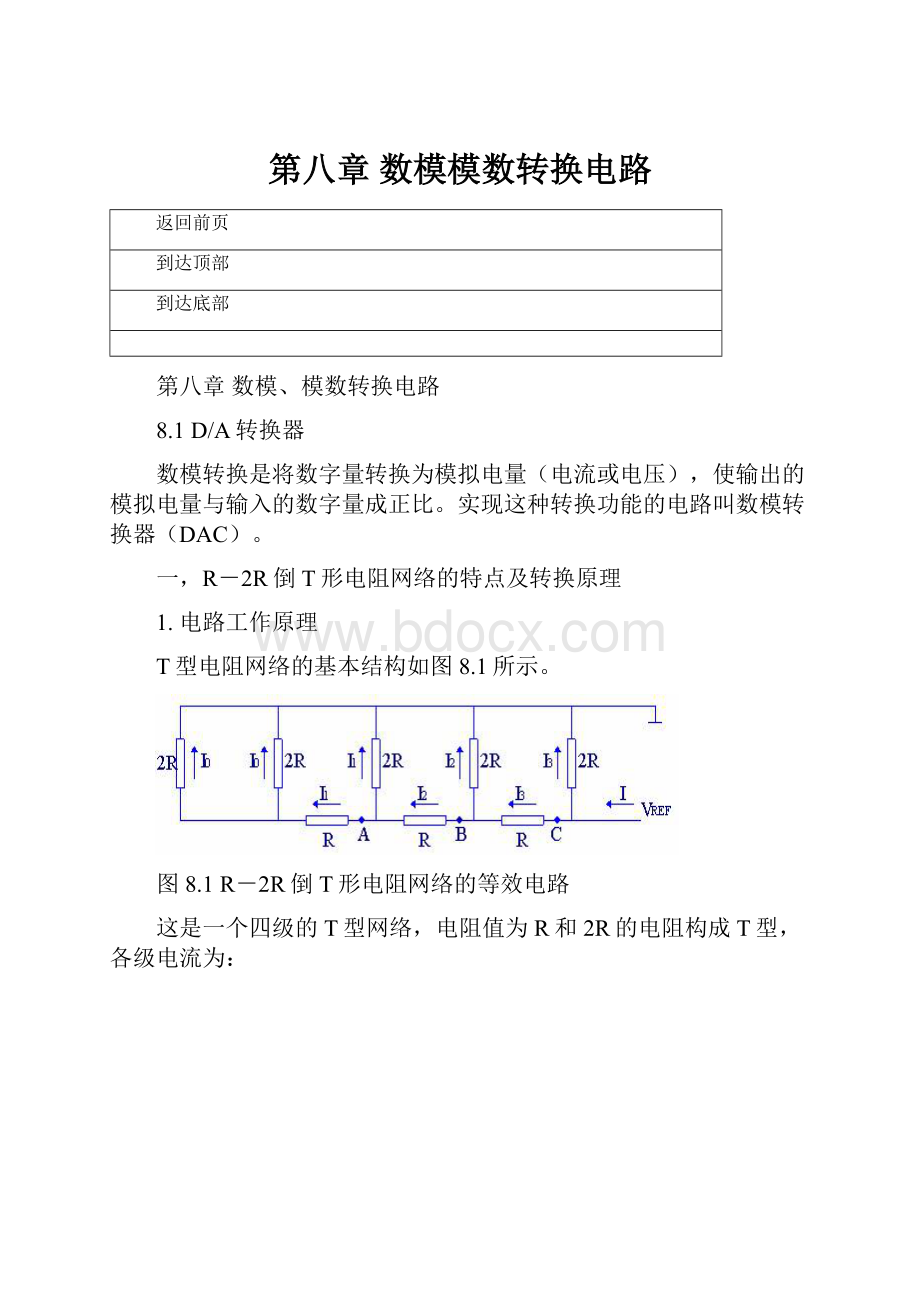

1.电路工作原理

T型电阻网络的基本结构如图8.1所示。

图8.1R-2R倒T形电阻网络的等效电路

这是一个四级的T型网络,电阻值为R和2R的电阻构成T型,各级电流为:

网络可以类推到n级。

这样实现了数字量到模拟量的转换。

T型网络的输出也可以接至运算放大器的同相和反相两个输入端,如图8.2所示。

这种结构也称为倒T型电阻网络D/A转换器。

图8.2倒T型电阻网络D/A转换器

求和运算放大器的输出电压为:

RF=R时

倒T形电阻网络由于流过各支路的电流恒定不变,故在开关状态变化时,不需电流建立时间,所以该电路转换速度高,在数模转换器中被广泛采用。

二、电子模拟开关

在各种D/A转换器中,几乎都要用到电子模拟开关。

例如T型网络中的S0~S3就是电子模拟转换开关,这些开关的输入信号是数字信号,即只有0和1两个状态。

下图为COMS模拟开关的电路原理图。

图8.3COMS模拟开关

在图8.3中,V1、V2、V3和保护二极管D组成输入级,V4、V5和V6、V7组成两级反相器。

两级反相器的输出信号总是相反的,它们分别去控制输出管V8、V9,因此V8和V9总是一个导通一个截止。

三、D/A转换器的主要技术参数

1.分辨率

分辨率是指D/A转换器模拟输出所能产生的最小电压变化量与满刻度输出电压之比。

对于一个n位的D/A转换器,分辨率可表示为

,

为满刻度电压,

为输入高位为零只有最低位为1时输出电压。

分辨率与D/A转换器的位数有关,位数越多,能够分辨的最小输出电压变化量就越小。

2.转换精度

转换精度是指D/A转换器实际输出的模拟电压与理论输出模拟电压的最大误差。

通常要求D/A转换器的误差小于ULSB/2。

3.转换速度

转换速度是指从送入数字信号起,到输出电流或电压达到稳态值所需要的时间。

因此也称输出建立时间。

有时产品手册上也给出输出上升到满刻度的某一百分数所需时间作为输出建立时间,如数字输入从全0边为全1到输出到达稳态值的±1/2LSB所需时间。

对于T型电阻网络D/A转换器转换时间t大约为几百毫秒、几微秒。

D/A转换器的技术指标还有其他一些。

如线形度,输入高、低逻辑电平值,温度系数,输出范围,功率消耗等。

四、集成D/A转换器

1.DAC0832

DAC0832是CMOS工艺,共20管引脚,其管脚排列如图8.4所示。

图8.4DAC0832管脚排列图

各管脚功能为:

D7~D0:

八位数字量输入端,D7为最高位,D0为最低位。

I0l:

模拟电流输出1端,当DAC寄存器为全1时,I0l最大;全0时,I0l最小。

I02:

模拟电流输出2端,I0l+I02=常数=

一般接地。

Rf:

为外接运放提供的反馈电阻引出端。

VREF:

是基准电压参考端,其电压范围为–10V~+l0V。

VCC:

电源电压,一般为+5V~+15V。

DGND:

数字电路接地端。

AGND:

模拟电路接地端,通常与DGND相连。

:

片选信号,低电平有效。

ILE:

输入锁存使能端,高电平有效。

它与

、

信号共同控制输入寄存器选通。

:

写信号1,低电平有效。

当

=0,ILE=1时,

此时才能把数据总线上的数据输入寄存器中。

:

写信号2,低电平有效。

与

配合,当二者均为0时,将输入寄存器中当前的值写入DAC寄存器中。

:

控制传送信号输入端,低电平有效。

用来控制

选通DAC寄存器。

由于DAC0832转换输出是电流,所以,当要求转换结果不是电流而是电压时,可以在DAC0832的输出端接一运算放大器,将电流信号转换成电压信号。

2.CDA7524

CDA7524是CMOS8位并行D/A转换器。

电源电压VDD可在+5~+15V之间选择。

包含有电阻网络和电子模拟开关及数据锁存器,还有片选控制和数据输入控制端,便于和微处理器进行接口的D/A转换器,多用于微机控制系统中。

其工作原理图见图8.5所示.

图8.5CDA7524的工作原理图

8.2A/D转换器

一、A/D转换的一般过程

1.采样一保持

采样是对模拟信号进行周期性地抽取样值的过程,就是把随时间连续变化的信号转换成在时间上断续、在幅度上等于采样时间内模拟信号大小的一串脉冲。

图8.6表明了采样过程。

UI是输入模拟信号,UO是采样输出信号。

如果采样周期很短,采样时间极小,则所得采样值序列即可代表原模拟信号。

为了能不失真地恢复原模拟信号,采样频率应不小于输人模拟信号频谱中最高频率的两倍,即:

。

图8.6模拟信号的采样

由于A/D转换需要一定的时间,所以在每次采样结束后,应保持采样电压值在一段时间内不变,直到下一次采样开始。

这就要在采样后加上保持电路,实际采样一保持是做成一个电路。

采样—保持电路基本组成如图8.7所示,US是采样脉冲信号。

电路由一个存储样值的电容C,一个场效应管T构成的电子模拟开关及电压跟随运算放大器组成。

图8.7基本采样—保持电路

2量化与编码

经采样保持所得电压信号仍是模拟量,不是数字量。

那么量化和编码就是从模拟量产生数字量的过程,亦即A/D转换的主要阶段。

量化是将采样—保持电路的输出信号进行离散化的过程。

离散后的电平称为量化电平。

用二进制数表示量化电平即为编码。

划分量化电平的两种方法:

(a)量化误差大(b)量化误差小

二、逐次逼近型A/D转换器

图8.8逐次逼近型A/D转换器原理图

图示电路由5个D触发器和门G1

G4构成控制逻辑电路,其中5个D触发器组成环形移位寄存器;3个RS钟控触发器做为逐次逼近寄存器;三位DAC用来产生反馈参考(比较)电压Uf;门G7

G9输出三位数字量D2D1D0;C为电压比较器。

三、A/D转换器的重要技术参数

1.分辨率

分辨率是指A/D转换器输出数字量的最低位变化一个数码时,对应输入模拟量的变化量。

ADC的位数越多,量化的阶梯越小,分辨率也就越高。

分辨率常以输出二进制码的位数来表示。

2.相对精度

相对精度是指A/D转换器实际输出数字量与理论输出数字量之间的最大差值。

通常用最低有效位LSB的倍数来表示。

如相对精度不大于(1/2)LSB,就说明实际输出数字量与理论输出数字量的最大误差不超过(1/2)LSB。

3.转换速度

转换速度是指A/D转换器完成一次转换所需要的时间,即从转换开始到输出端出现稳定的数字信号所需要的时间。

四、集成A/D转换器

1.ADC0809是8位A/D转换器,它的转换方法为逐次逼近法。

ADC0809为CMOS工艺,其管脚为28脚,管脚排列如图8.9所示。

各个管脚的功能如下:

INo~IN7:

八个模拟量输入端。

START:

启动A/D转换,当START为高电平时,开始A/D转换。

EOC:

转换结束信号。

当A/D转换完毕之后,发出一个正脉冲,表示A/D转换结束,此信号可用做

A/D转换是否结束的检测信号或中断申请信号(加一个反相器)。

C、B、A:

通道号地址输入端,C、B、A为二进制数输入,C为最高位,A为最低位,CBA从000~111分别选中通道IN0~IN7。

ALE:

地址锁存信号,高电平有效。

当ALE为高电平时,允许C、B、A所示的通道被选中,并把该

通道的模拟量接入A/D转换器。

CLOCK:

外部时钟脉冲输入端,改变外接R、C可改变时钟频率。

D7~D0:

数字量输出端。

D7为高位。

VREF(+),VREF(—):

参考电压端子,用来提供D/A转换器权电阻的标准电平。

一般VREF(+)=5V,

VREF(—)=0V

Vcc:

电源电压,+5V。

GND:

接地端。

图8.9ADC0809管脚排列图

ADC0809可以进行八路A/D转换,并且这种器件使用时无需进行调零和满量程调整,转换速度和精度属中高档,售价又不贵。

所以,一般控制场合采用这些ADC0809(或0800系列)的A/D转换片是比较理想的。

2.CAD571

它由10位D/A转换器、10位逐次逼近寄存器及时钟发生器、比较器、三态输出缓冲器、基准电压和控制逻辑等电路组成。

它的特点是内部有时钟发生器和基准电压电路,故不需外接时钟脉冲和基准电压VREF,并能与计算机接口,使用非常方便。

CAD571内部结构原理图见图8.10所示。

图8.10CAD571内部结构原理图

逻辑代数基础

门电路

组合逻辑电路

触发器

时序逻辑电路

寄存器、存储器和

可编程逻辑器件

脉冲信号的产生与整形

数模、模数转换电路

窗体底端

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 第八章 数模模数转换电路 第八 数模 转换 电路

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《C12343098汽轮机操作规程》要点.docx

《C12343098汽轮机操作规程》要点.docx