EDA考试.docx

EDA考试.docx

- 文档编号:27133895

- 上传时间:2023-06-27

- 格式:DOCX

- 页数:18

- 大小:120.84KB

EDA考试.docx

《EDA考试.docx》由会员分享,可在线阅读,更多相关《EDA考试.docx(18页珍藏版)》请在冰豆网上搜索。

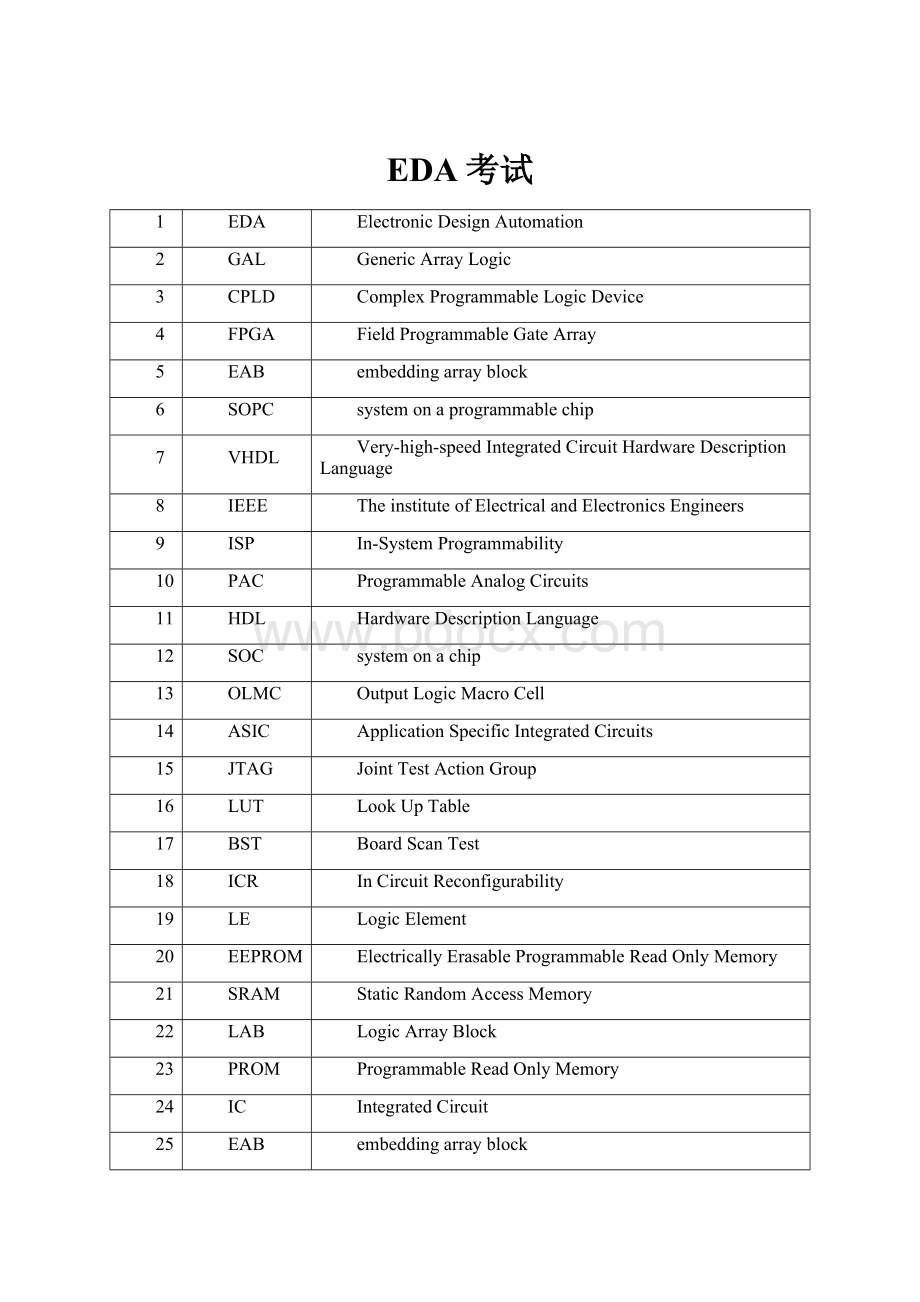

EDA考试

1

EDA

ElectronicDesignAutomation

2

GAL

GenericArrayLogic

3

CPLD

ComplexProgrammableLogicDevice

4

FPGA

FieldProgrammableGateArray

5

EAB

embeddingarrayblock

6

SOPC

systemonaprogrammablechip

7

VHDL

Very-high-speedIntegratedCircuitHardwareDescriptionLanguage

8

IEEE

TheinstituteofElectricalandElectronicsEngineers

9

ISP

In-SystemProgrammability

10

PAC

ProgrammableAnalogCircuits

11

HDL

HardwareDescriptionLanguage

12

SOC

systemonachip

13

OLMC

OutputLogicMacroCell

14

ASIC

ApplicationSpecificIntegratedCircuits

15

JTAG

JointTestActionGroup

16

LUT

LookUpTable

17

BST

BoardScanTest

18

ICR

InCircuitReconfigurability

19

LE

LogicElement

20

EEPROM

ElectricallyErasableProgrammableReadOnlyMemory

21

SRAM

StaticRandomAccessMemory

22

LAB

LogicArrayBlock

23

PROM

ProgrammableReadOnlyMemory

24

IC

IntegratedCircuit

25

EAB

embeddingarrayblock

26

IP

IntellectualProperty

27

PLA

ProgrammableLogicArray

28

GRP

GlobalRoutingPool

29

PIA

ProgrammableInterconnectArray

二、改错题

指出下列程序设计元件的中文名,指出语法错误并改正,给出改正后的时序图:

1、

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT4BIS

PORT(CLK,RST,ENA:

INSTD_LOGIC;

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC);

ENDCNT4B;

ARCHITECTUREbehavOFCNT4BIS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(CLK,RST,ENA)

BEGIN

IFRST='1'THENCQI<= '0000'; ………………………………………………… "0000"

ELSIFCLK'EVENTANDCLK='1'THEN

IFENA= "1" THENCQI<=CQI+1; ……………………………………………………'1'

ELSECQI<="0000";

ENDIF; ……………………………………………………………………ENDIF;

OUTY<=CQI;

ENDPROCESS;

COUT<=CQI(0)ANDCQI

(1)ANDCQI

(2)ANDCQI(3);

ENDbehav;

含异步清0和同步时钟使能的4位加法计数器

2、

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADDER8IS

PORT(CIN:

INSTD_LOGIC;

A,B:

INSTD_LOGIC_VECTOR(7DOWNTO0);

S:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);

COUT:

OUTSTD_LOGIC_VECTOR );

ENDADDER8;

ARCHITECTUREbehavOFADDER8IS

SIGNALSINT:

OUT STD_LOGIC_VECTOR(8DOWNTO0); …………………………………BEGIN

SINT :

= ('0'&A)+B+CIN; …………………………………………………………<=

S<=SINT(7DOWNTO0);

COUT<=SINT(8);

ENDbehav;

8位硬件加法器

3、

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCLK_6DIS

PORT(CLK,RST:

INSTD_LOGIC;

CLK_OUT:

OUTSTD_LOGIC);

ENDCLK_6D;

ARCHITECTUREONEOFCLK_6DIS

VARIABLE TEMP:

STD_LOGIC; ………………………………………………………………………SIGNAL

BEGIN

PROCESS(CLK)

VARIABLECNT6D:

INTEGERRANGE0TO3;

CONSTANTSIGN:

INTEGER:

=2;

BEGIN

IF(RST= “1”)THENTEMP<= “0”; …………………………………………… '1','0'

ELSIF CLK'EVENTANDCLK='1' THEN…………………………………… (CLK'EVENTANDCLK='1')

IF(CNT6D=SIGN)THEN

CNT6D:

=0;

TEMP<=NOTTEMP;

ELSECNT6D:

=CNT6D+1;

ENDIF;

ENDIF;

ENDPROCESS;

CLK_OUT<=TEMP;

ENDONE;

六分频电路

电路时序图:

4、

libraryieee;

useieee.std_logic_1164.all;

entityencoderis

port(b:

instd_logic(7downto0);………………………… b:

instd_logic_vector(7downto0)

y:

outstd_logic(2downto0));……………………………… y:

outstd_logic_vector(2downto0)

endencoder;

architectureoneofencoderis

begin

process (b)

begin

casebis

when"01111111"=>y<="111";

when"10111111"=>y<="110";

when"11011111"=>y<="101";

when"11101111"=>y<="100";

when"11110111"=>y<="011";

when"11111011"=>y<="010";

when"11111101"=>y<="001";

when"11111110"=>y<="000";

whenothers=>null;

endcase;

endprocess;

endone;

8-3线译码器

5、

libraryieee;

useieee.std_logic_1164;…………………………………………………………… 少.all;

entitypisois

port(reset,clock:

instd_logic;

parallelnum:

instd_logic_vector(3downto0);

serialout:

outstd_logic);

end;

architectureconvertofpisois

begin

process(clock)

variablei:

integerrange0to3;

begin

ifreset='1'then

i:

=0;

elsifrising_edge(clock)then

serialout<=parallelnum(i);

ifi<3then

i:

=i+1;

else

i:

=0;

endif;

endif;

…………………………………………………………………………………少endprocess;

end;

并串转换

6、

libraryieee;

useieee.std_logic_1164.all;

entityis ……………………………………………………… 少FreDevider

port(Clkin:

instd_logic;

Clkout:

outstd_logic

);

end;

architectureDeviderofFreDevideris

constantN:

integer:

=3;

signalcounter:

integerRANGE0TON;

signalClk:

std_logic;

begin

process(Clkin)

begin

IFrising_edge(Clkin)then

IFcounter=Nthen

Counter<=0;

Clk<=NotClk;

Else

Counter<=Counter+1;

EndIF;

……………………………………………………………………………少EndIF;

Endprocess;

Clkout<=Clk;

End;

8分频

7、

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcounterIS

PORT(reset:

INSTD_LOGIC;

clock:

INSTD_LOGIC;

num:

bufferintegerrange0to3;………………………………………………… 多一个“;”

);

END;

ARCHITECTUREbehavOFjishuIS…………………………………………. jishu改为 counter

Begin

Process(reset,clock)

Begin

Ifreset=’1’then

num<=0;

Elsifrising_edge(clock)then

Ifnum=3then

num<=0;

else

num<=num+1;

……………………………………………………………………………… 少endif;

endif;

endprocess;

end;

功能:

4进制计数器

8、

………………………………………………………………………………………… 少LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYMUXIS

PORT(

Data0,Data1,Data2,Data3:

INStd_Logic_Vector(7downto0);

sel:

INSTD_Logic_Vector(1downto0);

DOUT:

OUTStd_Logic_Vector(7downto0)

);

END;

ARCHITECTUREDATAflowOFMUXIS

BEGIN

ifselSELECT …………………………………………………………………………if改为WITH

DOUT<=Data0WHEN“00”,

Data1WHEN“01”,

Data2WHEN“10”,

Data3WHEN“11”,

“00000000”WHENOTHERS;

END;

功能:

8路4选1复用器

9、给出下列程序设计元件实现的功能,简要分析工作原理或画出时序图,指出语法错误并改正。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYLX3_1IS

PORT(s2,s1,s0:

INSTD_LOGIC;

d3,d2,d1,d0:

INSTD_LOGIC;

d7,d6,d5,d4:

INSTD_LOGIC;

y:

OUTSTD_LOGIC);

………………………………………………………………………………………………ENDLX3_1;

ARCHITECTUREoneOF LX8_1 IS ……………………………………………………………LX3_1

SIGNALs:

STD_LOGIC(1DOWNTO0); ……………………………STD_LOGIC_VECTOR(2DOWNTO0)

BEGIN

S:

=s2&s1&s0;………………………………………………………………………………………… <=

y<=d0WHENs="000"ELSE

d1WHENs="001"ELSE

d2WHENs="010"ELSE

d3WHENs="011"ELSE

d4WHENs="100"ELSE

d5WHENs="101"ELSE

d6WHENs="110"ELSE

d7;

ENDone;

功能:

8选1数据选择器

工作原理:

d7~d0是数据输入端,s2、s1和s0是控制输入端,Y是数据输入端。

当s2s1s0=000时,d0数据被选中,输出y=d0;当s2s1s0=001时,d1数据被选中,输出y=d1;依次类推。

10、

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED; ………………………………… STD_LOGIC_UNSIGNED.ALL

ENTITYLX3_2IS

PORT(CLK,CLR,OE:

INBIT;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

Q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDLX3_2;

ARCHITECTUREstrucOFLX3_2IS

VARIABLE Q_TEMP:

STD_LOGIC_VECTOR(7DOWNTO0); …………………………………………SIGNAL

BEGIN

PROCESS(CLR) ………………………………………………………………………… PROCESS(CLK)

BEGIN

IFCLR='0'THENQ_TEMP<='00000000'; ………………………………………………… "00000000"

ELSIFCLK='1'THEN

Q_TEMP<=D;

ELSEQ_TEMP<=Q_TEMP;

ENDIF;

ENDPROCESS;

Q<=Q_TEMPWHENOE='1'ELSE

"ZZZZZZZZ";

………………………………………………………………………………….. ENDstruc;

功能:

带三态输出的8位D锁存器

时序图:

(根据给出的输入测试向量画出输出Q的时序图)

11、

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED; ……………………….. USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYLX3_2IS

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

B:

IN STD_LOGIC(3DOWNTO0);…………………………………………………… STD_LOGIC_VECTOR

GT,LT,EQ:

OUTSTD_LOGIC);

ENDLX3_2;

ARCHITECTUREoneOF LX8_2 IS………………………………………………………………LX3_2

BEGIN

PROCESS(A,B)

BEGIN

GT<='0';

LT<='0';

EQ<='0';

IFA>BTHENGT<=”0”; ………………………………………………………………………….'0'

ELSIFA ELSEEQ<=”0”; …………………………………………………………………………………….. '0' ENDIF; ENDPROCESS; ENDone; 功能: 4位二进制数据比较器 工作原理: A[3..0]和B[3..0]是两个4位二进制数输入,当A>B时,大于输出端GT=1;当A 12、 LIBRARYIEEE; USEIEEE.STD_LOGIC_1164.ALL; USEIEEE.STD_LOGIC_UNSIGNED.ALL; ENTITYLX3_3IS PORT(CLK,RST,ENA: INSTD_LOGIC; Q: OUTSTD_LOGIC_VECTOR(7DOWNTO0); COUT: OUTSTD_LOGIC); ENDLX3_3; ARCHITECTUREoneOFLX3_3IS VARIABLE QI: STD_LOGIC_VECTOR(7DOWNTO0);…………………………………………………… SIGNAL BEGIN PROCESS(RST,ENA) ………………………………………………………………… PROCESS(CLK,RST,ENA) BEGIN IF RST=”1” THENQI<="00000000";……………………………………………………………… RST='1' ELSIFCLK'EVENT OR CLK='1'THEN……………………………………………………………………AND IFENA='1'THEN QI<=QI+1; ENDIF; ENDIF; Q<=QI; ENDPROCESS; COUT<=QI(0)ANDQI (1)ANDQI (2)ANDQI(3)ANDQI(4)ANDQI(5)ANDQI(6)ANDQI(7); ENDone; 功能: 带复位和使能控制的8位二进制加法计数器 工作原理: CLK是时钟输入端。 RST是复位控制输入端,当RST=1时,计数器被复位。 ENA是使能控制输入端,当ENA=1时,计数器工作,当ENA=0时,计数器状态不变(保持)。 在EN1=1和RST=0时,电路每接到一个CLK时钟的上升沿,计数器状态加1。 当计数器状态为“11111111”(最大值)时,进位输出COUT=1,产生向高位的进位。 1、简述电子设计技术的发展 电子设计技术的发展: 应用SSI数字电路芯片 应用MCU微控制器or单片机(电子系统智能化) FPGA/CPLD现场可编程/复杂可编程逻辑器件(EDA基础) 2、图示阵列完成的是什么功能? 3、简述自顶向下的系统设计方法 自顶向下(top-to-down): 基于EDA技术 顶: ? 系统功能 向下: 系统分为若干功能模块 步骤: 1.采用完全独立于目标芯片物理结构的硬件描述语言HDL(HardwareDescriptionLanguage),对系统的基本功能(行为)进行描述和定义。 2.多层次仿真,完成功能确认。 3.功能描述——具体目标芯片的网表文件。 4.逻辑映射,布局布线。 5.利用仿真文件进行功能、时序验证——确保系统性能。 4、菊花链下载时,器件位置如何确定? 在串行片数不超出接口的驱动能力时,器件位置由器件识别码确定器件前后芯片内存储器短路 5、端口模式有几种? IN OUT INOUT BUFFER 6、简述在系统编程技术的特点 特点: 不用编程器,直接在用户的目标系统中或线路板上直接对PLD器件编程 1、装配后编程下载 2、根据需要对系统的硬件功能实时加以修改 3、不改变系统硬件结构情况下,重构逻辑 4、系统不停止工作时进行远程硬件升级 7、简述EDA工具的FPGA/CPLD开发流程 8、设计时怎样选择CPLD和FPGA器件 1、I/O口定义: 资源是否够用。 2、逻辑资源: GLB 查阅宏单元库(门、触发器、计数器、MUX等,约200种)。 3、方程实现部分的估算。 4、资源利用率: (取50%) 9、指出时序电路描述定义方式,给出CLK信号上升沿检测语句 用不完整条件语句定义时序电路: CLK'EVENTANDCLK='1' risen_edge(CLK) 10、指出端口模式BUFFER与INOUT的不同之处 INOUT: 输入输出端口。 BUFFER: 只能将输出的数据反馈输入,不能输入外部数据 11、给出PROM、FPLA、PAL、GAL结构异同点 与阵列 或阵列 输出电路 PROM 固定 可编程 固定 PLA 可编程 可编程 固定 PAL 可编程 固定 固定 GAL 可编程 固定 可组态 12、给出CPLD和FPGA的主要异同 CPLD: 基于乘积项,编程。 FPGA: 基于查找表,配置 13、给出信号、变量的异同点。 数据对象 基本用法 适用范围 赋值表示和特性 Signal 电路中信号连线 整个结构体内 <=进程最后赋值 Variable 进程中数据存储 进程中使用 : =立即赋值 14、列举5条以上VDHL与计算机语言的主要不同之处 VHDL是硬件描述语言,用于硬件器件的设计; 实体定义元件的输入输出接口;结构体定义元件的行为逻辑功能;数据对象信号用于描述电路中信号连线;进程必须由敏感信号的变化来启动;信号上升下降沿事件监测;用不完整条件语句定义时序电路;仿真延时δ、固有延时和传输延时赋值

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 考试

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《崔万志演讲观后感》.docx

《崔万志演讲观后感》.docx