IDE接口协议.docx

IDE接口协议.docx

- 文档编号:26907792

- 上传时间:2023-06-24

- 格式:DOCX

- 页数:12

- 大小:60.46KB

IDE接口协议.docx

《IDE接口协议.docx》由会员分享,可在线阅读,更多相关《IDE接口协议.docx(12页珍藏版)》请在冰豆网上搜索。

IDE接口协议

基于FPGA的IDE硬盘接口卡的实现

摘要:

本文介绍了一种基于FPGA技术的IDE硬盘接口的设计。

该卡提供两个符合ATA-6规范的接口,采用FPGA实现了两套IDE接口功能,设计支持PIO和Ultra DMA传输模式,文章侧重于介绍用FPGA实现IDE接口协议的具体方法。

关键词:

FPGA;硬盘;IDE接口

引言

本文采用FPGA实现了IDE硬盘接口协议。

系统提供两套符合ATA-6规范的IDE接口,一个与普通IDE硬盘连接,另一个与计算机主板上的IDE接口相连。

系统采用FPGA实现接口协议,完成接口数据的截获、处理(在本文中主要是数据加密)和转发,支持PIO和UltraDMA两种数据传输模式。

下面重点介绍用FPGA实现接口协议的方法。

1IDE接口协议简介

1.1IDE接口引脚定义

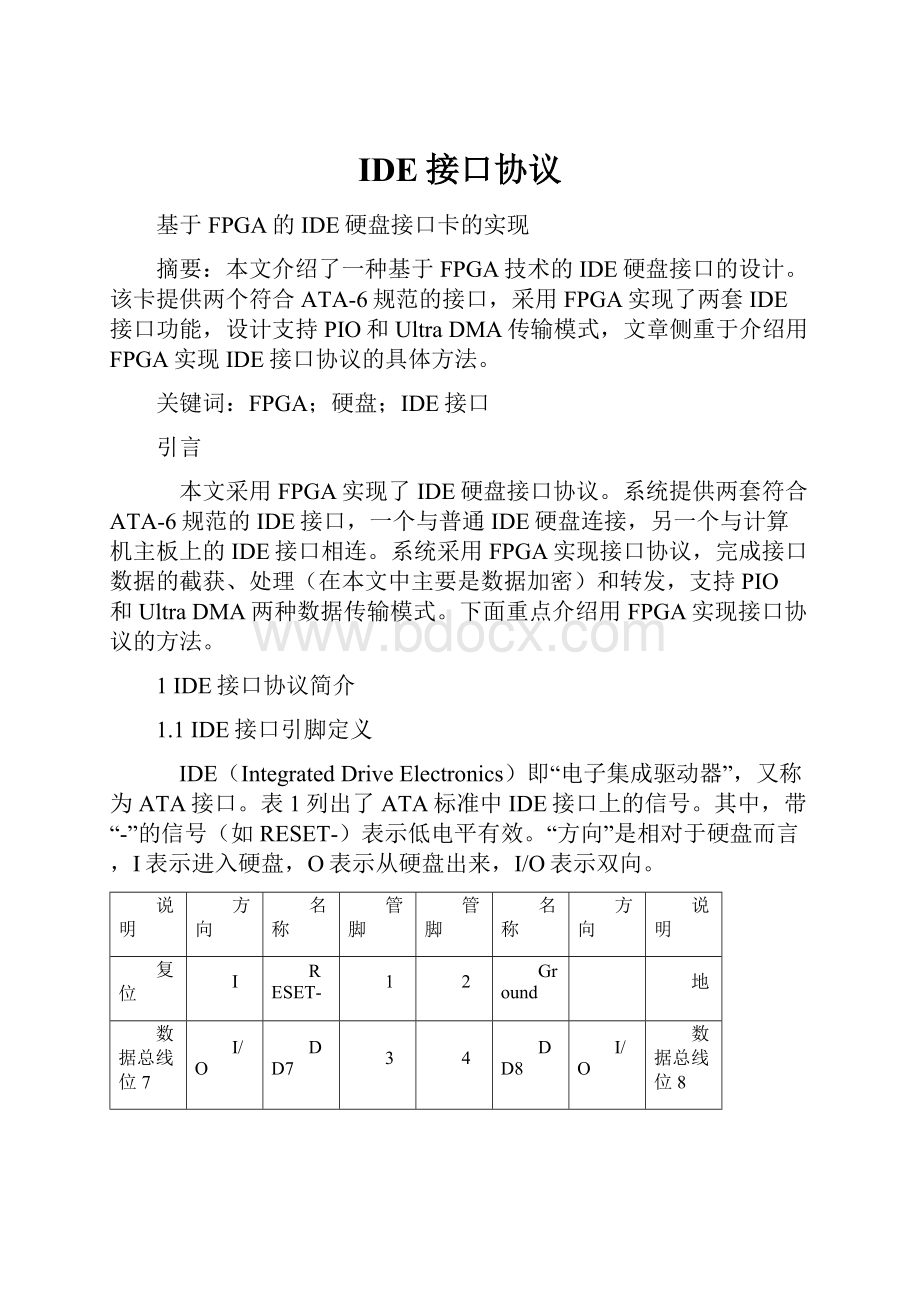

IDE(IntegratedDriveElectronics)即“电子集成驱动器”,又称为ATA接口。

表1列出了ATA标准中IDE接口上的信号。

其中,带“-”的信号(如RESET-)表示低电平有效。

“方向”是相对于硬盘而言,I表示进入硬盘,O表示从硬盘出来,I/O表示双向。

说 明

方向

名称

管脚

管脚

名称

方向

说 明

复位

I

RESET-

1

2

Ground

地

数据总线位7

I/O

DD7

3

4

DD8

I/O

数据总线位8

数据总线位6

I/O

DD6

5

6

DD9

I/O

数据总线位9

数据总线位5

I/O

DD5

7

8

DD10

I/O

数据总线位10

数据总线位4

I/O

DD4

9

10

DD11

I/O

数据总线位11

数据总线位3

I/O

DD3

11

12

DD12

I/O

数据总线位12

数据总线位2

I/O

DD2

13

14

DD13

I/O

数据总线位13

数据总线位1

I/O

DD1

15

16

DD14

I/O

数据总线位14

数据总线位0

I/O

DD0

17

18

DD15

I/O

数据总线位15

地

Ground

19

20

N.C.

DMA请求

O

DMARQ

21

22

Ground

地

I/O写

I

DIOW-

23

24

Ground

地

I/O读

I

DIOR-

25

26

Ground

地

I/O通道准备好

O

IORDY

27

28

CSEL

(见注1)

DMA确认

I

DMACK-

29

30

Ground

地

中断请求

O

INTRQ

31

32

N.C.

(ATA-2中使用)

地址位1

I

DA1

33

34

PDIAG-

(见注2)

地址位0

I

DA0

35

36

DA2

I

地址位2

片选0

I

CS0-

37

38

CS1-

I

片选1

驱动器状态

O

DASP-

39

40

Ground

地

注:

1、CSEL:

一条排线上有两个存储设备时,通过该信号确定某存储设备为设备0(主设备)或设备1(从设备)。

2、PDIAG-/CBLID-:

一条排线上有两个存储设备时,设备1通知设备0,设备1已检测通过。

该引脚也用于确定是否有80芯的排线连接到接口上。

表1:

IDE接口引脚定义

1.2IDE控制器的寄存器组

主机对IDE硬盘的控制是通过硬盘控制器上的两组寄存器来实现的。

一组为命令寄存器组;另一组为控制/诊断寄存器,如表2所示。

地 址

名 称 及 意 义

CS1-

CS0-

DA2

DA1

DA0

读操作

写操作

命 令 寄 存 器 组

1

0

0

0

0

数据寄存器

数据寄存器

1

0

0

0

1

错误寄存器

特征寄存器

1

0

0

1

0

扇区数寄存器

扇区数寄存器

1

0

0

1

1

扇区号寄存器

扇区号寄存器

1

0

1

0

0

柱面数低8位

柱面数低8位

1

0

1

0

1

柱面数高8位

柱面数高8位

1

0

1

1

0

驱动器/磁头寄存器

驱动器/磁头寄存器

1

0

1

1

1

状态寄存器

命令寄存器

控 制 / 诊 断 寄 存 器 组

0

1

1

1

0

辅助状态寄存器

设备控制寄存器

数 据 端 口 (用于DMA模式,DMACK-有效后启用)

1

1

*

*

*

数据端口

数据端口

表2寄存器组

特征寄存器中的内容作为命令的一个参数,其作用随命令而变。

扇区数寄存器指示该次命令所需传输数据的扇区数。

扇区号寄存器、柱面数寄存器(低、高)、驱动器/磁头寄存器三者合称为介质地址寄存器,指示该次命令所需传输数据首扇区的地址,寻址方式可以用“柱面/磁头/扇区(CHS)”或“逻辑块地址(LBA)”方式,在驱动器/磁头寄存器中指定。

命令寄存器存储执行的命令代码。

当向命令寄存器写入命令时,相关的参数必须先写入。

命令写入后,硬盘立即开始命令的执行。

状态寄存器保存硬盘执行命令后的结果,供主机读取。

其主要位有:

BSY-驱动器忙,DRDY-驱动器准备好,DF-驱动器故障,DRQ-数据请求,ERR-命令执行出错。

辅助状态寄存器与状态寄存器的内容完全相同,但读该寄存器时不清除中断请求。

错误寄存器包含了命令执行出错时硬盘的诊断信息。

数据寄存器为PIO传输模式下,主机和硬盘控制器的缓冲区之间进行数据交换的寄存器。

数据端口为DMA传输模式下专用的数据传输通道。

1.3IDE数据传输方式

IDE接口的数据传输包括PIO和DMA两种方式。

PIO模式是硬盘数据传输的基本方式。

在PIO方式下,数据的传输以数据块(1个或者多个扇区)为单位,每传输完一个数据块后,硬盘都会产生一个中断请求,并向主机报告命令执行结果。

在DMA方式下,主机和硬盘之间需要通过一系列握手信号建立一个DMA通道,数据以数据流的形式传输。

当传输完一个命令的所有数据时,硬盘产生一个中断请求,并向主机报告命令执行结果。

DMA方式又分为UltraDMA和MultiwordDMA两种。

UltraDMA方式在选通信号的上升沿和下降沿均锁定数据,提高了数据的传输速率,并且在数据传输结束时还要进行CRC校验。

2FPGA内部框图

本设计采用Actel公司的ProASICPLUS系列FPGA芯片,其内部框图如图1所示。

寄存器组一保存从主机写入的命令及命令参数,在控制模块的作用下转发给硬盘。

寄存器组二保存从硬盘读出的命令执行结果,供主机读取。

控制模块负责产生对主机及对硬盘的各种IDE协议控制信号,并协调各模块之间的工作。

控制模块采用状态机的设计方法,其软件设计流程将在下一节中详细介绍。

数据处理单元对数据进行加/解密运算。

缓冲区一、二则作为数据处理单元的输入/输出缓存。

在PIO方式下,数据的处理以数据块为单位,缓冲区充当RAM的作用;在UltraDMA方式下,数据以数据流的形式处理,缓冲区充当FIFO的作用。

3系统软件流程

开机时,FPGA检测到复位信号,初始化内部寄存器组,并对硬盘进行复位操作,硬盘复位完毕后FPGA进入空闲状态。

FPGA在空闲状态时会检测主机是否有写命令操作(通常一个命令的写入,要先写特征寄存器、扇区数寄存器、扇区号寄存器、柱面数低位寄存器、柱面数高位寄存器、驱动器/磁头寄存器6个命令参数寄存器,最后将命令写入命令寄存器)。

当主机依次将寄存器组一写完后,FPGA对主机置BSY位,并将命令转发给硬盘,同时判断命令类型,根据不同的命令,进入相应的命令处理流程。

如果是无数据命令,FPGA等待硬盘命令的执行,命令执行完毕后,硬盘产生一个中断请求,此时FPGA将执行结果读入寄存器组二中,并向主机产生中断请求。

如果是有数据命令,则根据数据传输的模式,分别进入到下述的PIO命令处理流程及UltraDMA命令处理流程。

3.1PIO命令处理流程

以PIO模式传输数据的命令有WriteSectors、WriteMultiple、ReadSectors和ReadMultiple。

当FPGA判断出是PIO模式的数据传输命令时,转向PIO命令处理流程。

下面我们以PIO写操作为例介绍。

FPGA首先查询硬盘的BSY位。

若BSY为0则将硬盘的状态寄存器读入寄存器组二,并查询DRQ位。

若DRQ为1则表明硬盘已准备好接收数据。

此时主机可以向缓冲区一写入数据块(本设计中,我们设定数据块的大小为1个扇区共512字节)。

主机写完一个数据块后FPGA对主机置BSY位,数据处理单元开始进行加密运算,并将加密后的数据写入缓冲区二。

加密运算完成后,FPGA将缓冲区二中的数据写入硬盘数据缓存区,并进入等待状态。

硬盘将数据写入物理介质(磁碟)后会产生一个中断请求,报告已完成该数据块的写操作。

FPGA将执行结果读入寄存器组二中,向主机产生中断请求,并再次查询DRQ位,若DRQ为1则进入下一个PIO数据块的传输过程,若DRQ为0则表示该命令所有数据全部传完,FPGA进入空闲状态。

此外,IdentifyDevice命令是主机以PIO方式从硬盘读出512字节的属性信息(包括硬盘的型号、容量等)。

此时,数据处理单元不应对该命令的数据进行加/解密运算。

3.2UltraDMA命令处理流程

以UltraDMA模式传输数据的命令有WriteDMA和ReadDMA。

下面我们以UltraDMA写操作为例介绍UltraDMA命令处理流程。

DMA传输通道的建立都是由硬盘通过DMARQ来请求的。

FPGA接收到硬盘的DMA请求后首先初始化主机至FPGA的DMA通道,紧接着初始化FPGA至硬盘的DMA通道。

此时主机经FPGA到硬盘的DMA通道即已建立,主机向缓冲区一写入数据,同时数据处理单元对数据进行加密运算,并将加密后的数据写入缓冲区二,FPGA则将缓冲区二中的数据写入硬盘。

在传输过程中,若硬盘要求暂停或者缓冲区二空,则FPGA暂停向硬盘发送数据;若缓冲区一满,则FPGA要求主机暂停发送数据。

图3PIO命令处理流程

主机和硬盘都可以随时停止当前的DMA传输,未传完的数据将等待硬盘下一次的DMA请求时再进行传输。

如果硬盘提出中止传输,FPGA将撤除FPGA至硬盘的DMA通道,同时向主机提出中止传输,撤除主机至FPGA的DMA通道,并计算该次所传数据的CRC校验。

然后FPGA进入等待状态,等待硬盘下一次的DMA请求。

如果主机提出中止传输,FPGA将撤除主机至FPGA的DMA通道,同时继续向硬盘发送数据,直到将接收到主机的数据发送完毕,即缓冲区二空后,向硬盘提出中止传输,撤除FPGA至硬盘的DMA通道,并计算CRC校验。

然后FPGA进入等待状态,等待硬盘下一次的DMA请求。

在等待状态下,若FPGA接收到硬盘的中断请求,则说明该次命令的所有数据已经传完,命令结束。

FPGA将命令执行结果读入寄存器组二,向主机产生中断请求,进入空闲状态。

若接收到硬盘的DMA请求,则说明硬盘还未接收到该次命令的所有数据,此时需要判断主机是否已将所有数据发送完。

如果主机并没有将所有数据发送完,则再次建立FPGA两侧的DMA通道,开始新一轮的DMA传输;如果主机已将所有数据发送完,则重新建立FPGA至硬盘的DMA通道,直到将缓冲区二中的数据发送完,并计算CRC校验。

4结束语

本文采用FPGA实现了两套符合ATA-6规范的IDE接口,完成主机与硬盘之间数据的截获、处理和转发。

经测试,系统在DOS、Windows98、Windows 2000、WindowsXP及RedHatLinux9.0操作系统环境下,使用希捷、迈拓、三星、西数等公司的多种型号硬盘均工作正常,支持PIO和UltraDMA两种数据传输模式。

由于通过FPGA实现一个完整的IDE接口,若对系统稍加改动,如在数据处理单元中加入相应的文件系统,即可实现脱机读写IDE硬盘,用于数据采集的海量存储等多种场合,使系统具有较好的通用性。

本文作者创新点:

作者针对硬盘数据易泄密及高速大容量数据采集困难等问题,提出在主机和硬盘之间使用FPGA芯片构建一个双向IDE硬盘通道,实现两套符合ATA-6规范的IDE接口,FPGA对主机与硬盘间的数据流进行处理及转发,以实现硬盘数据加密、数据高速采集存储及脱机控制硬盘等操作。

系统支持PIO和UltraDMA两种数据传输模式,对操作系统透明,较常见的单向IDE通道,该系统通用性强,有较好的推广价值。

本文侧重于用FPGA实现IDE接口协议,对实现过程及方法做了详细描述,对读者有较高的参考实用价值。

参考文献:

1 T13TechnicalCommittee. InformationTechnology-ATAttachmentwithPackedInterface-6(ATA/ATAPI-6).[S]Revision1e. 2001

2 FriedhelmSchmidt,精英科技译,SCSI总线和IDE接口:

协议、应用和编程(第二版),[M]中国电力出版社,2001.3

3 ActelCorporation. LiberoUser’sGuide. 2004

4 ActelCorporation,ProASICPLUSDatasheet,Versionv3.5,2004.4

5 基于FPGA的高速连续数据采集系统的设计 [J] 黄新财 佃松宜 汪道辉 《微计算机信息》2005年第21卷第2期58页

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- IDE 接口 协议

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《崔万志演讲观后感》.docx

《崔万志演讲观后感》.docx