针对IO的缓冲器版图设计.docx

针对IO的缓冲器版图设计.docx

- 文档编号:26834261

- 上传时间:2023-06-23

- 格式:DOCX

- 页数:9

- 大小:178.37KB

针对IO的缓冲器版图设计.docx

《针对IO的缓冲器版图设计.docx》由会员分享,可在线阅读,更多相关《针对IO的缓冲器版图设计.docx(9页珍藏版)》请在冰豆网上搜索。

针对IO的缓冲器版图设计

《集成电路版图设计》实验

(二):

针对IO的缓冲器版图设计

一.实验容

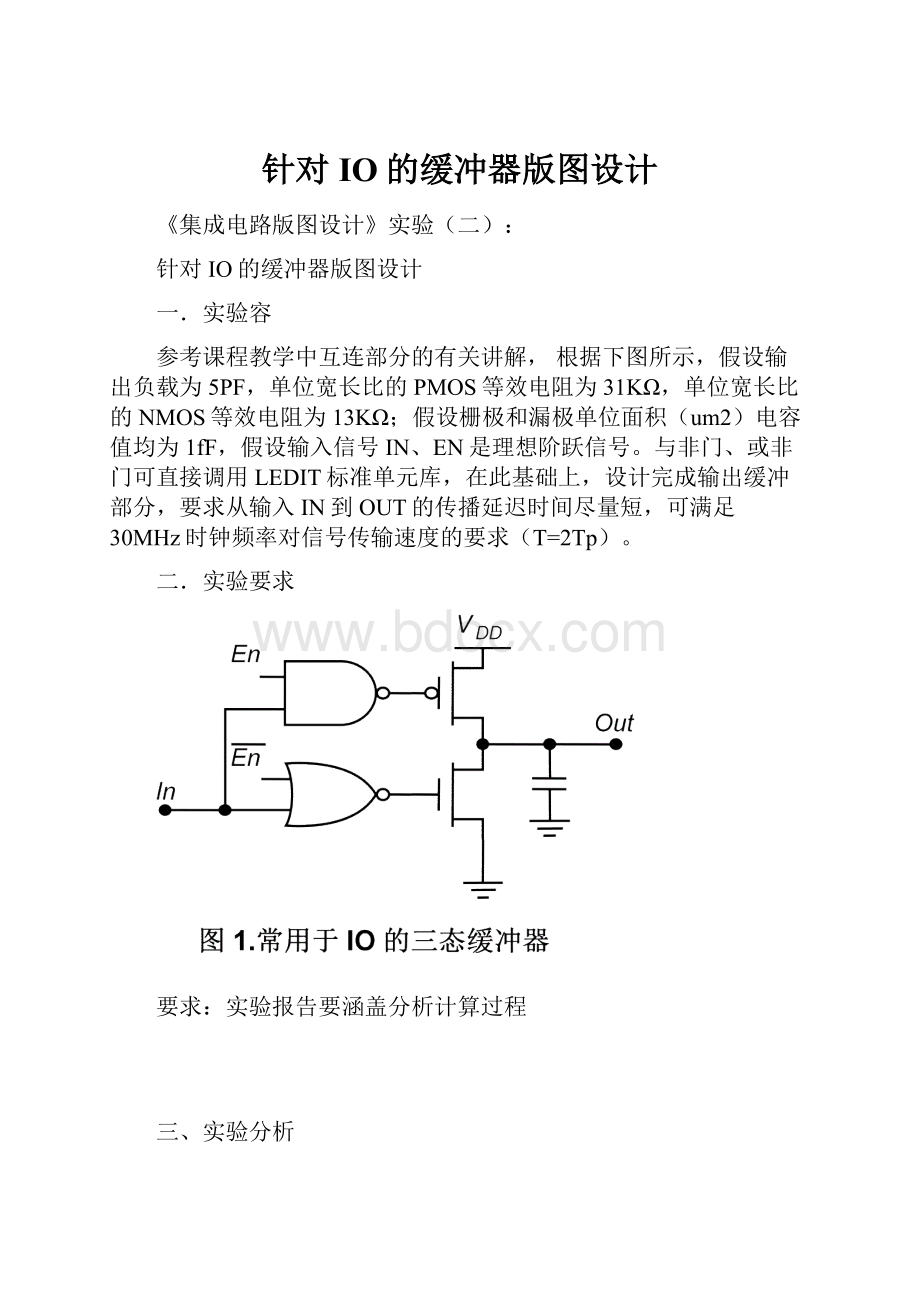

参考课程教学中互连部分的有关讲解,根据下图所示,假设输出负载为5PF,单位宽长比的PMOS等效电阻为31KΩ,单位宽长比的NMOS等效电阻为13KΩ;假设栅极和漏极单位面积(um2)电容值均为1fF,假设输入信号IN、EN是理想阶跃信号。

与非门、或非门可直接调用LEDIT标准单元库,在此基础上,设计完成输出缓冲部分,要求从输入IN到OUT的传播延迟时间尽量短,可满足30MHz时钟频率对信号传输速度的要求(T=2Tp)。

二.实验要求

要求:

实验报告要涵盖分析计算过程

三、实验分析

为了满足时钟频率对信号传输速度的要求,通过计算与非门和或非门的最坏延时,再用全局的时钟周期减去最坏的延时,就得到了反相器的应该满足的延时要求,可以得到反相器N管和P管宽度应该满足什么要求。

标准与非门和或非门的电容、电阻可以通过已知条件算出。

由于与非门、或非门可直接调用LEDIT标准单元库,所以本设计的关键在于后级反相器的设计上(通过调整反相器版图的宽长比等),以满足题目对电路延时的要求。

由于输入信号IN和是理想的阶跃信号,所以输入的延时影响不用考虑。

所以计算的重点在与非门和或非门的延时,以及输出级的延时。

对于与非门,或非门的延时,由于调用的是标准单元,所以它的延时通过提取标准单元的尺寸进行估算,输出级的尺寸则根据延时的要求进行设计。

四、分析计算

计算过程:

(1)全局延时要求为:

30MHz的信号的周期为T=1/f=33ns;

全局延时对Tp的取值要求,Tp<1/2*T=16.7ns;

(2)标准单元延时的计算:

所用到的标准单元如下图所示:

图2.与非门和或非门标准单元版图

通过在ledit软件中使用尺子测量与非门和或非门的晶体管的尺寸,得到了L=2um,W=28um,漏极的长度为LD=6um。

pmos和nmos采用的是等尺寸的。

NMOS的电阻为:

Rn=13kΩ/(w/l)n=13kΩ/14=0.93kΩ

PMOS的电阻为:

Rp=31kΩ/(w/l)p=31kΩ/14=2.2kΩ

栅极的寄生电容为Cg=2281fF=56fF

漏极的寄生电容为Cd=6281fF=168fF

分别计算与非门和或非门的上拉和下拉网络的延迟时间,以找到最坏路径的延时,将最坏延时确定这一级的延时。

CL为后级pmos的栅极电容,由于栅极电容的量级一般在fF量级,从上面的结果知道,栅电容为56fF,对其延时影响有限,所以我们忽略栅电容的影响,只计算无负载延时。

(3)计算与非门的无负载延时

图三.与非门管级电路图

1、与非门下拉网络的无负载延时,即C1通过一个MOS管放电加上C2通过两个MOS管的放电时间:

TPHL=0.69*(0.93kΩ*168fF(0.93kΩ0.93kΩ)*168fF)=0.32ns

2、与非门上拉网络的最坏延迟时间即单管导通的延时:

TPLH=0.682.3kΩ168fF=0.256ns;

所以比较可知与非门的最坏延时为下拉时间TPHL=0.32ns;

(4)或非门的无负载延时

图4.或非门的管级电路图

1、或非门下拉网络的最大延迟即单管导通延迟:

TPHL=0.69*0.93kΩ*168fF=0.108ns;

2、或非门上拉网络的最大延迟:

TPLH=0.69*(2.3kΩ168fF(2.3kΩ2.3kΩ)168fF)=0.765ns;

所以比较可知或非门的最大延时TPLH=0.765ns。

可见:

与非门和或非门的最坏延时由或非门的上拉网络决定,其无负载的延时为0.765ns。

实际中或非门的下级负载是反相器NMOS的栅极电容,从上面的结果知道,栅电容为56fF,可知栅极电容是比较小的,取一个适当的栅电容值100fF。

(5)输出级的延时应该满足的数值

当负载电容为100fF时的延时为:

TP栅=0.69*(2*RP*Cg)=0.69*2*2.2*10^3*100*10^(-15)=0.304ns

得到反相器前的最坏延迟为:

tp=TPLH+TP栅=0.765ns+0.304ns=1.093ns

所以输出级的延时应该小于16.7ns-1.093ns=15.607ns。

(6)反相器尺寸的确定

由于漏极电容的量级在fF量级,所以,输出的电容负载近似的认为仅有CL=5pf提供。

1、设PMOS的栅宽为Wp,栅长由工艺决定2um,所以上拉网络延时应该满足的关系为:

0.69*31kΩ/(WP/2)*5*10^(-12)F<15.607ns

得到:

WP>13.705um。

2、设NMOS的栅宽为Wn,栅长由工艺决定2um,所以上拉网络延时应该满足的关系为:

0.69*13kΩ/(Wn/2)*5*10^(-12)F<15.607ns

得到:

WP>5.747um。

五、版图绘制的过程概述

(1)计算后分析

我们通过计算得到了输出端NMOS和PMOS的最小尺寸,分别为5.747um和13.705um,其对应的栅电容比标准与非门和或非门小很多,前面计算得知标准与非门的栅电容仅仅为栅电容为56fF,可知栅极电容是比较小的,因此我们在前面取的或非门的后级负载电容量100fF是满足设计要求的。

通过上面计算可以知道,NMOS的尺寸只要大于5.747um,PMOS的尺寸只要大于13.705um就可以满足时钟频率对信号传输速度的要求。

由于布线,设计规则的限制,导致版图面积会变大,所以N管有源区的面积可以绘制大一些也并不会增大整体版图面积。

综合选定了反相器PMOS的的宽度为14um,反相器NMOS的尺寸为12um。

(2)绘制版图的过程

1、打开ledit软件,新建newlayout,通过file中的replacesetup选择lights.tdb文件,使用里面的参数设置来绘制版图。

2、调用标准与非门和或非门,将两个门放置在同一高度。

3、下面绘制反相器版图,根据前述的计算,在P衬底上绘制有源区,再画Nselect,将有源区包裹住,进行设计规则检查。

4、在有源区上绘制1条多晶硅,宽度为最小尺寸,。

需满足最小尺寸要求和伸展出有源区2um的距离。

进行设计规则检查无误后,这样就形成了MOS管的源漏。

4、绘制GND,反相器NMOS的源极通过metal1接地。

需要满足金属包裹接触孔、接触孔离有源区的边界、接触孔离多晶的距离,金属的最小尺寸等设计规则。

5、上述步骤将反相器的NMOS基本绘制完成。

下面绘制PMOS,根据前面计算的尺寸,首先绘制Nwell,再在Nwell中绘制Pselect,然后再绘制Active层,之后绘制多晶硅,伸展出有源区2um的距离这样就形成了PMOS的源漏区,进行设计规则检查。

6、绘制VDD。

根据电路图知反向器PMOS的源极需要接电源,在有源区打接触孔,通过金属线连接至电源端。

需要满足金属包裹接触孔、接触孔离有源区的边界、接触孔离多晶的距离,金属的最小尺寸等设计规则。

7、上面的步骤基本完成了MOS管的绘制,之后就是连接和信号输入输出问题了。

根据电路图,将与非门和或非门的一个输入连接,引入IN信号,与非门的另一个输入引入En信号,或非门的另一个输入引入En的反向信号。

8、将或非门的输出通过Metal1→通孔→Metal2→通孔→Metal1→多晶硅接触→NMOS的栅极,最后进行设计规则检查。

9、将与非门的输出通过Metal1→通孔→Metal2→通孔→Metal1→多晶硅接触→PMOS的栅极,最后进行设计规则检查。

10、做NMOS和PMOS的衬底接触,进行设计规则检查。

11、将反相器的NMOS和PMOS的漏极通过Metal1连接,在Metal1上打通孔连接Metal2将最终的输出引出,进行设计规则检查。

综合布局布线,设计版图、输入输出如下图5所示。

通过DRC检测没有错误。

图5.IO的缓冲器版图

(3)版图评价

1、将与非门、或非门、反相器的PMOS都绘制在了一个Nwell中,避免了不同Nwell之间间距的设计规则要求,节省了版图的面积。

2、版图的绘制都是一步一步按照设计规则卡出来的,使得有源区面积小,使用了最小尺寸的多晶硅和金属连线,减小寄生参数,降低RC延时。

3、在版图面积已经确定的情况下,尽可能的加大了有源区的面积,改善了电路性能。

4、在最小面积的有源区上,尽可能多的做了接触孔,减小接触电阻。

5、通过使用Metal2,减小了布线间距,节省了面积。

6、将nMOS管和pMOS管的多晶硅栅极对准,利于工艺上的加工,这样可以由最小长度的多晶硅线条组成栅极连线,这样做可以降低RC延时。

六、总结

这次版图设计我做的针对IO的缓冲器版图设计,明白了几成定阿鲁怎么对延时进行计算和分析,对所学的CMOS集成电路设计有一个更系统更全面的了解,通过两次L-edit软件的训练,进一步加深了L-edit软件的基本操作方法,进一步熟悉了版图的绘制步骤,并能够独立的运用该软件设计版图,灵活的根据要求绘制版图,我想这对我今后学习或者工作大有裨益,今后,我要更多的运用该软件,达到熟练掌握的目的,在我们锻炼动手能力的同时,学到更多的有关专业知识。

感师兄师姐上机时的悉心指导,使我能够进一步完善所绘制的版图,学习到更多知识。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 针对 IO 缓冲器 版图 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《崔万志演讲观后感》.docx

《崔万志演讲观后感》.docx