QuartusII教程.docx

QuartusII教程.docx

- 文档编号:26821199

- 上传时间:2023-06-23

- 格式:DOCX

- 页数:61

- 大小:2.77MB

QuartusII教程.docx

《QuartusII教程.docx》由会员分享,可在线阅读,更多相关《QuartusII教程.docx(61页珍藏版)》请在冰豆网上搜索。

QuartusII教程

第3章AlteraQuartusII软件开发向导

基于AlteraQuartusII软件的设计方法有模块编辑法、文本编辑法、宏模块编辑法和包含前三种方法的混合编辑法。

宏模块设计法放在第6章讲述,本章通过实例简单介绍使用QuartusII软件的模块原理图编辑法、文本编辑法和包含前两种方法的混合编辑法。

3.1模块编辑及设计流程

QuartusII软件的模块编辑器以原理图的形式和图标模块的形式来编辑输入文件。

每个模块文件包含设计中代表逻辑的框图和符号。

模块编辑器可以将框图、原理图或符号集中起来,用信号线、总线或管道连接起来形成设计,并在此基础上生成模块符号文件(.bdf)、AHDLInclude文件(.inc)和HDL文件。

3.1.1原理图输入文件的建立

在这里我们设计非常简单一个二输入的或门电路。

它只包含一个或门、两个输入引脚和一个输出引脚。

首先创建一个原理图形式的输入文件。

步骤如下:

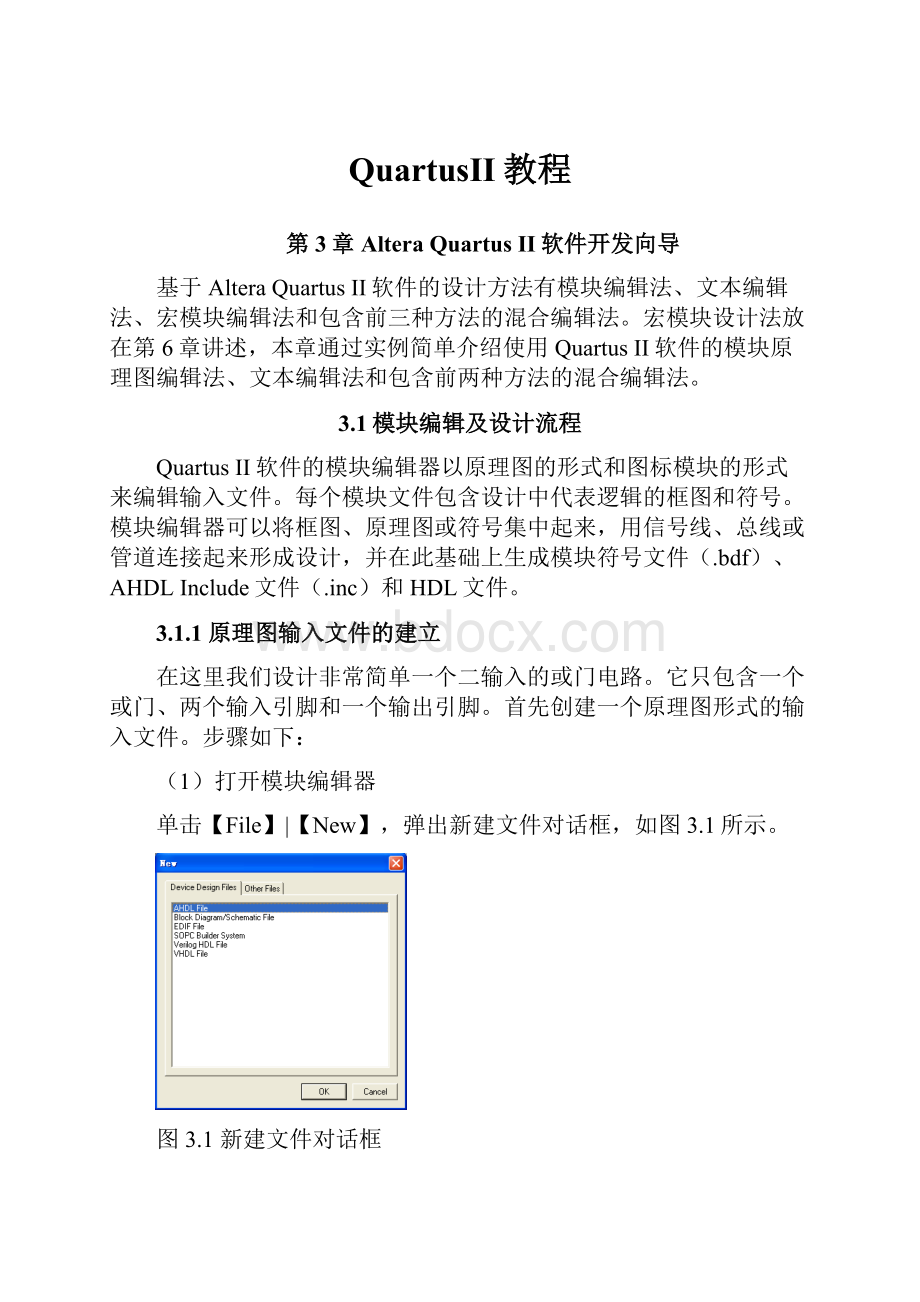

(1)打开模块编辑器

单击【File】|【New】,弹出新建文件对话框,如图3.1所示。

图3.1新建文件对话框

选择文件类型【BlockDiagram/SchematicFile】,打开模块编辑器,如图3.2所示。

使用该编辑器可以编辑图标模块,也可以编辑原理图。

图3.2模块编辑器

QuartusII提供了大量的常用的基本单元和宏功能模块,在模块编辑器中可以直接调用它们。

在模块编辑器要插入元件的地方单击鼠标左键,会出现小黑点,称为插入点。

然后鼠标左键,弹出【Symbol】对话框,如图3.3所示。

或者在工具栏中单击

图标,也可打开该对话框。

图3.3Symbol对话框

在Symbol对话框左边的元件库【Libraries】中包含了QuartusII提供的元件。

它们存放在\altera\quartus60\libraries\的子目录下,分为primitives、others、megafunctions三个大类。

❑基本逻辑函数(primitives)

基本逻辑函数存放在\altera\quartus60\libraries\primitives\的子目录下,分别为缓冲逻辑单元(buffer)、基本逻辑单元(logic)、其它单元(other)、引脚单元(pin)和存储单元(storage)五个子类。

Buffer子类中包含的是缓冲逻辑器件,如alt_inbuffer、alt_out_buffer、wire等;logic子类中包含的是基本逻辑器件,如and、or、xor等门电路器件;other子类中包含的是常量单元,如constant、vcc和gnd等;pin子类中包含的是输入、输出和双向引脚单元;storage子类中包含的是各类触发器,如dff、tff等。

❑宏模块函数(megafunctions)

宏模块函数是参数化函数,包括LPM函数MegaCoreAMPP函数。

这些函数经过严格的测试和优化,用户可以根据要求设定其功能参数以适应不同的应用场合。

这些函数存放在\altera\quartus60\libraries\megafunctions\的子目录下,包含arithmetic、gates、I/O和storage四个子类。

arithmetic子类中包含的是算法函数,如累加器、加法器、乘法器和LPM算术函数等;gates子类中包含的是多路复用器和门函数;I/O子类中包含的是时钟数据恢复(CDR)、锁相环(PLL)、千兆位收发器(GXB)、LVDS接收发送器等;storage子类中包含的是存储器、移位寄存器模块和LPM存储器函数。

❑其他函数(others)

其他函数包含了MAX+Plus所有的常用的逻辑电路和Opencore_plus函数,这些函数存放在\altera\quartus60\libraries\others\的子目录下。

这些逻辑函数可以直接应用到原理图的设计上,可以简化许多设计工作。

在模块编辑器的左边是工具栏,熟悉这些工具按钮的性能,可以大幅度提高设计速度。

下面详细介绍这些按钮的功能。

❑选择工具

:

选取、移动、复制对象,是最基本且常用的功能。

❑文字工具

:

文字编辑工具,设定名称或批注时使用。

❑符号工具

:

用于添加工程中所需要的各种原理图函数和符号。

❑图标模块工具

:

用于添加一个图表模块,用户可定义输入和输出以及一些相关参数,用于自顶向下的设计。

❑正交节点工具

:

用于画垂直和水平的连线,同时可定义节点的名称。

❑正交总线工具

:

用于画垂直和水平的总线。

❑正交管道工具

:

用于模块之间的连线和映射。

❑橡皮筋工具

:

使用此项移动图形元件时引脚与连线不断开。

❑部分连线工具

:

使用此项可以实现局部连线。

❑放大/缩小工具

:

用于放大或缩小原理图。

❑全屏工具

:

用于全屏显示原理图编辑窗口。

❑查找工具

:

用于查找节点,总线和元件等。

❑元件翻转工具

:

用于图形的翻转,分别为水平翻转,垂直翻转和90度的逆时针翻转。

❑画图工具

、

、

、

:

画图工具,分别为矩形、圆形、直线和弧线工具。

(2)添加元件符号

打开Symbol对话框左边的元件库【Libraries】,选择【primitives】|【logic】|【or2】,弹出Symbol对话框,如图3.4所示。

图3.4在Symbol对话框选择元件

单击【OK】按钮。

鼠标变为+和选中的符号,将目标元件移动到合适位置单击左键,编辑器窗口就出现了该元件,如图3.5所示。

图3.5在编辑器窗口添加或门

同理,在【Libraries】中,选择【primitives】|【pin】|【input】,放两个输入引脚到编辑器窗口;选择【primitives】|【pin】|【output】,放一个输出引脚到编辑器窗口。

如图3.6所示。

图3.6在编辑器窗口添加输入/输出引脚

(3)连接各元件并给引脚命名

放置好元件后,接下来的就要连接各个功能模块,通过导线将模块间的对应管脚直接连接起来。

其具体做法如下:

将鼠标移到其中一个端口,待鼠标变为“+”形状后。

一直按住鼠标左键,将鼠标拖到到待连接的另一个端口上。

放开左键,则一条连线画好了。

如果需要删除一根线,单击这根连线并按Del键。

这里分别将两个输入引脚连接到或门的两个输入端,将输出引脚连接到或门的输出端。

连线完成后可以给输入/输出引脚命名。

在引线端子的PIN_NAME处双击鼠标,弹出PinProperties对话框,在【Pinname】栏中填入名字。

这里三个引脚分别命名为A、B、C。

如图3.7所示。

图3.7连接元件并命名

引脚名称可以使用26个大写英文字母和26个小写英文字母,以及10个阿拉伯数字,或是一些特殊符号“/”“_”来命名,例如AB,/5C,a_b都是合法的引脚名。

引脚名称不能超过32个字符;大小写的表示相同的含义;不能以阿拉伯数字开头;在同一个设计文件中引脚名称不能重名。

总线(Bus)在图形编辑窗口中显示为的是一条粗线,一条总线可代表2~256个节点的组合,即可以同时传递多路信号。

总线的命名必须在名称后面加上[a…b],表示一条总线内所含的节点编号,其中a和b必须是整数,但谁大谁小并无原则性的规定,例如A[3..0]、B[0..15]、C[8..15]都是合法的总线名称。

(4)保存文件

最后如需要保存文件,选择【File】菜单中的【SaveAs】项或单击

按钮,弹出SaveAs对话框,如下图3.8所示,在FileName对话框内输入设计文件名my_or_2,然后选择【OK】,即可保存文件。

图3.8保存文件

原理图和图表模块设计的文件名称与引脚命名规则相同,长度必须在32个字符以内,不包含扩展名“.bdf”。

3.1.2图表模块输入

图表模块输入是自顶向下的设计方法。

首先在顶层文件中划出图形块或器件符号,然后在图形块上设置端口和参数信息,用信号线、总线和管道把各个组件连接起来。

下面以3-8译码器为例介绍图表模块输入法。

打开模块编辑器,单击工具栏上的图表模块工具

,将该模块拖到右边的空白处,用鼠标在需作图的地方画矩形框,在所画的矩形框范围就会出现图表模块,如图3.9所示。

图3.9生成的图表模块

在图表模块上单击鼠标右键,弹出如图3.10左图所示的菜单,选择【BlockProperties】选项,弹出模块属性设置对话框,如图3.10右图所示。

图3.10模块属性设置对话框

模块属性设置对话框有四个属性标签页.。

在【General】标签页中的【Name】栏设置模块名称为decode3_8;在【I/Os】标签页设置3-8译码器的端口信息,在【Name】栏中输入端口名称A,【Type】栏输入INPUT,设定为输入端口。

单击【Add】按钮,即可将输入端口A添加到模块属性设置对话框下面的【ExistingBlockI/Os】列表中,如图3.11左图所示。

以此类推,添加另外两个输入信号B、C,添加三个使能信号G1、G2a、G2b,添加八个输出信号y0、y1、y2、y3、y4、y5、y6、y7。

如图3.11右图所示。

图3.11添加输入端口

单击【确定】,就生成了图标模块。

使用鼠标选中图标模块,调整其大小,以便显示所有的端口。

如图3.12所示。

图3.12生成的图标模块

单击

,保存设计的图标模块文件,将该文件的后缀名定义为.bdf。

以上的设计过程只是规定了设计的图标模块的外部端口,图标模块的功能由硬件描述语言或图形文件实现。

QuartusII软件支持的设计文件格式有:

AHDL语言格式、VHDL语言格式、VerilogHDL语言格式、Schematic图形格式。

在图标模块单击鼠标右键,在弹出的菜单中选择【CreateDesignFilefromSelectedBlock】选项,弹出创建设计文件对话框,如图3.13所示。

图创建设计文件对话框

选择文件设计类型,这里选VHDL,确定是否把将要生成的文件添加到当前工程中。

单击【OK】,就生成了设计文件decode3_8.vhd。

如图所示。

图3.13生成设计文件decode3_8.vhd

单击【确定】,弹出包含端口声明的VHDL文本编辑窗口,如图3.14所示。

图包含端口声明的VHDL文本编辑窗口

在该窗口中,已经自动生成了包含端口定义的VHDL程序的实体部分,用描述模块功能的结构体部分是个空白,需要插入相应的语句,完成设计。

如果在图创建设计文件对话框选择Schematic,则弹出包含已经定义的输入输出端口原理图编辑窗口,如图3.15所示。

图3.15已经定义的输入输出端口原理图编辑窗口

在原理图编辑窗口左边,是输入端口;在原理图编辑窗口右边,是输出端口。

下面我们要做的工作就是在中间插入元件,以构成自动decode3_8的原理图。

在生成图标模块的设计文件之后,如果需要对顶层图标模块的端口名或端口数目进行修改,那么在修改后,在模块上单击右键,在弹出的菜单中选择【UpdateDesignFilefromSelectedBlock】选项,QuartusII软件会自动更新底层设计文件。

在设计较为复杂的电路时,顶层文件中需要包含多个图标模块和多个元件符号,而且需要把它们连接起来。

,一般来说,连接元件符号的是信号线或总线,连接图标模块的既可以是信号线或总线,也可以是管道。

当用管道连接两个图标模块时,如果两边端口名称相同,如图所示则不必在管道上加标注,两者能够智能连接。

在连接两个图标模块的管道上单击右键,在弹出的菜单中选择【Properties】选项,弹出ConductProperties对话框,如图3.16所示。

选择【Signal】属性页,可在【Connections】列表中看到对应的连接关系。

如图3.17所示。

图3.16具有相同端口名称的两图标模块

图3.17ConduitProperties对话框

当需要连接的两个图标模块端口名称不同时,或者是图标模块和元件符号相连时,使用端口映射的方法将两个模块的端口连接起来。

以如图3.18所示的电路为例。

图3.18图标模块和元件符号相连

图3.18中显示的时一个图标模块和一个二输入的与门,首先用两条信号线分别从与门的两个输入端引向图标模块,在图标模块会产生一个连接器端点。

选中连接的信号线,在弹出的菜单中选择【Properties】选项,弹出ConductProperties对话框,对该信号线命名,例如这里为wire01和wire02。

选中图标模块中需要映射的连接器端点,在连接器端点上单击右键,在弹出的菜单中选择【MapperProperties】选项,弹出MapperProperties对话框,如图3.19所示。

图3.19MapperProperties对话框

在MapperProperties对话框中选择【Mapping】属性页,该属性页用于设置模块I/O端口和连接器上的信号映射。

例如,这里在【I/Oonblock】填入M,在【Signalinnode】填入单击wire01,单击【Add】按钮,就将映射关系添加到了下面的【Existingmapping】列表中,表示将图标模块的输出端连接到信号线wire01上,而信号线wire01又连接在与门的一个输入端上,这样就实现了图标模块和元件符号的相连。

依此类推,将其它映射关系也添加进来。

完成映射后,在图表模块连接器端点处可以看到相关信息,如图3.20所示。

图3.20映射后的连接图

如果连接的是两个图标模块,用类似同样地办法设置。

3.1.3原理图设计流程

本节以上节建立的二输入或门输入文件为顶层文件,通过全部流程,实现设计。

详细介绍基于QuartusII软件的原理图设计方法,具体实现步骤如下。

1.建立工程

(1)单击【File】|【NewProjectWizard】选项,弹出工程向导的基本信息对话框,如图3.7所示,在此对话框中,第一栏填入新工程的文件夹名,这里单击

,弹出SelectDirectory对话框,找到上节建立的输入文件(my_or2.bdf),单击【打开】,在第一栏就出现新工程的文件夹名,第二栏出现工程名,第三栏出现顶层实体名。

注意工程名要和顶层实体名相同。

图3.7工程向导的基本信息

(2)选择需要加入的文件和库

单击图3.7所示对话框中的【Next】按钮进行下一步操作。

此时如果文件夹不存在的话,系统会自动提示用户是否创建该文件夹,选择【Yes】按钮后会自动创建。

已经创建就弹出添加文件对话框,如图3.8所示。

如果此设计中还需要其他设计文件,可以单击【Filename】栏右边的

,选择要添加的文件,单击【AddAll】按钮就将该文件加入到上面的工程中。

或者直接单击【AddAll】按钮加入在该目录下的所有文件,如果需要用户自定义的库,单击【UserLibraries】按钮进行选择。

选中已加入的文件,单击【Remove】可以将其移除。

这里不需要添加任何其它文件,直接单击【Next】。

图3.8添加文件对话框

3)选择目标器件

单击图3.8所示对话框中的【Next】按钮后,弹出器件类型设置的对话框,如图3.9所示。

在【Targetdevice】选项中选择【AutodeviceselectedbytheFitter】选项,系统会自动给所设计的文件分配目标器件。

选择【Specificdeviceselectedin‘Availabledevices’list】选项,用户可以根据实验条件指定目标器件。

在右侧的选项中,可以选择目标器件的封装类型(Package),引脚数量(Pincount)和速度等级(Speedgrade)以便快速查找用户所需的器件范围。

图3.9器件类型设置

(4)选择第三方EDA工具

单击图3.9中的【Next】按钮,弹出EDA工具设置对话框,如图.10所示。

在此选择使用的第三方EDA工具。

本例中不需要第三方EDA工具,直接单击【Next】按钮。

图3.10EDA工具设置

(5)结束工程设置

最后弹出新工程确认对话框,如图3.11所示。

从对话框中可以看到建立的工程名称,选择的器件等信息,如确认无误后,单击【Finish】按钮,创建新工程。

图3.11工程信息概要

2.编译工程

单击工具栏上的

按钮,对工程文件进行编译,这时QuartusII界面不断变化,编译结束后产生的界面如图3.12所示,这是编译成功的情况。

单击【确定】,生成的编译结果界面如图3.13所示。

该界面显示了编译时的各种信息。

如果编译不成功,在信息显示窗口给出错误和警告,可根据提示错误和警告进行相应的修改后重新编译,直到没有错误提示为止。

图3.12编译完成时界面

图3.13编译结果

3.建立仿真矢量波形文件

(1)创建文件

在工具栏中单击【File】|【New】,弹出新建对话框,如图3.14所示。

在出现的【New】对话框中选择【OtherFiles】页面,在该页面选择【WaveformEditorFile】选项,单击【OK】按钮,弹出矢量波形文件编辑窗口,如图3.15所示。

图3.14建立矢量波形文件

图3.15矢量波形编辑窗口

(2)添加引脚或节点

双击图3.15中【Name】下方空白处,弹出InsertNodeorBus对话框,如图3.16所示。

图3.16InsertNodeorBus对话框

点击【NodeFinder】按钮,弹出NodeFinder对话框,如图3.17所示。

图3.17NodeFinder对话框

单击【Filter】栏的下拉菜单选择【Pins:

all】选项后,点击【List】按钮,弹出设计文件引脚列表窗口,如图3.18所示。

在【NodeFound】栏中列出了设计文件的列表。

图3.18输入/输出引脚列表

在列表中双击需要的引脚,选中的信号将出现在右边的一侧,或者单击

按钮,也可以如此,如图3.19所示。

图3.19选择输入/输出节点

单击【OK】按钮。

返回insertNodeorBus对话框,如图3.20所示。

图3.20查找节点后的“InsertNodeorBus”对话框

单击【OK】按钮后,选中的输入/输出引脚就出现在波形编辑窗口的【Name】栏下,引脚添加成功,如图3.21所示。

图3.21添加节点后的矢量波形编辑窗口

(3)编辑输入波形并保存

波形观察窗的左边是输入引脚,在同行的右边可以编辑波形。

使用时,先选中左边的输入引脚名,再在右边用鼠标在输入波形上拖一条需要改变的黑色区域,然后单击左边工具栏的有关按钮,即可进行低电平、高电平、任意、高阻态、反相和总线数据等各种设置。

若是时钟信号,用鼠标点时钟信号的

,出现时钟信号设置对话框,按下【OK】即可设置时钟信号。

这时时钟信号的波形区域全部变成黑色,按集成环境窗左边上的时钟按钮,根据要求将各输入信号A、B的波形设置成如图3.22所示。

然后单击

保存文件,文件取名为my_or_2.vwf。

图3.22编辑输入信号

4.波形仿真

(1)功能仿真

在QuartusII的工具栏中选择【Processing】|【GenerateFunctional….】,生成功能仿真网表,然后选择【Assignments】|【Setting】,弹出设置仿真类型对话框,点击“SimulatorSettings”选项,在“simulationmode”中选择“Functional”命令,如图3.23所示。

图3.23设置功能仿真类型

后点击

按钮进行功能仿真,检查设计的逻辑错误。

仿真结果如图3.24所示。

图3.24功能仿真

(2)时序仿真

选择QuartusII的工具栏中【Assignments】|【Setting】|【SimulatorSettings】|【simulationmode】选择“Timing”命令,然后单击工具栏的

按钮,开始时序仿真,验证时序是否符合要求,仿真过程在后台进行,计算机能够同时作其他的工作。

结果如图3.25所示。

图3.25时序仿真

观察波形,发现输出端C的波形产生了一些延时。

5.引脚分配

分配引脚是为了对所设计的过程进行硬件测试,将输入/输出引脚信号锁定在目标器件的引脚上。

单击工具栏【Assignments】|【Pins】选项,弹出选择要分配的分配引脚的对话框,如图3.26所示。

在下方的列表中列出了本设计的所有输入\输出引脚名。

图3.26选择要分配的分配引脚

在图3.26中,双击输入端A对应的【Location】选项,弹出引脚列表,从中选择合适的引脚,这时输入A的引脚分配完毕,同理完成其他所有引脚的指定,结果如图3.27所示。

图3.27完成所有引脚的分配

6.下载验证

下载验证是将所做设计生成的文件通过计算机下载到实验电路板上,用来验证本次设计是否符合要求的一道流程,其步骤如下:

(1)编译

分配完引脚后必须经过再次编译,这样才能存储引脚锁定的信息,单击编译按钮

执行再次编译。

如果编译出现问题,可以对器件重新设置。

(2)配置下载电缆

在【Tools】|【Progammer】命令,弹出未经配置的下载窗口,如图3.28所示。

图3.28未经配置的下载窗口

单击【HardwareSetup】按钮,弹出HardwareSetup对话框,如图3.29所示。

图3.29HardwareSetup对话框

单击【AddHardware】按钮,弹出下载电缆选择对话框,如图3.30所示。

在【HardwareType】一栏中选择【ByteBlasterMVorByteBlasterII】,单击【OK】按钮,完成设置。

如果下载电缆一直保持不变,不需每次都要设置。

图3.30下载电缆选择对话框

(3)JTAG模式下载

JTAG模式是QuartusII软件默认的下载模式,其相应的下载文件为.sof格式,勾选下载文件右侧的小方框,如图3.31所示.。

图3.31选择下载文件

将下载电缆连接好后,单击【Start】按钮,计算机就开始下载编程文件。

下载完后结果如图3.32所示。

图3.32JTAG模式下载完毕

(4)ActiveSerial模式

ActiveSerial模式的下载文件为“.pof”格式,在【Mode】一栏中选择ActiveSerial】,弹出提示框,点击【是】,然后在“AddFile”里添加选择文件“or_2.pof”,勾选下载文件右侧的小方框,将下载电缆连接好后,单击【Start】按钮,开始下载编程文件。

下载完后结果如图3.33所示。

图3.33ActiveSerial模式

对于大多数设计来说,到此就完成了。

7.QuartusII的几个常用功能。

(1)使用RTLViewer分析综合结果

单击【Tools】|【NetlistViewers】|【RTLViewer】,弹出RTLViewer对话框,如图3.34所示。

可以看到综合后的RTL结构图,发现该图与原理图相同。

图3.34RTLViewer对话框

(2)使用TechnologyMapViewer分析综合结果

单击【Tools】|【NetlistViewers】|【TechnologyMapViewer】,弹出TechnologyMapViewer对

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- QuartusII 教程

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《C12343098汽轮机操作规程》要点.docx

《C12343098汽轮机操作规程》要点.docx