EDA技术实验教案.docx

EDA技术实验教案.docx

- 文档编号:26545163

- 上传时间:2023-06-20

- 格式:DOCX

- 页数:26

- 大小:190.03KB

EDA技术实验教案.docx

《EDA技术实验教案.docx》由会员分享,可在线阅读,更多相关《EDA技术实验教案.docx(26页珍藏版)》请在冰豆网上搜索。

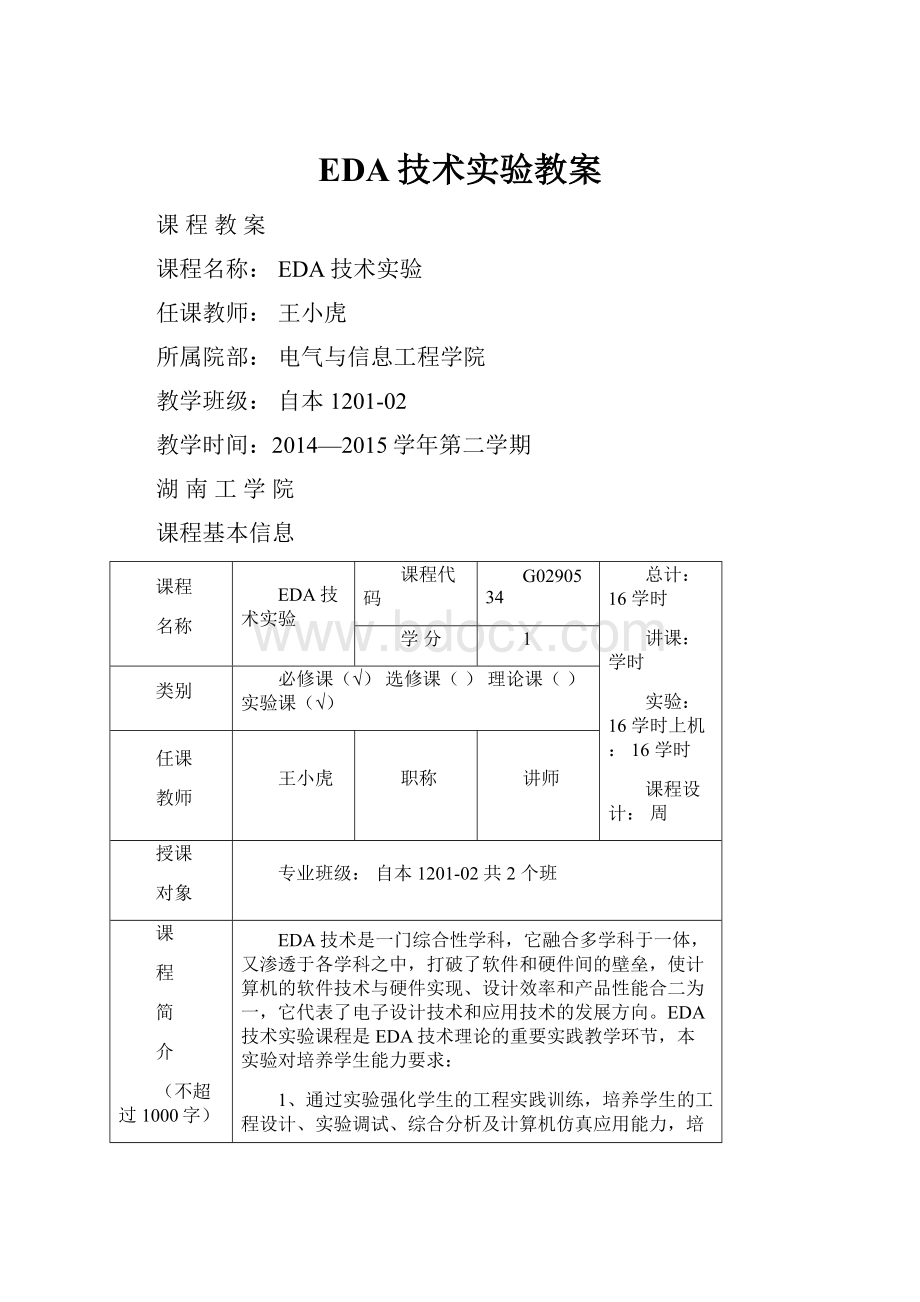

EDA技术实验教案

课程教案

课程名称:

EDA技术实验

任课教师:

王小虎

所属院部:

电气与信息工程学院

教学班级:

自本1201-02

教学时间:

2014—2015学年第二学期

湖南工学院

课程基本信息

课程

名称

EDA技术实验

课程代码

G0290534

总计:

16学时

讲课:

学时

实验:

16学时上机:

16学时

课程设计:

周

学分

1

类别

必修课(√)选修课()理论课()实验课(√)

任课

教师

王小虎

职称

讲师

授课

对象

专业班级:

自本1201-02共2个班

课

程

简

介

(不超过1000字)

EDA技术是一门综合性学科,它融合多学科于一体,又渗透于各学科之中,打破了软件和硬件间的壁垒,使计算机的软件技术与硬件实现、设计效率和产品性能合二为一,它代表了电子设计技术和应用技术的发展方向。

EDA技术实验课程是EDA技术理论的重要实践教学环节,本实验对培养学生能力要求:

1、通过实验强化学生的工程实践训练,培养学生的工程设计、实验调试、综合分析及计算机仿真应用能力,培养学生严谨的科学作风,为今后能设计更大规模的电路系统打好基础。

2、根据教学计划,本学期EDA技术实验课程共开设8个实验项目,每个实验项目2学时,共计16学时。

具体安排依次为:

原理图的绘制,PCB板的制作,有时钟使能的二位十进制计数器原理图输入设计,7段数码显示译码器设计,数控分频器的设计,循环彩灯控制器的设计,四位十进制数字频率计的设计,频率计的综合设计共八个实验。

3、通过本课程实验教学使学生能掌握自顶向下的设计方法,将系统分解为各个模块,使用VHDL语言对硬件设计进行说明、建模、逻辑及结构综合、行为及功能仿真、硬件测试等最终完成设计。

4、学生在完成每个实验项目后,要求认真撰写实验报告(实验名称、目的要求、设计步骤、实验电路、实验结果及实验结果分析、总结与讨论),并鼓励学生在报告中发表自己的独到见解和所做的实验创新。

基本

教材

和主

要参

考资

料

教材:

理论教材:

潘松黄继业编著.EDA技术实用教程.科学出版社,第三版.

实验教材:

自编EDA技术实验指导书

参考书

[1]王振红主编.VHDL数字电路设计与应用实践教程.机械工业出版社,2003.

[2]谭会生主编.EDA技术基础。

湖南大学出版社,2004。

[3]李国丽朱维勇等编著.EDA与数字系统设计.机械工业出版社,2004.

实验一原理图的绘制

一、本次课主要内容

绘制一张完整的电源电路原理图.

1.绘制电源电路的原理图,并填上正确的封装,完成后将文件存盘。

2.对完成的电路图进行ERC校验,若有错误,则加以改正,直到校验无误后,存盘.

2.对修改后的电路图进行编译,产生网络表文件,将网络表文件存盘后退出

3.根据以上的实验内容写出实验报告,并将绘制好的完整电源电路图打印出来贴在报告中,分析实验过程中遇到的问题,总结用到的知识点。

二、教学目的与要求

1.熟练掌握PROTEL99的基本操作。

2.学会绘制电路原理图。

3.掌握电路图的ERC校验、电路错误修改和网络表的生成

三、教学重点难点

重点:

调用元件;创建原理图元件库;网络标号。

难点:

原理图元件库的创建

四、教学方法和手段

采用课堂讲授大概20分钟时间,对原理图绘制的方法与技巧运用多媒体进行演示、制作教学幻灯片。

五、作业与习题布置

写出完整的实验报告,并回答下面问题。

1、为什么要给元器件定义封装形式?

是否所有原理图中的元器件都要定义封装形式?

2、放置元器件时系统提示没有打开元器件库,应如何解决?

3、使用网络标号时应注意哪些问题?

4、总线和一般连线有何区别?

使用中应注意哪些问题?

实验一原理图的绘制

一、实验目的

(1)熟练掌握PROTEL99的基本操作。

(2)学会绘制电路原理图。

(3)掌握电路图的ERC校验、电路错误修改和网络表的生成。

二、实验内容与步骤

(1)新建文档,设置参数的基本操作。

进入ADVANCEDSCHEMATIC,新建一张原理图,并设置它的工作空间参数和文档参数。

其中,电路图大小设置为A4,横向放置,标题栏选择标准标题栏,栅格大小均选为20mil。

(2)装入元器件库。

执行相关命令,

(3)放置元器件。

按照如图1-1所示,从元器件库中放置相应的元器件到电路图中,并对元器件做移动,旋转等操作,同时进行属性设置。

各元器件的元器件标号及标称值均采用小四号宋体,完成后将文件存盘。

(4)全局修改。

利用SCH的全局修改功能,将图1-1中电阻的标号和标称值均由小四号宋体改为五号黑体,并将电阻的编号R*由大写改为小写r*,完成后将文件改名存盘。

(5)绘制电源电路图。

按照如1-1所示,绘制电源电路的原理图,并填上正确的封装,完成后将文件存盘。

(6)对完成的电路图进行ERC校验,若有错误,则加以改正,直到校验无误后,存盘

(7)对修改后的电路图进行编译,产生网络表文件,将网络表文件存盘后退出

图1-1电源电路图

三.仪器设备

计算机,打印机

四.思考题

(1)为什么要给元器件定义封装形式?

是否所有原理图中的元器件都要定义封装形式?

(2)放置元器件时系统提示没有打开元器件库,应如何解决?

(3)使用网络标号时应注意哪些问题?

(4)总线和一般连线有何区别?

使用中应注意哪些问题?

教学后记:

实验二单面板的制作

一、本次课主要内容

1.导入实验一中己完成的电源电路的原理图.设置好相关的参数,绘制好电源电路PCB图.将文件存盘退出.

2.将绘制好的PCB图打印出来贴在报告中.

3.制作电源实物

二、教学目的与要求

1.熟练掌握PCB的基本操作。

2.基本掌握PCB元器件库的编辑方法。

3.掌握单面板的制作。

三、教学重点难点

重点:

图纸参数设置;调用PCB元件;创建PCB元件库;元件布局与排列;网络走线.

难点:

元件布局与走线

注意:

单面板走线不能有交叉,布线前元件布局时尽量不能有飞线交叉

四、教学方法和手段

采用课堂讲授(大概20分钟时间),对PCB板图绘制的方法与技巧运用多媒体进行演示、并制作教学幻灯片,并制作教学幻灯片。

其余时间指导学生上机操作,并解答学生提问.

五、作业与习题布置

回答下面问题:

1.简述自动布局的步骤。

2.自动布线前,要进行哪些设置?

3.何种类型的电路,在设计印制板时要使用铺铜?

写出完整的实验报告:

要求制作直流稳压电源系统实物,能输出+5V、-5V、+12V、-12V、+3.3V

实验二单面板的制作

一、实验目的

(1)熟练掌握PCB的基本操作。

(2)基本掌握PCB元器件库的编辑方法。

(3)掌握单面板的制作。

(4)绘制出电源PCB图(单面板)

二、实验内容

(1)进入SCH,打开在实验一中己完成的电源电路的原理图(图1-1),设置好电路图中各元器件的封装,执行相关菜单命令,生成此电路图的网络表。

(2)新建一个PCB文件,打开标准元器件库,设置好工作空间参数和文档参数,其中信号层选择底层,将此文件更名为dydl.PCB保存.

(3)在禁止布线层上绘制电路版图的边框,给边框加上尺寸标注.

(4)调入电源电路的网络表,若网络表中存在错误,则加以修改,完全正确后,按下EXECUTE按钮确定.

(5)通过自动布局以及人工调整的方法,合理布局元器件,布局调整时应尽量减少飞线交叉。

(6)设置设计规则,其中,电源以及接地线要求的铜膜线宽最小为30mil,最大为40mil,其余的线宽均为10mil.

(7)执行手动布线,并参考自动布线。

(8)在PCB中,生成此电路板图的网络表,重新回到SCH中,与原理图的网络表进行比较,若发现不符,寻找原因,加以改正。

(9)进行DRC检查,生成报告文件,若有错误,则加以修改。

(10)给电路板图加上铺铜,铺铜与地相连,并且去除死铜,最后完成电源电路印制电路图,将文件存盘退出.

(11)打印电路图

三、思考题

(1)简述自动布局的步骤。

(2)自动布线前,要进行哪些设置?

(3)何种类型的电路,在设计印制板时要使用铺铜?

四、作业要求:

要求制作直流稳压电源系统实物,能输出+5V、-5V、+12V、-12V、+3.3V

要求在实物上敷铜表示出班级、姓名、学号、制作日期(没有者不计成绩)。

表1.1电路板所需要的器材

器材名称

规格

单价(元)

所需数量

总计

焊锡丝

0.8mm(50g)

1卷

松香

10g

一盒

三氯化铁(无水、粉末状的)

500克

1袋

PCB板子(双面)

200mm*150mm*1.5mm

1块

打孔针(直柄麻花钻)

0.8mm

2根

1.2mm

1根

砂纸

1张

总计

另:

微型钻台1台,电熨斗1台(可每个班共用1台)

表1.2电源元器件清单

名称

规格

数量

单价(元)

合计

变压器(中心轴头)

12V输出20w

1

六角开关

6mm*6mm

1

电解质电容

25v2200uF

2

电解质电容

25v470uF

4

瓷片电容

104

4

LM7812

TO-220

1

LM7912

TO-220

1

LM7805

TO-220

1

LM7905

TO-220

1

LM1117-3.3

TO-263

1

发光二极管

0.5mm

5

电阻

470、1k

2

电阻

300

1

单排针

1

散热片

7805用

4

散热片固定螺钉、螺帽

4

整流桥

2W10

2A/1000V

1

220V电源插头线

1米

1

总计

教学后记:

实验三有时钟使能的两位十进制计数器原理图输入设计

一、本次课主要内容

设计一个有时钟使能的两位十进制计数器,在QuartusII软件平台上绘制出完的电路原理图,并进行编译,仿真,测试。

二、教学目的与要求

1.掌握带有时钟输入的数字电路原理图输入设计方法;

2.进一步掌握时序波形的真;

3.了解VHDL初步的基本知识。

4..根据以上的实验内容写出实验报告,并将仿真波形图打印出来贴在报告中,分析实验过程中遇到的问题,总结用到的知识点

三、教学重点难点

重点:

QuartusII使用,文件命名与保存,调元件库,网络标号,总线设置,波形仿真

难点:

波形仿真,总线设置,

四、教学方法和手段

采用课堂讲授(大概20分钟时间),对QuartusII软件的使用方法运用多媒体进行演示、并制作教学幻灯片。

其余时间指导学生上机操作,并解答学生提问.

实验设备:

EDA系统箱一台,装有PROTEL软件的计算机一台,打印机一台

五、作业与习题布置

1、对仿真波形结果进行分析。

2、用VHDL编写有时钟输入的两位十进制计数器源程序。

3、写出完整的实验报告

实验三有时钟使能的两位十进制计数器原理图输入设计

一.实验目的

掌握带有时钟输入的数字电路原理图输入设计方法;

进一步掌握时序波形的真;

了解VHDL初步的基本知识。

二.实验原理与步骤

1.实验步骤见第五章第一节介绍的方法。

2.电路设计原理:

频率计设计的基本步骤与上一个实验介绍的完全一样,只是需要考虑从哪一个电路模块开始。

图3-1用74390设计一个有时钟使能的两位十进制计数器原理

图3-2调出元件74390

图3-3从Help中了解74390的详细功能

1、设计电路原理图,频率计的核心元件之一是含有时钟使能及进位扩展输出的十进制计数器。

为此这里拟用一个双十进制计数74390和其它一些辅助元件来完成。

电路原理图如图2-1所示。

图中,74390连接成两个独立的十进制计数器,待测频率信号clk通过一个与门进入74390的计数器1的时钟输入端1CLKA,与门的另一端由计数使能信号enb控制:

当enb='1'时允许计数;enb='0'时禁止计数。

计数器1的4位输出q[3]、q[2]、q[1]和q[0]并成总线表达方式即q[3..0],由图2-1左下角的OUTPUT输出端口向外输出计数值,同时由一个4输入与门和两个反相器构成进位信号进入第2个计数器的时钟输入端2CLKA。

第2个计数器的4位计数输出是q[7]、q[6]、q[5]和q[4],总线输出信号是q[7..4]。

这两个计数器的总的进位信号,即可用于扩展输出的进位信号由一个6输入与门和两个反相器产生,由cout输出。

clr是计数器的清零信号。

2、计数器电路实现,在此首先从实现图3-1所示的电路的绘制和测试开始,用鼠标双击“EnterSymbol”窗中SymbolLibraries栏的e:

\maxplus2\max2lib\mf的宏功能元件库,于是可以在SymbolFiles栏中看到绝大多数74系列的元件(图3-2)。

这些器件的详细功能及其它们的逻辑真值表可以通过查阅“Help”选项来获得。

为了查阅74390的功能,可如图3-3所示,在Help菜单中选Old-StyleMacrofunctions项,然后选Counters项。

图3-4两位十进制计数器工作波形

向原理图编辑窗中调入宏功能元件如图3-2所示,直接在上端的SymbolName栏中键入器件的名称,如74390等,然后点击OK键即可。

如果要了解74390内部的情况,可以用鼠标在其上双击。

最后根据图2-1在原理图编辑窗中完成该电路的全部绘制。

绘制过程中应特别注意图形设计规则中信号标号和总线的表达方式:

若将一根细线变成以粗线显示的总线,可以先将其点击使其变成红色,再选Option选项中的LineStyle;若在某线上加信号标号,也应该在该线某处点击使其变成红色,然后键入标号名称,标有相同标号的线段可视作连接线段,但可不必直接连接。

对于以标号方式进行总线连接可以如图3-1那样。

例如一根8位的总线bus1(7..0)欲与另3根分别为1、3、4位的连线相接,它们的标号可分别表示为bus1(0),bus1(3..1),bus1(7..4)。

3、波形仿真,按照第一章介绍的流程能够很容易地得到图2-1电路的仿真波形(图3-4)。

由波形图3-4可见,图2-1电路的功能完全符合原设计要求:

当clk输入时钟信号时,clr信号具有清0功能,当enb为高电平时允许计数,低电平时禁止计数;当低4位计数器计到9的向高4位计数器进位,另外由于图3-4中没有显示高4位计数器计到9,故看不到count的进位信号。

如果本设计电路的存盘文件名为conter8.gdf,则按照步骤5的第9段介绍的方法,将此项设计包装成一个元件存入库中以备后用,该电路对应的元件名是conter8。

三、实验注意事项

1、输入文件名不能用汉字或关键字、非法字符;

2、注意文件在编译连接时的路径;

3.注意引脚分配与对应的FPGA芯片相匹配;

4.注意信号标号与总路线的表达方式。

四、实验设备

EDA系统一套,计算机一台,打印机一台

五、实验思考

1.用VHDL编写有时钟输入的两位十进制计数器源程序。

2.对仿真波形结果进行分析。

教学后记:

实验四7段数码显示译码器的设计

一、本次课主要内容

设计一个7段数码显示译码器,能够显示0-9,A-F数字。

1.编写7段数码显示译码器的VHDL源程序;

2.在QuartusII上进行编译、综合、适配、仿真测试,引脚锁定、下载测试。

二、教学目的与要求

1.学习7段数码显示译码器的设计方法;

2.掌握多层次的VHDL程序设计方法。

三、教学重点难点

重点:

QuartusII使用,文件命名与保存,波形仿真,配置器件的选择与设置

难点:

配置器件的选择与设置,波形仿真,。

四、教学方法和手段

采用课堂讲授(大概20分钟时间),对QUARTUSII软件的使用方法运用多媒体进行演示、并制作教学幻灯片。

其余时间指导学生上机操作,并解答学生提问.

五、作业与习题布置

写出完整的设计性实验报告。

实验报告内容包括:

程序设计、软件编译、仿真分析、硬件测试和详细实验过程;硬件测试分析报告、仿真波形图及其分析报告。

讨论语句WHENOTHERS=>NULL的作用。

对于不同的VHDL综合器,此句是否具有相同含义和功能?

实验四7段数码显示译码器的设计

一、设计目的

1.学习7段数码显示译码器的设计方法;

2.掌握多层次的VHDL程序设计方法。

二、设计要求

1.编写7段数码显示译码器的VHDL源程序;

2.在QuartusII上进行编译、综合、适配、引脚锁定、下载测试;

3.进行仿真波形的测试;

4.写出设计性实验报告。

三、设计原理说明

1、实验原理说明:

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA或CPLD中实现。

本项实验很容易实现这一目的。

例6-21作为7段BCD码译码器的设计,输出信号LED7S的7位分别接如图6-21数码管的7个段,高位在左,低位在右。

例如当LED7S输出为"1101101"时,数码管的7个段:

g、f、e、d、c、b、a分别接1、1、0、1、1、0、1,接有高电平的段发亮,于是数码管显示“5”。

2、引脚锁定以及硬件下载测试提示:

建议选实验电路模式6,用数码8显示译码输出(PIO46--PIO40),键8、键7、键6、键5四位控制输入,硬件验证译码器的工作性能。

四、实验设备

EDA系统一套,计算机一台,打印机一台

五、实验报告要求

根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试和详细实验过程;设计原程序,程序分析报告、仿真波形图及其分析报告。

六、实验思考和总结

1.讨论语句WHENOTHERS=>NULL的作用。

对于不同的VHDL综合器,此句是否具有相同含义和功能?

2.用VHDL例化语句(参考实验2)按图3-25的方式,以本章第一节实验三和本节实验一为底层元件,完成顶层文件设计,并重复以上实验过程。

注意图3-25中的tmp是4位总线,led是7位总线。

对于引脚锁定和实验,建议仍选实验电路模式6,用数码8显示译码输出,用键3作为时钟输入(每按2次键为1个时钟脉冲),或直接时钟信号clock0。

图4-1计数器和译码器连接电路的顶层文件原理图

3.对实验思考2进行分析和总结。

教学后记:

实验五数控分频器的设计

一、本次课主要内容

设计一个能实现数控分频的分频器。

1.编写数控分频器的VHDL源程序;

2.在QuartusII上进行编译、综合、适配、引脚锁定、下载测试;

3.输入不同的CLK和预置值进行仿真波形的测试;

二、教学目的与要求

1.学习数控分频器的设计、分析、测试方法;

2.牢固掌握用VHDL语言编写程序的方法和技巧。

3.频率可选65536Hz或更高(确保分频后落在音频范围);

三、教学重点难点

重点:

实体与结构体的关键词及进程的使用,分频的原理,波形仿真,配置器件的选择与设置,程序设计中进程的作用

难点:

配置器件的选择与设置,分频器的原理。

四、教学方法和手段

采用课堂讲授(大概20分钟时间),对分频器的原理及VHDL程序编写方法运用多媒体进行演示、并制作教学幻灯片。

其余时间指导学生上机操作,并解答学生提问.

五、作业与习题布置

对所完成的实验进行总结和分析并写出完整的设计性实验报告。

实验报告内容包括:

程序设计、软件编译、仿真分析、硬件测试和详细实验过程.

实验五数控分频器的设计

一、设计目的

1.学习数控分频器的设计、分析、测试方法;

2.牢固掌握用VHDL语言编写程序的方法和技巧。

二、设计要求

1、编写数控分频器的VHDL源程序;

2、在QuartusII上进行编译、综合、适配、引脚锁定、下载测试;

3、输入不同的CLK和预置值进行仿真波形的测试;

4、写出设计性实验报告。

三、设计原理说明

1.实验原理说明:

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,可用计数值可并行预置的加法计数器设计完成,方法是将计数溢出位与预置数加载输入信号相接即可。

2.引脚锁定及下载测试提示:

如果目标器件是EPF10K10,建议选实验电路模式1,键2/键1(PIO7-PIO0)负责输入8位预置数D;CLK由clock0输入,频率可选65536Hz或更高(确保分频后落在音频范围);输出FOUT接扬声器(SPKER:

PIN3)。

编译下载后进行硬件测试:

改变键2/键1的输入值,可听到不同音调的声音。

四、实验设备

EDA系统一套,计算机一台,打印机一台

五、实验报告要求

根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试和详细实验过程;设计原程序,程序分析报告、仿真波形图及其项目分析。

六、实验思考和总结

1.阐述程序设计中进程的作用。

2.对所完成的实验进行总结和分析。

3.写出完成时钟上升沿的语句。

附:

数控分频器的设计程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYPULSEIS

PORT(CLK:

INSTD_LOGIC;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

FOUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREoneOFPULSEIS

SIGNALFULL:

STD_LOGIC;

BEGIN

P_REG:

PROCESS(CLK)

VARIABLECNT8:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFCNT8="11111111"THEN

CNT8:

=D;--当CNT8计数计满时,输入数据D被同步预置给计数器CNT8

FULL<='1';--同时使溢出标志信号FULL输出为高电平

ELSECNT8:

=CNT8+1;--否则继续作加1计数

FULL<='0';--且输出溢出标志信号FULL为低电平

ENDIF;

ENDIF;

ENDPROCESSP_REG;

P_DIV:

PROCESS(FULL)

VARIABLECNT2:

STD_LOGIC;

BEGIN

IFFULL'EVENTANDFULL='1'

THENCNT2:

=NOTCNT2;--如果溢出标志信号

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 技术 实验 教案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《C12343098汽轮机操作规程》要点.docx

《C12343098汽轮机操作规程》要点.docx